TC1796

Peripheral Units (Vol. 2 of 2)

Micro Second Channel (MSC)

User’s Manual 21-55 V2.0, 2007-07

MSC, V2.0

Note: When the ISC register is written with both bits set (clear and set bit) for a specific

interrupt flag, the clear operation takes place and the set operation is ignored.

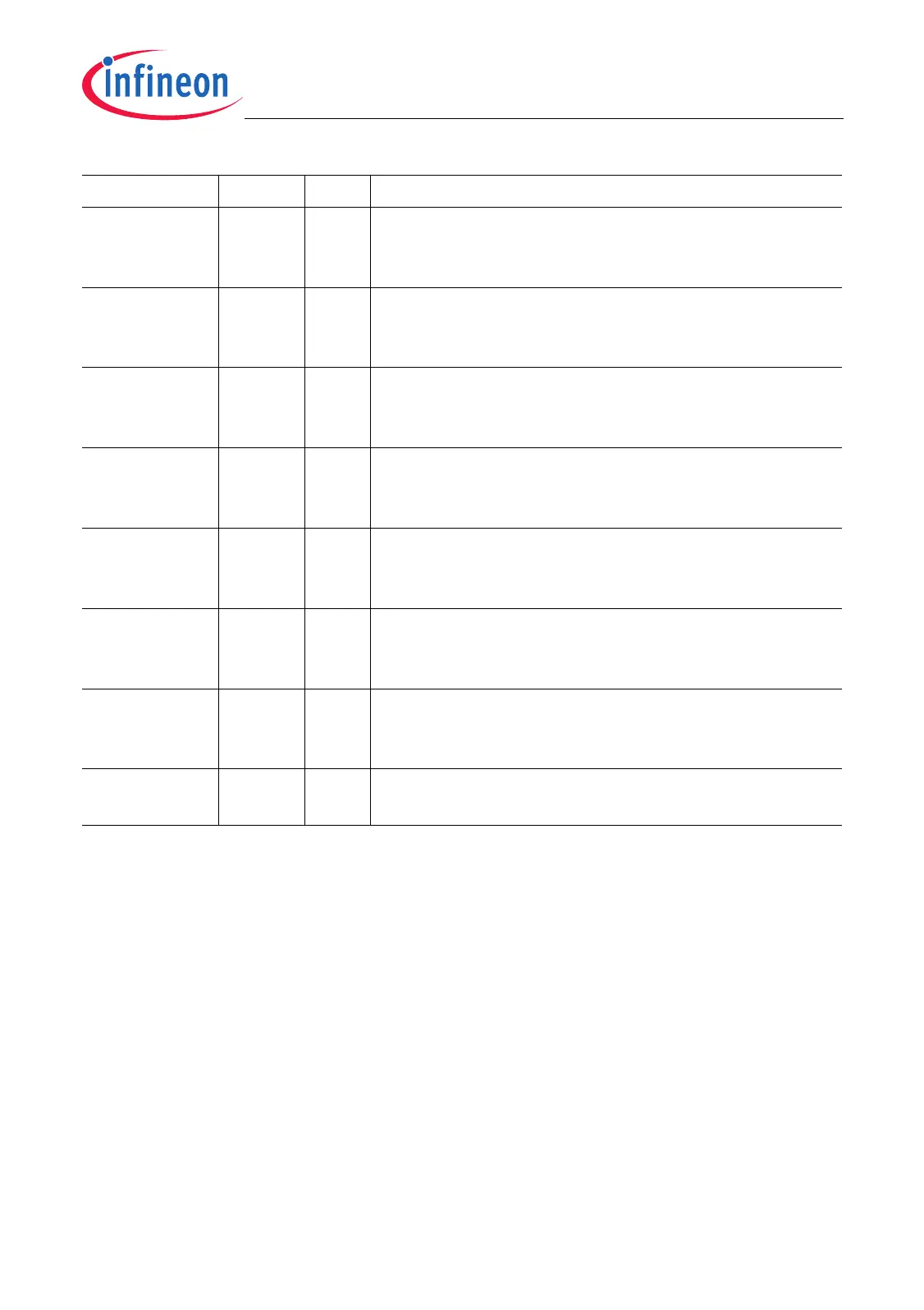

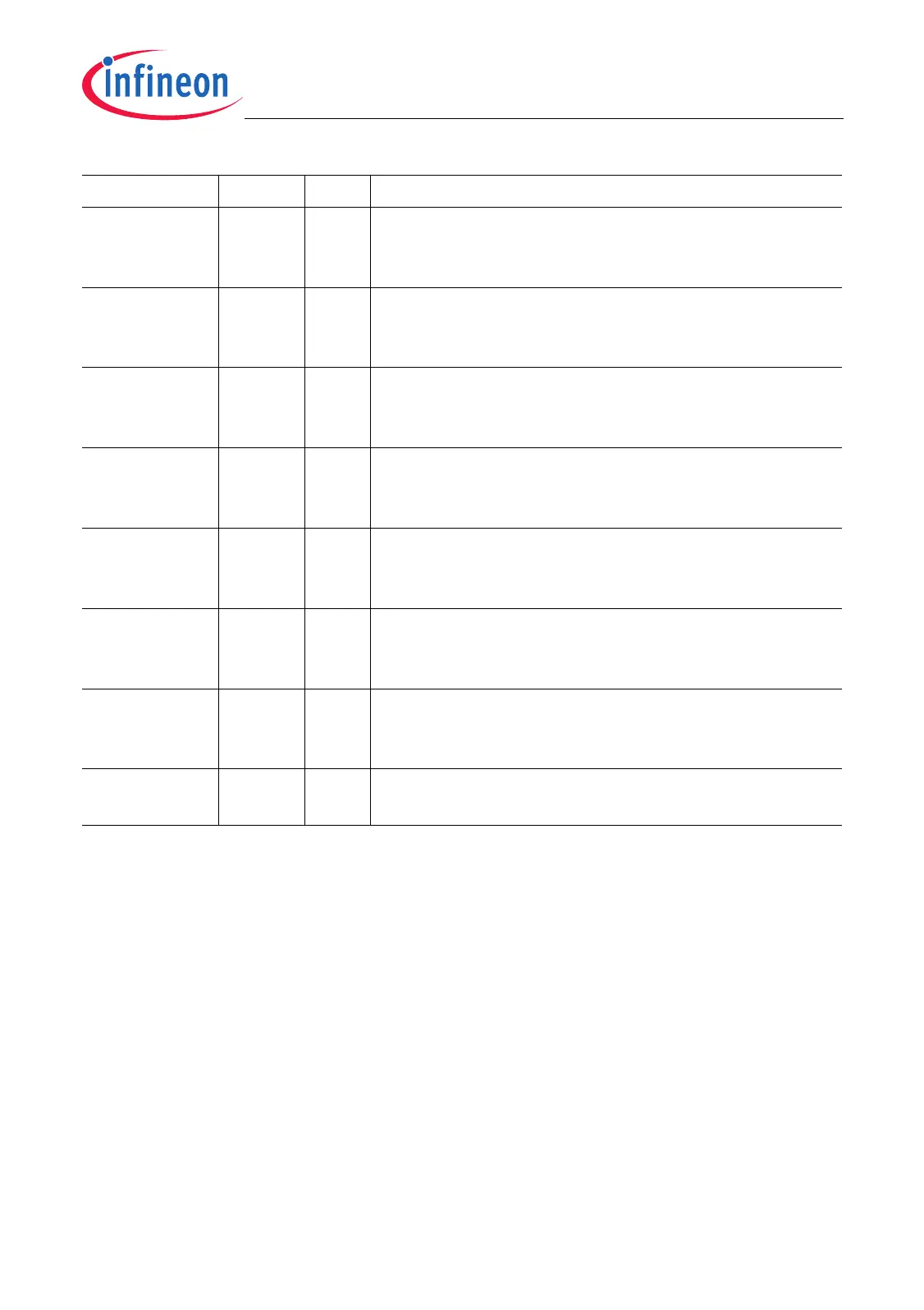

SDEDI 16 w Set DEDI Flag

0

B

No operation.

1

B

Bit ISR.DEDI is set.

SDECI 17 w Set DECI Flag

0

B

No operation.

1

B

Bit ISR.DECI is set.

SDTFI 18 w Set DTFI Flag

0

B

No operation.

1

B

Bit ISR.DTFI is set.

SURDI 19 w Set URDI Flag

0

B

No operation.

1

B

Bit ISR.URDI is set.

SDP 20 w Set DP Bit

0

B

No effect.

1

B

Bit DSC.DP is set.

SCP 21 w Set CP Flag

0

B

No operation.

1

B

Bit DSC.CP is set.

SDDIS 22 w Set DSDIS Flag

0

B

No operation.

1

B

Bit DSC.DSDIS is set.

0 [15:7],

[31:23]

r Reserved

Read as 0; should be written with 0.

Field Bits Type Description

Loading...

Loading...