TC1796

Peripheral Units (Vol. 2 of 2)

Controller Area Network (MultiCAN) Controller

User’s Manual 22-195 V2.0, 2007-07

MultiCAN, V2.0

The bits in the scheduler instruction status register monitor the information during and

after the instruction collection phase of the scheduler. These values will become valid

when the next time mark is reached.

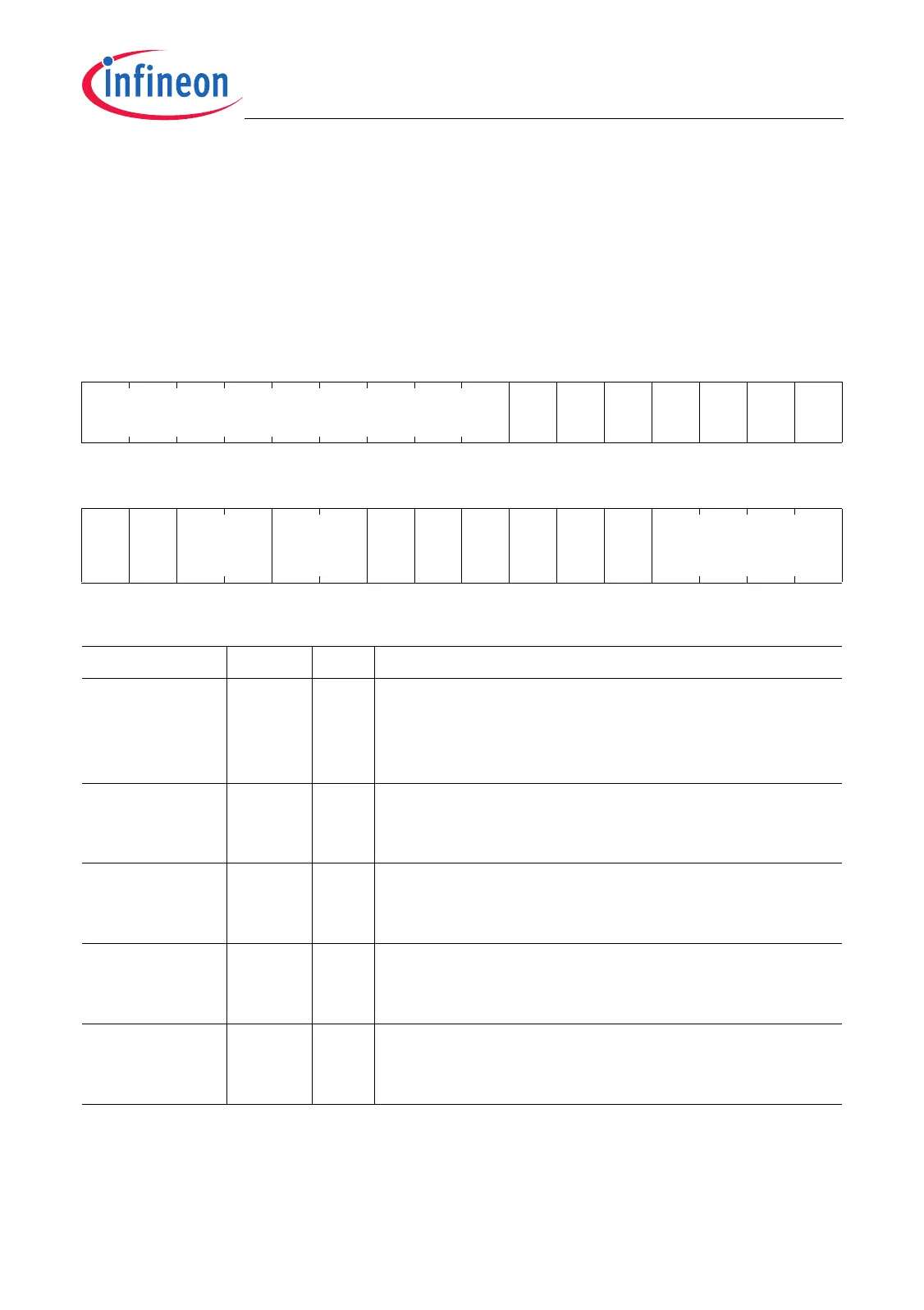

SISR

Scheduler Instruction Status Register

(2F8

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

BCE

V

RME

V

TME

V

ARB

V

ICE

V

TCE

V

RCE

V

r rhrhrhrhrhrhrh

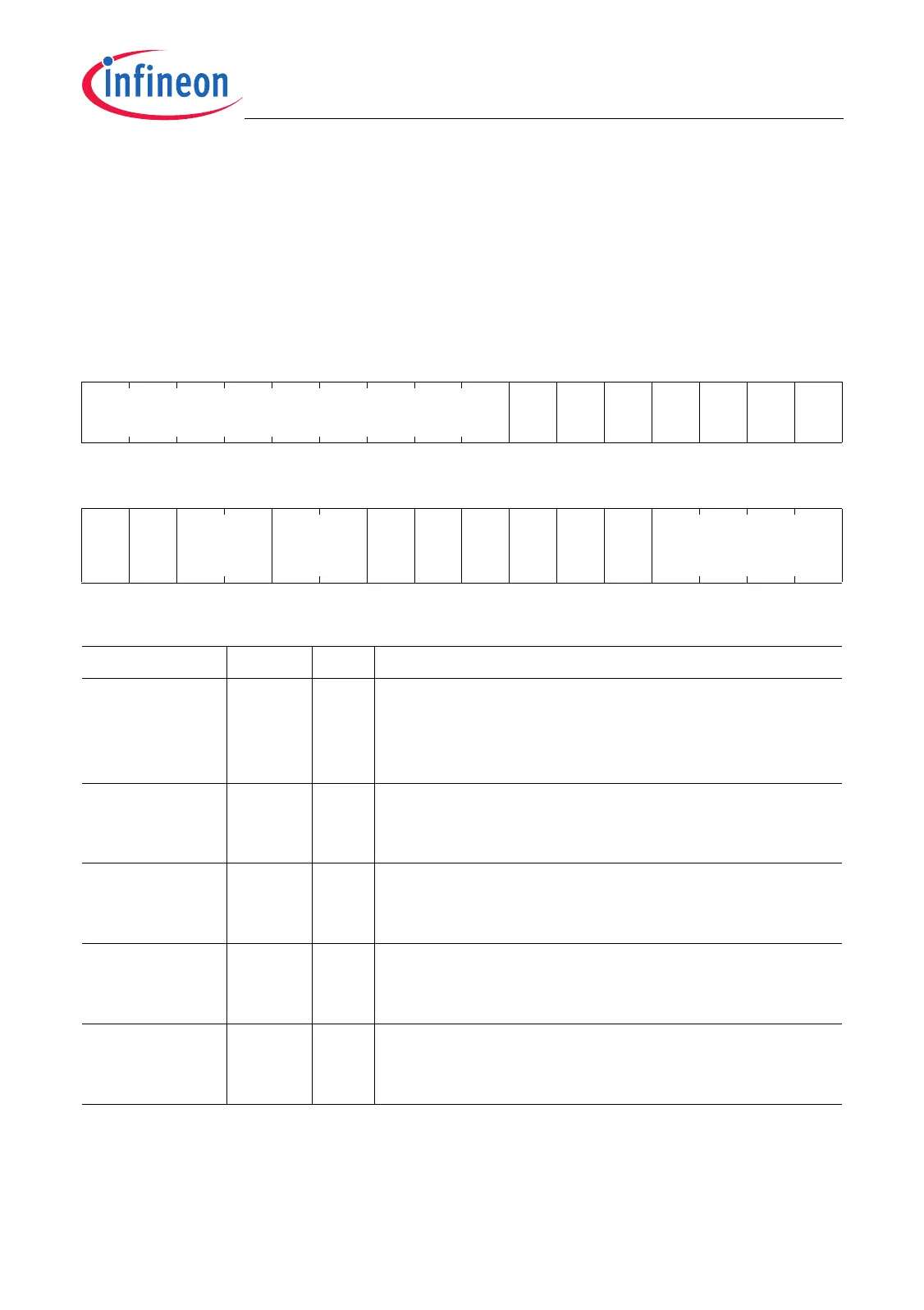

1514131211109876543210

ICF GM ARBM ALTMSG

TR

EN

CH

EN

IEN

REC

F1

IEN

REC

F0

IEN

TRA

F1

IEN

TRA

F0

INP

rh rh rh rh rh rh rh rh rh rh rh

Field Bits Type Description

INP [3:0] rh Interrupt Node Pointer

This bit field indicates the collected INP information.

This value is taken into account only when at least

one of the four interrupt requests is enabled.

IENTRAF0 4rhInterrupt Enable if TRAF = 0

This bit field indicates the collected IENTRAF0

information.

IENTRAF1 5rhInterrupt Enable if TRAF = 1

This bit field indicates the collected IENTRAF1

information.

IENRECF0 6rhInterrupt Enable if RECF = 0

This bit field indicates the collected IENRECF0

information.

IENRECF1 7rhInterrupt Enable if RECF = 1

This bit field indicates the collected IENRECF1

information.

Loading...

Loading...