TC1796

Peripheral Units (Vol. 2 of 2)

Micro Link Interface (MLI)

User’s Manual 23-107 V2.0, 2007-07

MLI, V2.0

The Transmitter Interrupt Status Register TISR contains all MLI event (or interrupt) flags

of the MLI transmitter. These flags can be cleared by software when writing the

appropriate bits in the TIER register; they are not cleared by hardware.

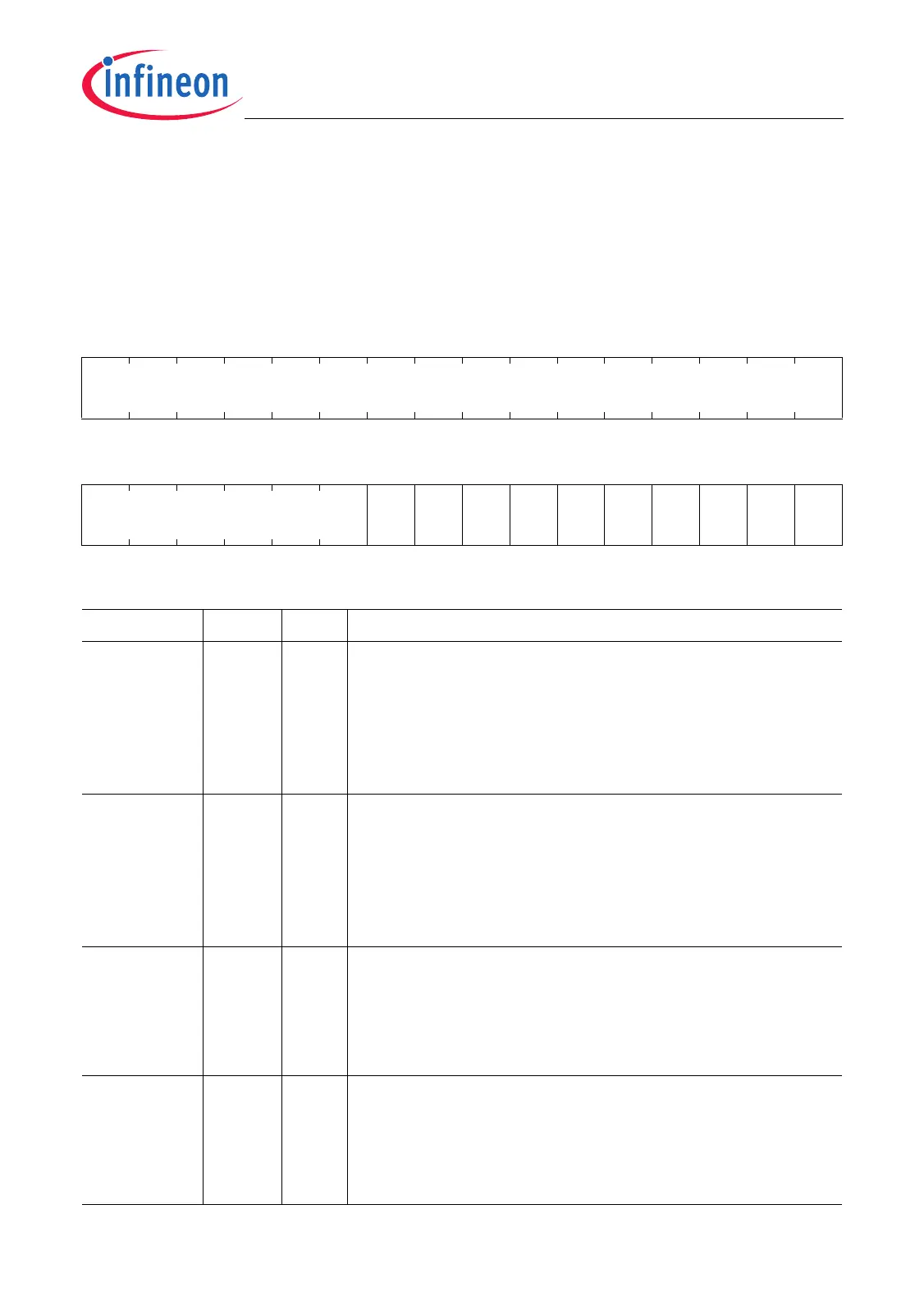

TISR

Transmitter Interrupt Status Register (9C

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

0

TE

I

PE

I

CFS

I3

CFS

I2

CFS

I1

CFS

I0

NFS

I3

NFS

I2

NFS

I1

NFS

I0

r rhrhrhrhrhrhrhrhrhrh

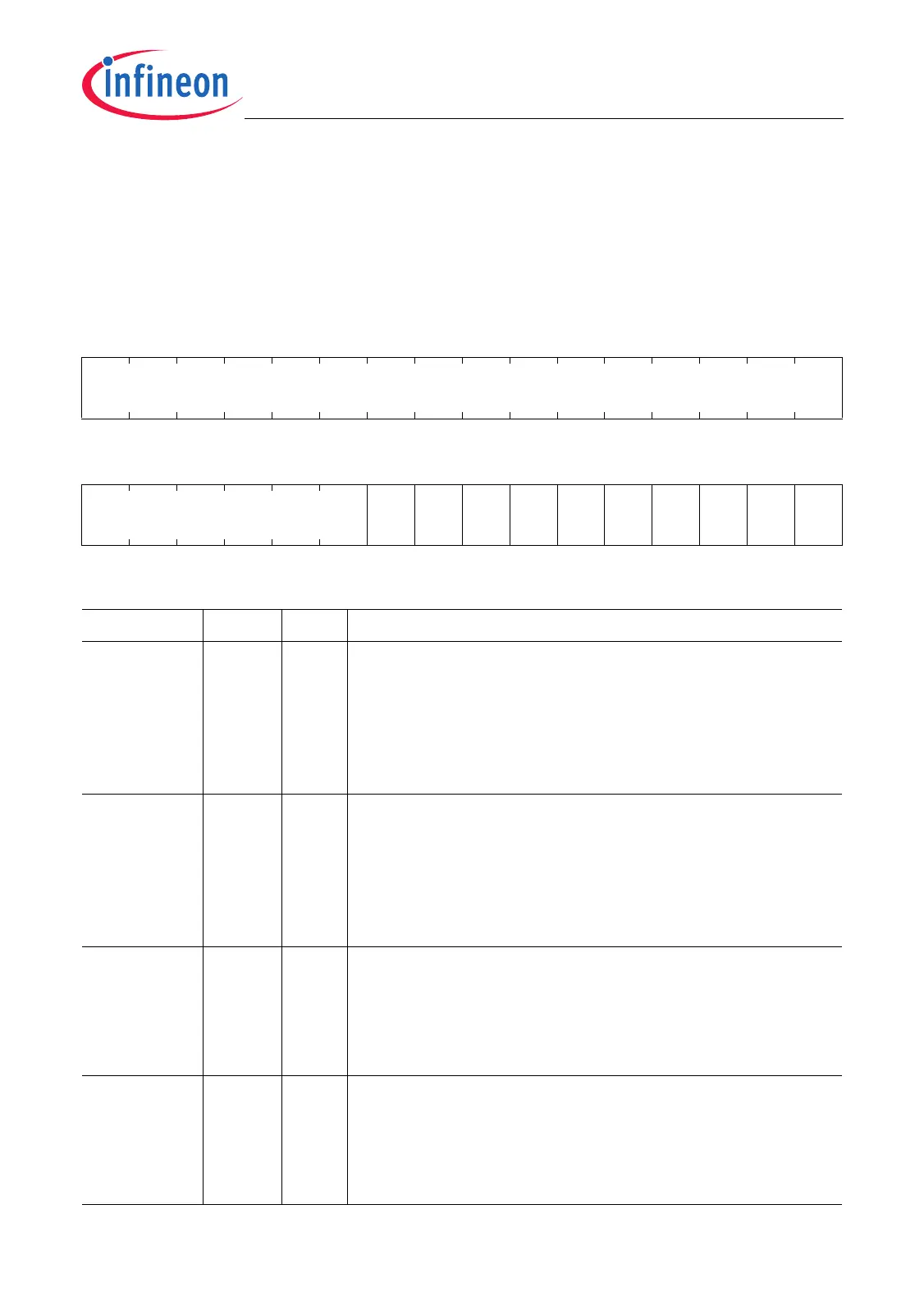

Field Bits Type Description

NFSIx

(x = 0-3)

xrhNormal Frame Sent in Pipe x Flag

0

B

A Normal Frame has not yet been sent.

1

B

A Write or Read Frame has been correctly sent

and acknowledged for pipe x.

The service request output that can be activated by

NFSIx is defined by TINPR.NFSIPx.

CFSIx

(x = 0-3)

4 + x rh Command Frame Sent in Pipe x Flag

0

B

A Command Frame has not yet been sent.

1

B

A Command Frame has been correctly sent and

acknowledged for pipe x.

The service request output that can be activated by

CFSIx is defined by TINPR.CFSIP.

PEI 8rhParity Error Flag

0

B

A parity error event has not yet been detected.

1

B

A parity error event has been detected.

The service request output that can be activated by PEI

is defined by TINPR.PTEIP.

TEI 9rhTime-Out Error Flag

0

B

A time-out error event has not yet been detected.

1

B

A time-out error event has been detected.

The service request output that can be activated by TEI

is defined by TINPR.PTEIP.

Loading...

Loading...