TC1796

Peripheral Units (Vol. 2 of 2)

Micro Link Interface (MLI)

User’s Manual 23-108 V2.0, 2007-07

MLI, V2.0

The Transmitter Interrupt Node Pointer Register TINPR contains the node pointers for

the MLI transmitter events.

0 [31:10] r Reserved

Read as 0.

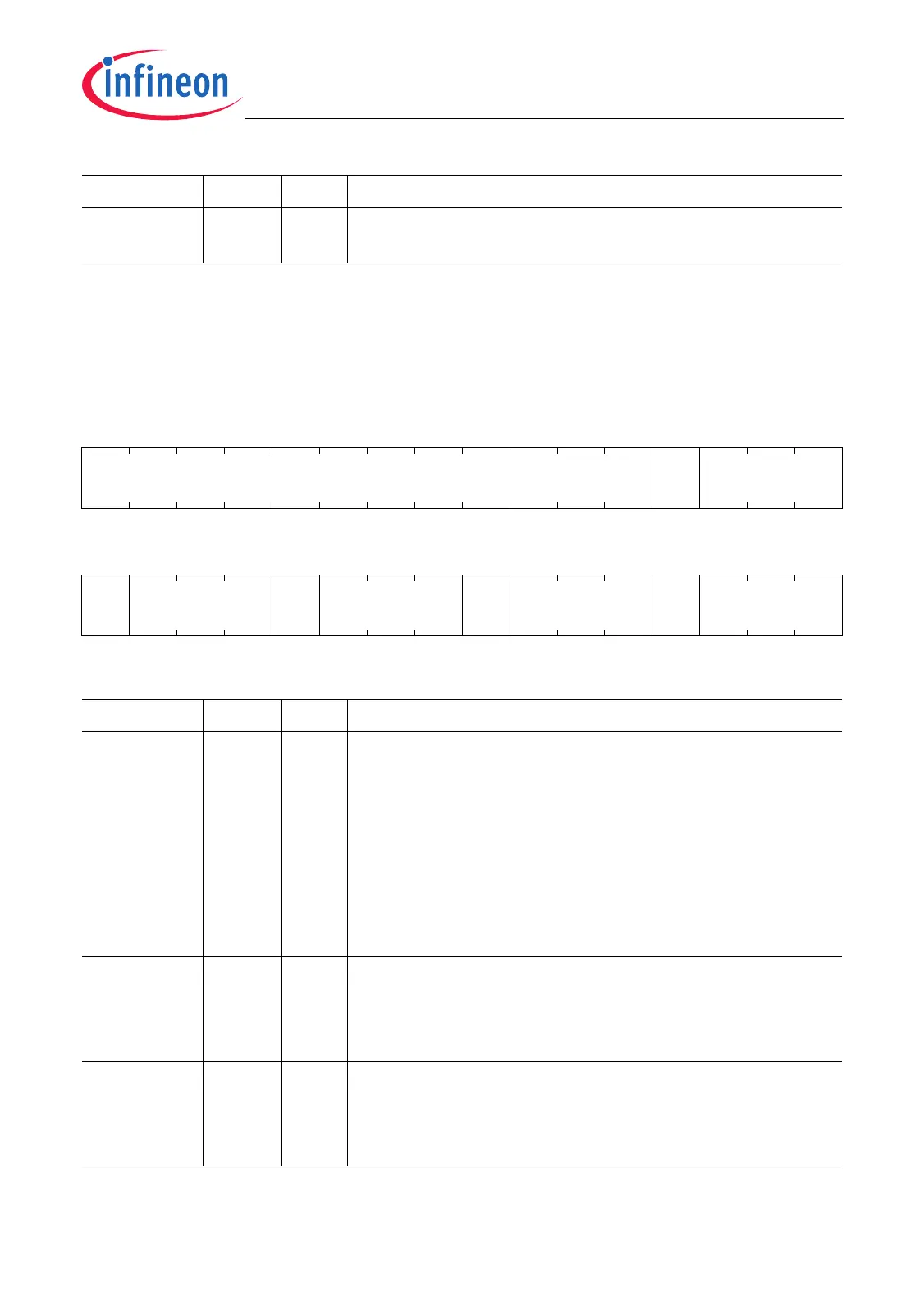

TINPR

Transmitter Interrupt Node Pointer Register (A0

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0 PTEIP 0 CFSIP

rrwrrw

1514131211109876543210

0NFSIP30NFSIP20NFSIP10NFSIP0

rrwrrwrrwrrw

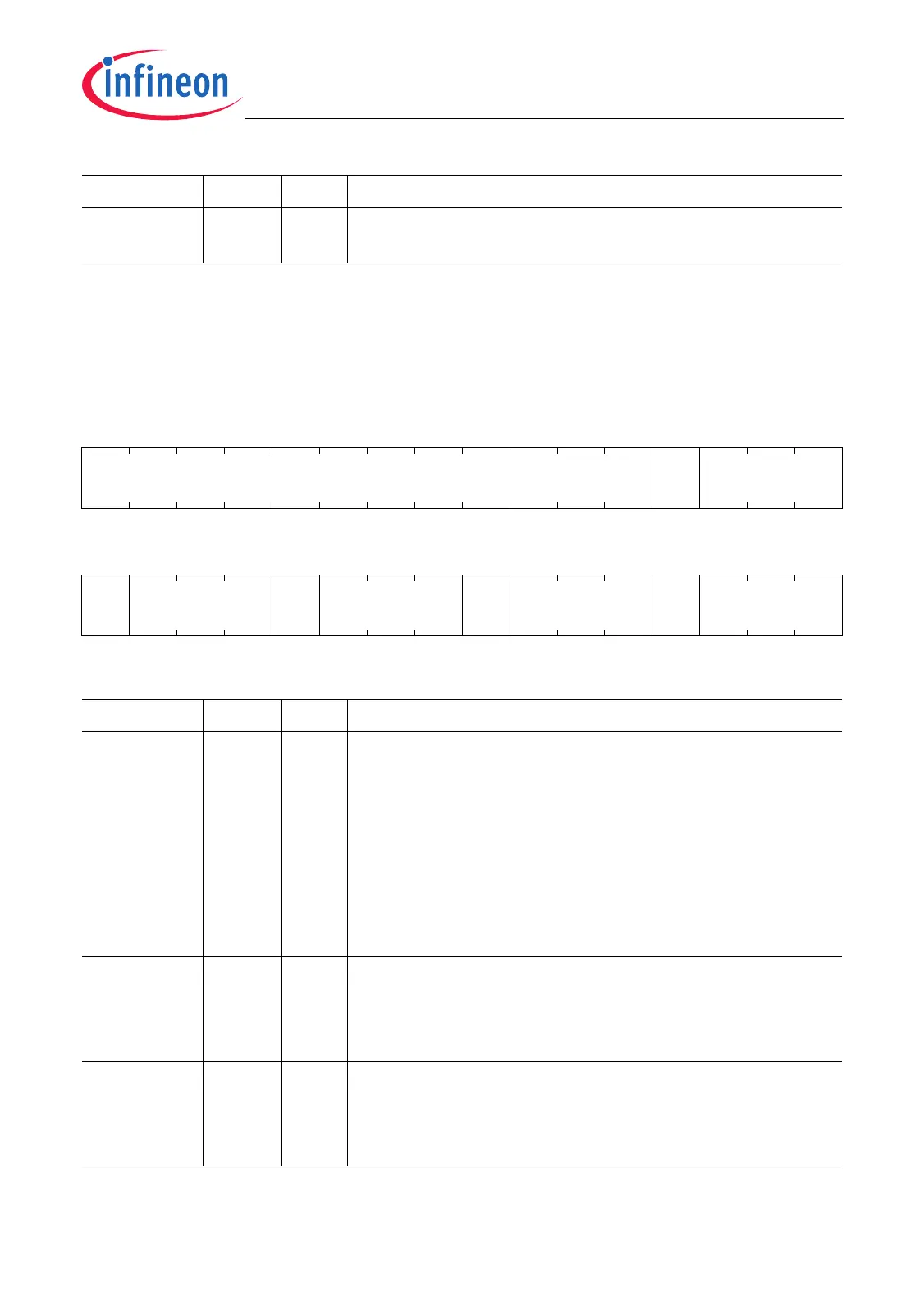

Field Bits Type Description

NFSIP0 [2:0] rw Normal Frame Sent in Pipe 0 Interrupt Pointer

This bit field determines which service request output

SRx becomes active when a Normal Frame sent in

pipe 0 event occurs (if enabled).

000

B

The service request output SR0 is selected.

001

B

The service request output SR1 is selected.

…

B

…

110

B

The service request output SR6 is selected.

111

B

The service request output SR7 is selected.

NFSIP1 [6:4] rw Normal Frame Sent in Pipe 1 Interrupt Pointer

This bit field determines which service request output

SRx becomes active when a Normal Frame sent in

pipe 1 event occurs (if enabled). Coding see NFSIP0.

NFSIP2 [10:8] rw Normal Frame Sent in Pipe 2 Interrupt Pointer

This bit field determines which service request output

SRx becomes active when a Normal Frame sent in

pipe 2 event occurs (if enabled). Coding see NFSIP0.

Field Bits Type Description

Loading...

Loading...