TC1796

Peripheral Units (Vol. 2 of 2)

General Purpose Timer Array (GPTA)

User’s Manual 24-32 V2.0, 2007-07

GPTA, V2.0

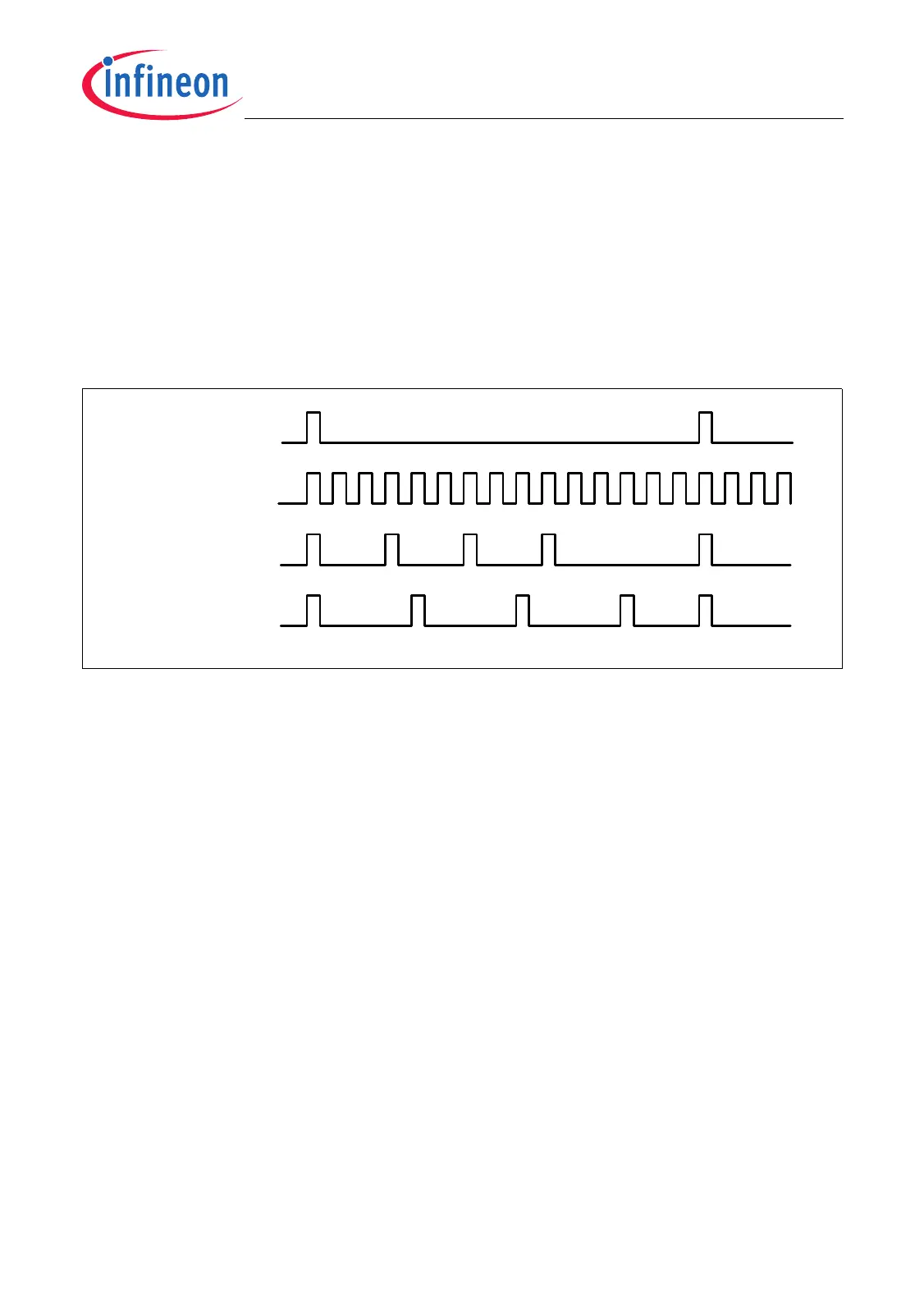

This type of PLL implementation presents a valuable advantage compared to classic

PLL implementation. Indeed, the generated microticks are equally distributed. The

division reminder is distributed to several clocks instead of adding this reminder to the

last pulse clock of the period.

Figure 24-21 illustrates this advantage. Considering a period of 15 clock pulses to be

divided by a factor of 4, it gives a result of 3 with a reminder equal to 3. The reload value

is calculated to 0B

H

(11 = 15 - 4). The number of output pulses is equal to 4 and its

2-complement representation (FFFC

H

) is written into the step register.

Figure 24-21 Advantage of the GPTA PLL

Input Signal Acceleration and Deceleration

The consequence of an input signal acceleration or deceleration can be compensated

either automatically or by an external software routine. It detects an input signal’s period

length variation by comparing the current period length (measured in the associated

DCM cell) with the expected period length used as calculation base for the PLLREV

register contents.

• Compensation of input signal deceleration

– Compensation by PLL Automatic End Mode

If Automatic End Mode is enabled (PLLCTR.AEN = 1), the PLL stops at the

calculated end of the current input signal period. Due to the deceleration, the rising

edge of the following input signal period is delayed, starting the next PLL operation

later than expected. A gap occurs between the last output pulse of the current input

signal period and the first pulse of the following one (see Figure 24-22).

– Compensation by Software

After disabling the Automatic End Mode (PLLCTR.AEN = 0), the PLL generates

output pulses without synchronization to an input signal edge. In case of a

deceleration, more output pulses than calculated are generated during one input

signal period. Several algorithms can be implemented to compensate the surplus

of generated output pulses:

MCT05930_mod

PLL Output of

a Conventional PLL

PLL Output of

the GPTA PLL

PLL Input Signal

333 6

3444

GPTA

Loading...

Loading...