TC1796

Peripheral Units (Vol. 2 of 2)

Analog-to-Digital Converter (ADC)

User’s Manual 25-82 V2.0, 2007-07

ADC, V2.0

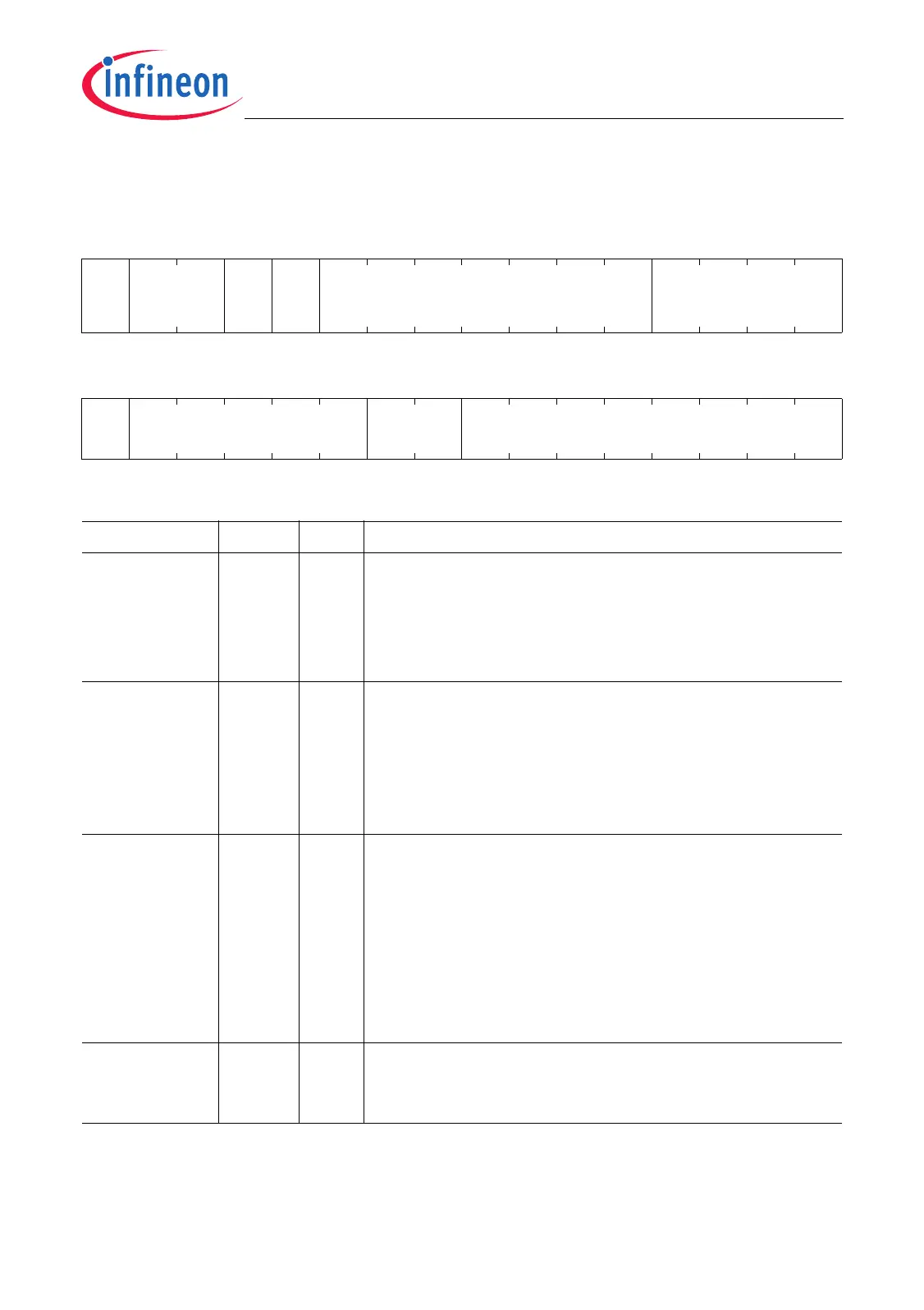

CON

Converter Control Register (120

H

) Reset Value: 0000 0001

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

SR

TE

ST

0CPR

PC

DIS

0 QWLP

rw r rw rw r rw

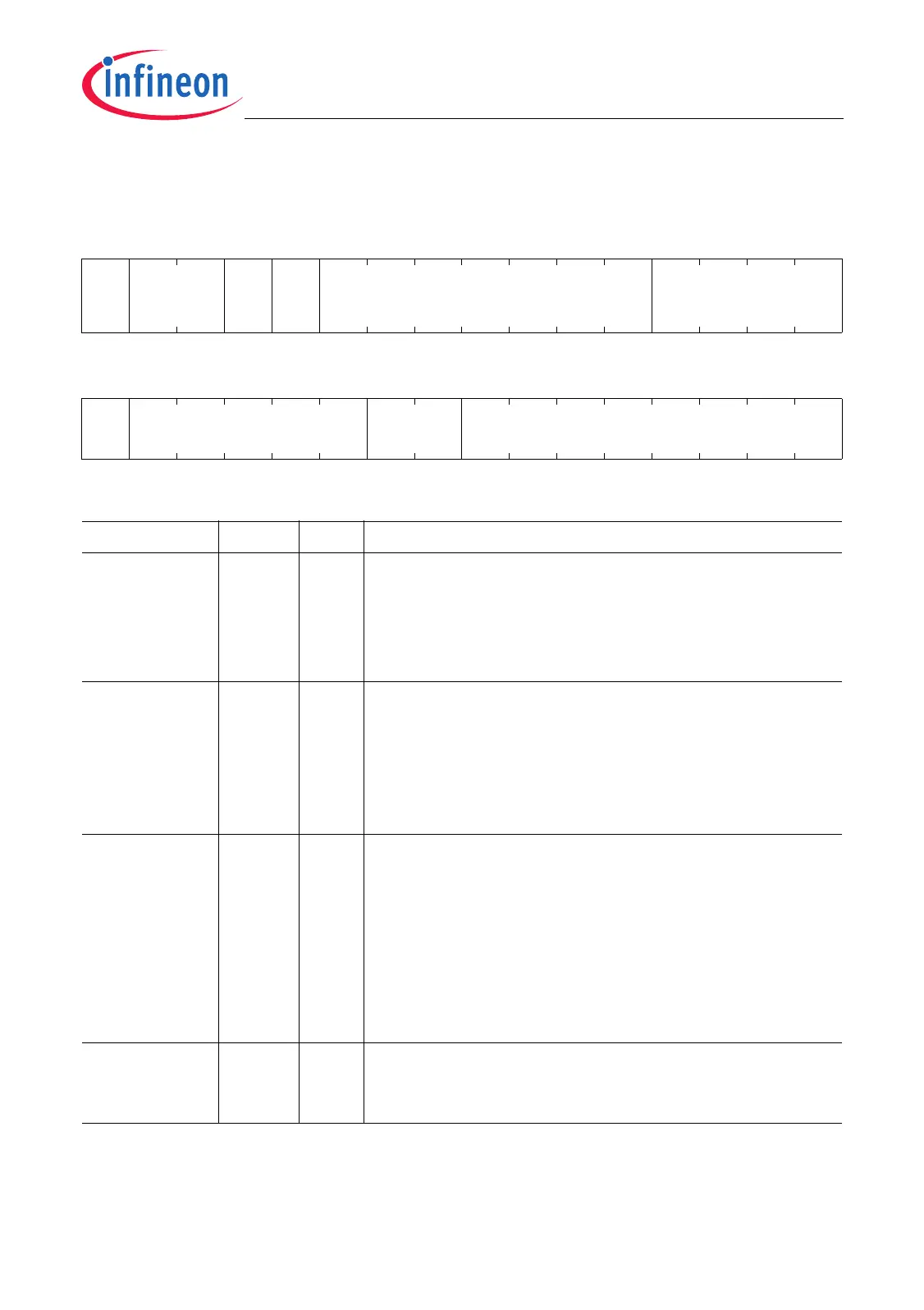

1514131211109876543210

QEN 0 SCNM CTC

rh r rw rw

Field Bits Type Description

CTC [7:0] rw Conversion Time Control

This bit determines the period of the ADC basic

operating clock f

BC

. Any modification of this bit field is

taken into account after the currently performed

conversion is finished.

SCNM [9:8] rw Auto-Scan Mode

This bit enables the auto-scan mode.

00

B

Auto-scan mode disabled

01

B

Auto-scan single sequence mode enabled

10

B

Auto-scan continuous sequence mode enabled

11

B

Reserved

QEN 15 rh Queue Enable

This bit specifies if queue controlled conversions are

enabled/disabled and queue based conversion

requests are generated.

0

B

Queue is disabled

1

B

Queue is enabled

Note: The queue load is not affected by a queue

disable condition.

QWLP [19:16] rw Queue Warning Limit Pointer

The value of the QWLP specifies the queue element

to be watched.

Loading...

Loading...