TC1796

Peripheral Units (Vol. 2 of 2)

Fast Analog-to-Digital Converter (FADC)

User’s Manual 26-33 V2.0, 2007-07

FADC, V2.0

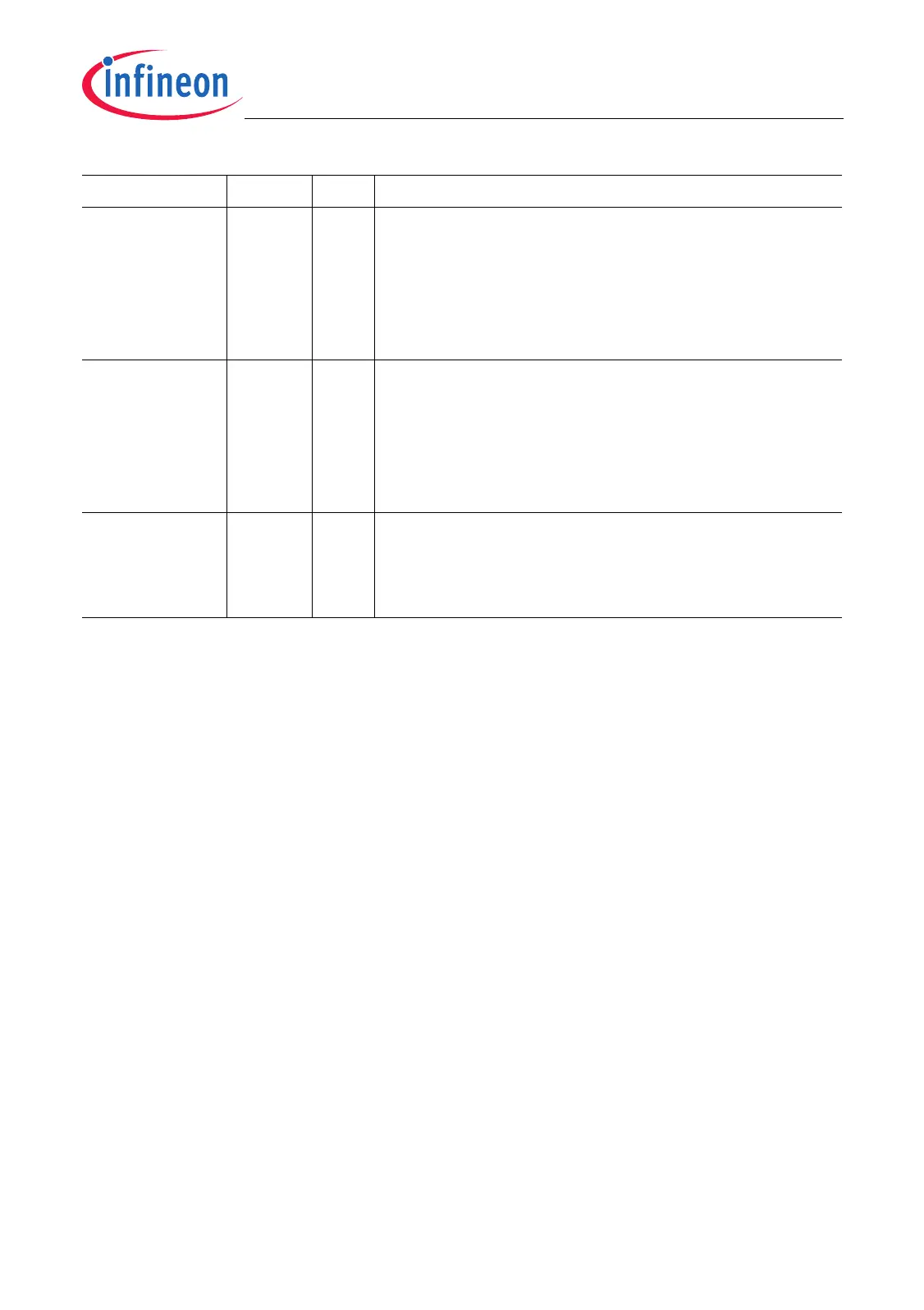

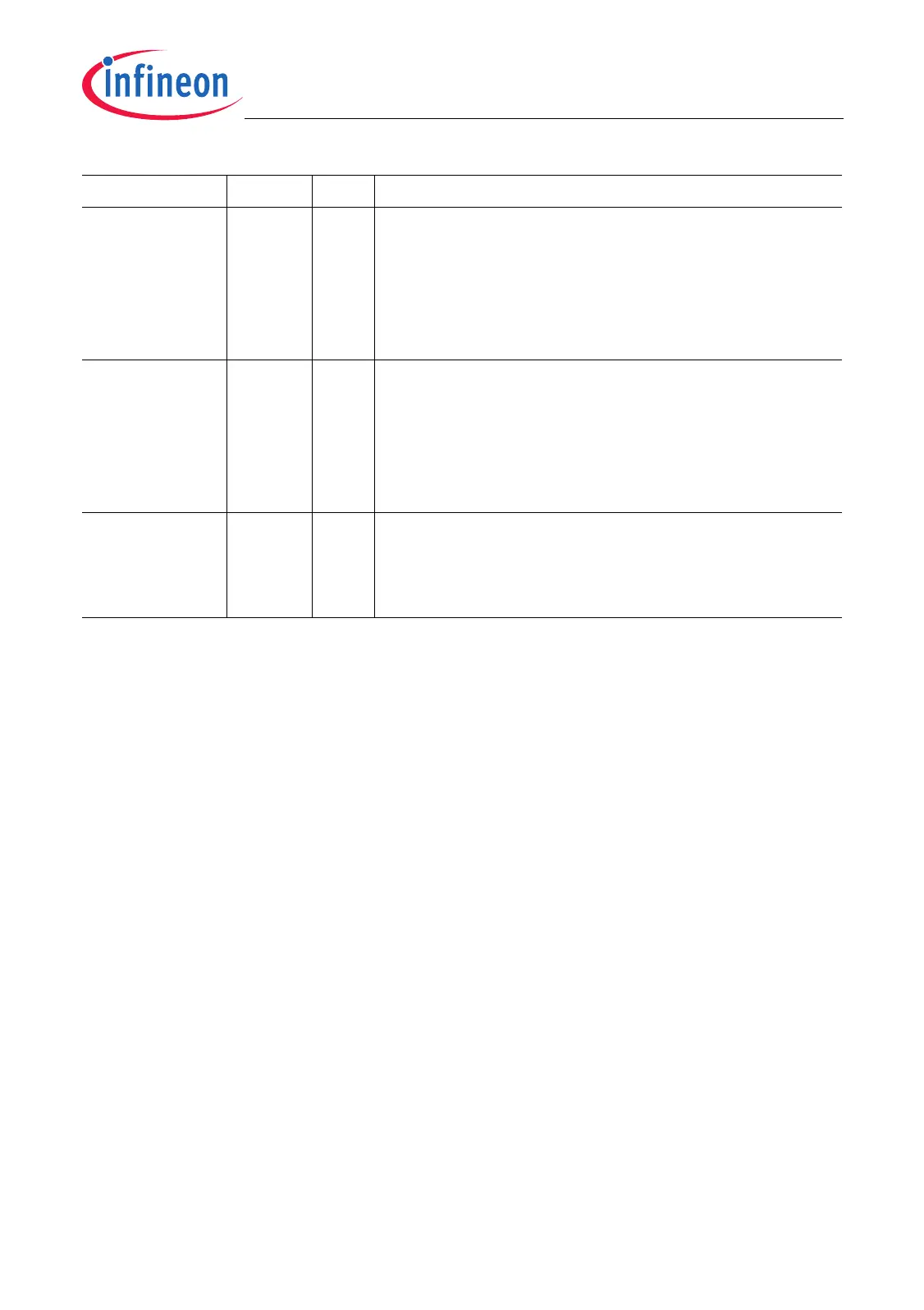

SIRQx

(x = 0-3)

24 + x w Set Interrupt Request Flag

This bit allows bit CRSR.IRQx to be set by software

(if bit RIRQx is written simultaneously with 0).

0

B

No operation

1

B

Bit CRSR.IRQx is set. An interrupt is

generated if CFGRx.IEN = 1.

SIRQFn

(n = 0-1)

28 + n w Set Interrupt Request Flag for Filter n

This bit allows bit CRSR.IRQFn to be set by software

(if bit RIRQFn is written simultaneously with 0).

0

B

No operation

1

B

Bit CRSR.IRQFn is set. An interrupt is

generated if FCRn.IEN = 1.

0 [7:4],

[15:12],

[23:22],

[31:30]

r Reserved

Read as 0; should be written with 0.

Field Bits Type Description

Loading...

Loading...