TC1796

Peripheral Units (Vol. 2 of 2)

Fast Analog-to-Digital Converter (FADC)

User’s Manual 26-52 V2.0, 2007-07

FADC, V2.0

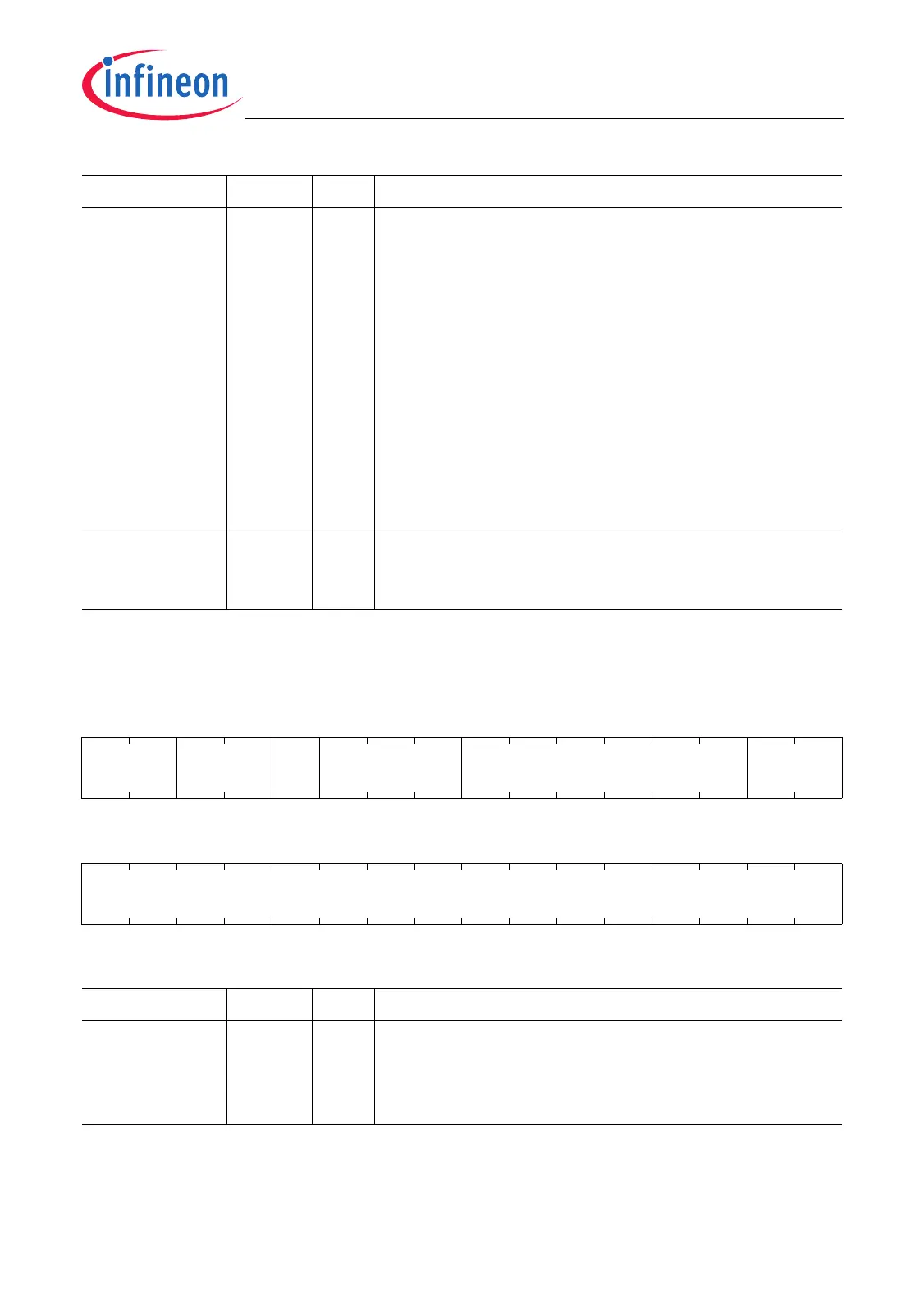

MAVS [29:28] rh Moving Average State

This bit field indicates how many intermediate

register transfers remain to be executed for the

generation of the next final result.

MAVS = 0 indicates the end of a filter calculation

operation. Since the filter calculation is executed

very fast in comparison to a conversion, MAVS > 0

can be interpreted only as a kind of calculation busy

flag. Therefore, it is recommended to read a valid

filter result from register FRRn only when the

corresponding interrupt request flag CRSR.IRQFn is

set.

MAVS is cleared when writing GCR.RSTFn = 1.

0 [23:13],

27,

[31:30]

r Reserved

Read as 0.

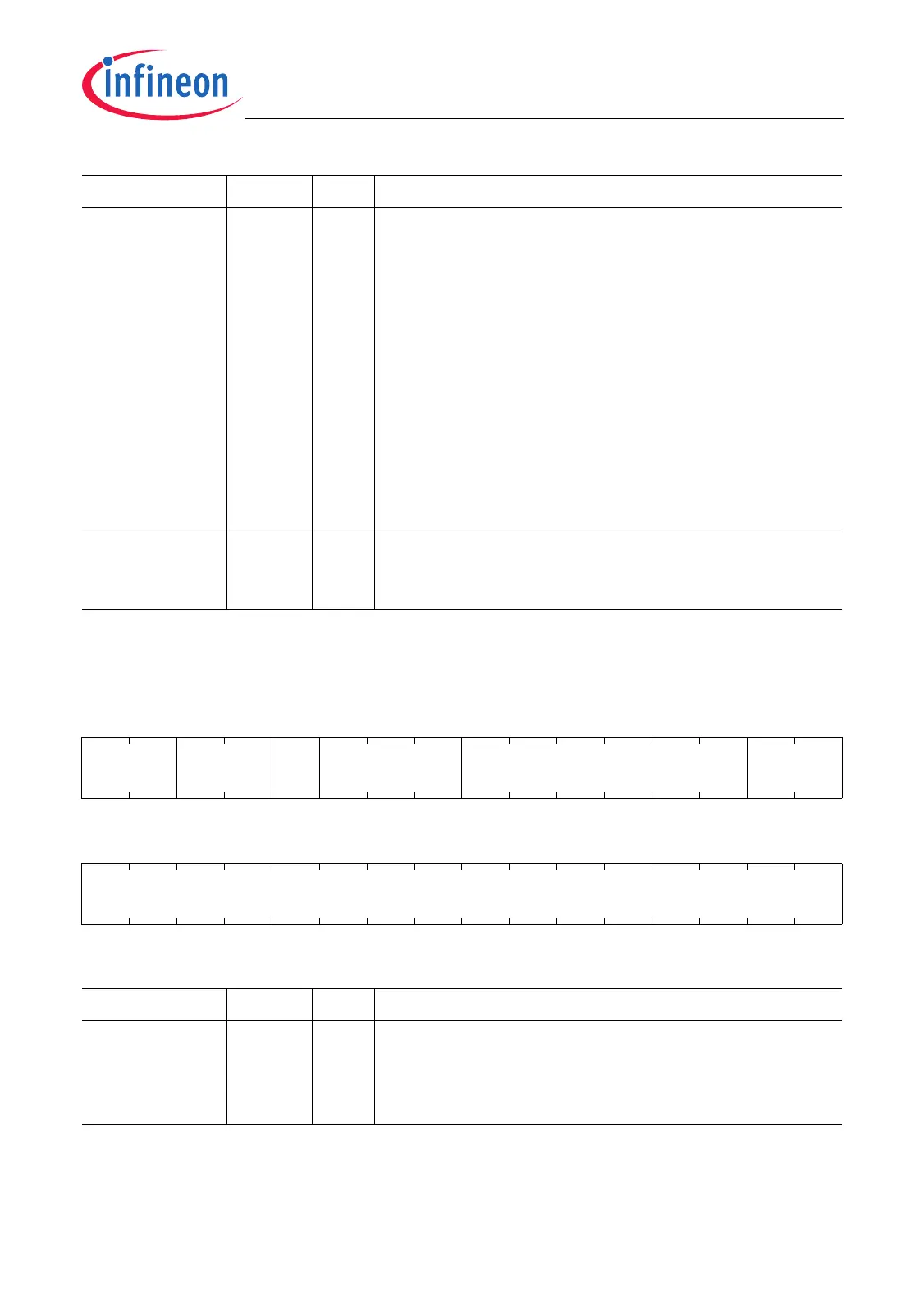

CRR1

Filter 1 Current Result Register (84

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0MAVS0 AC 0 CR

rrhrrh r rh

1514131211109876543210

CR

rh

Field Bits Type Description

CR [17:0] rh Current Result

This bit field ([12:0] for filter 0, [17:0] for filter 1)

contains the right-aligned current result value of

filter 0. CR is cleared when writing GCR.RSTFn = 1.

Field Bits Type Description

Loading...

Loading...