TC1796

Peripheral Units (Vol. 2 of 2)

Fast Analog-to-Digital Converter (FADC)

User’s Manual 26-54 V2.0, 2007-07

FADC, V2.0

The Intermediate Result Registers IRRxn hold the intermediate results x of filter n.

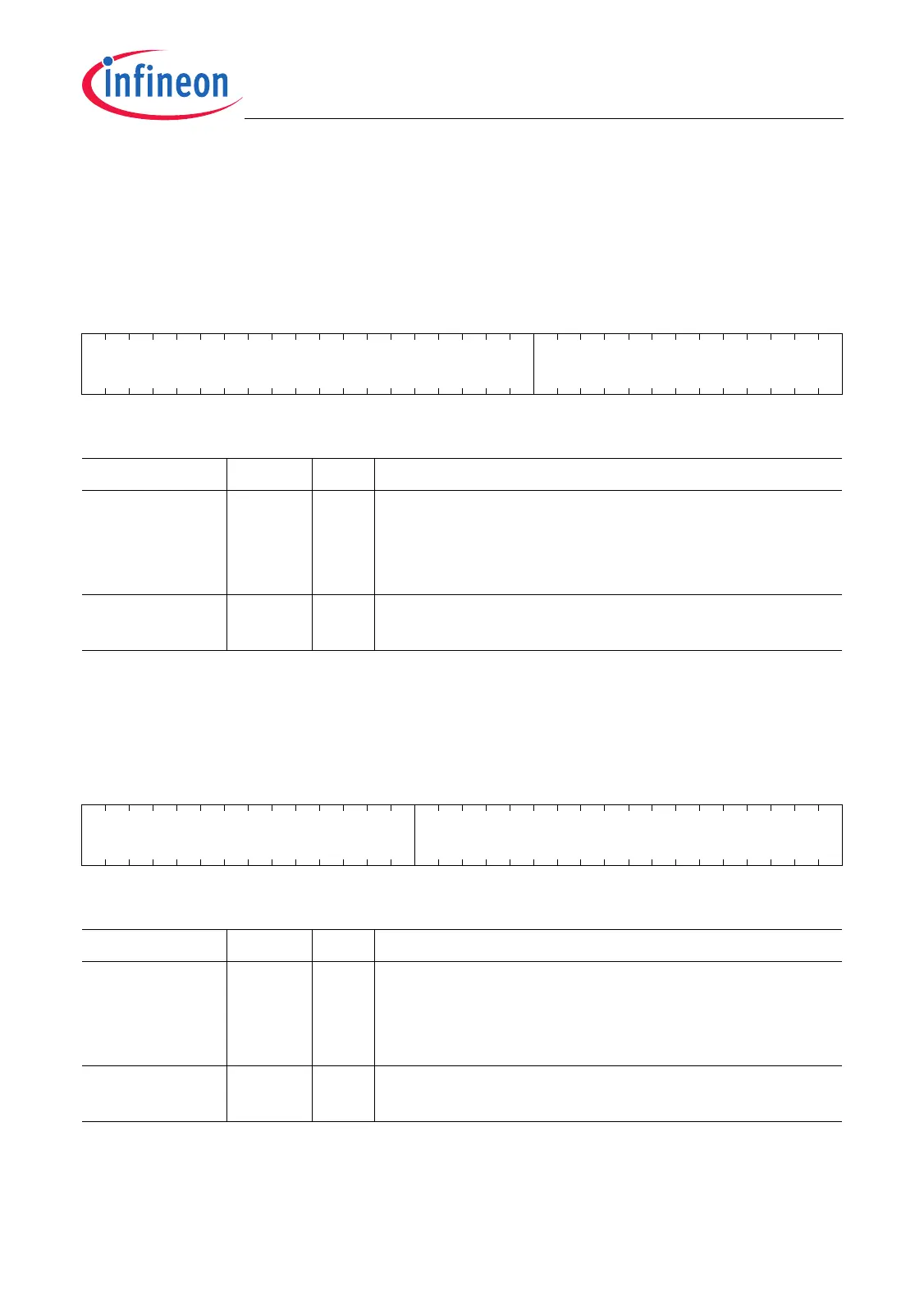

IRRx0 (x = 1-3)

Filter 0 Intermediate Result Register x

(64

H

+x*4

H

) Reset Value: 0000 0000

H

31 13 12 0

0IR

rrh

Field Bits Type Description

IR [12:0] rh Intermediate Result

This bit field contains the right-aligned intermediate

result of filter 0.

IR is cleared when writing GCR.RSTFn = 1.

0 [31:13] r Reserved

Read as 0.

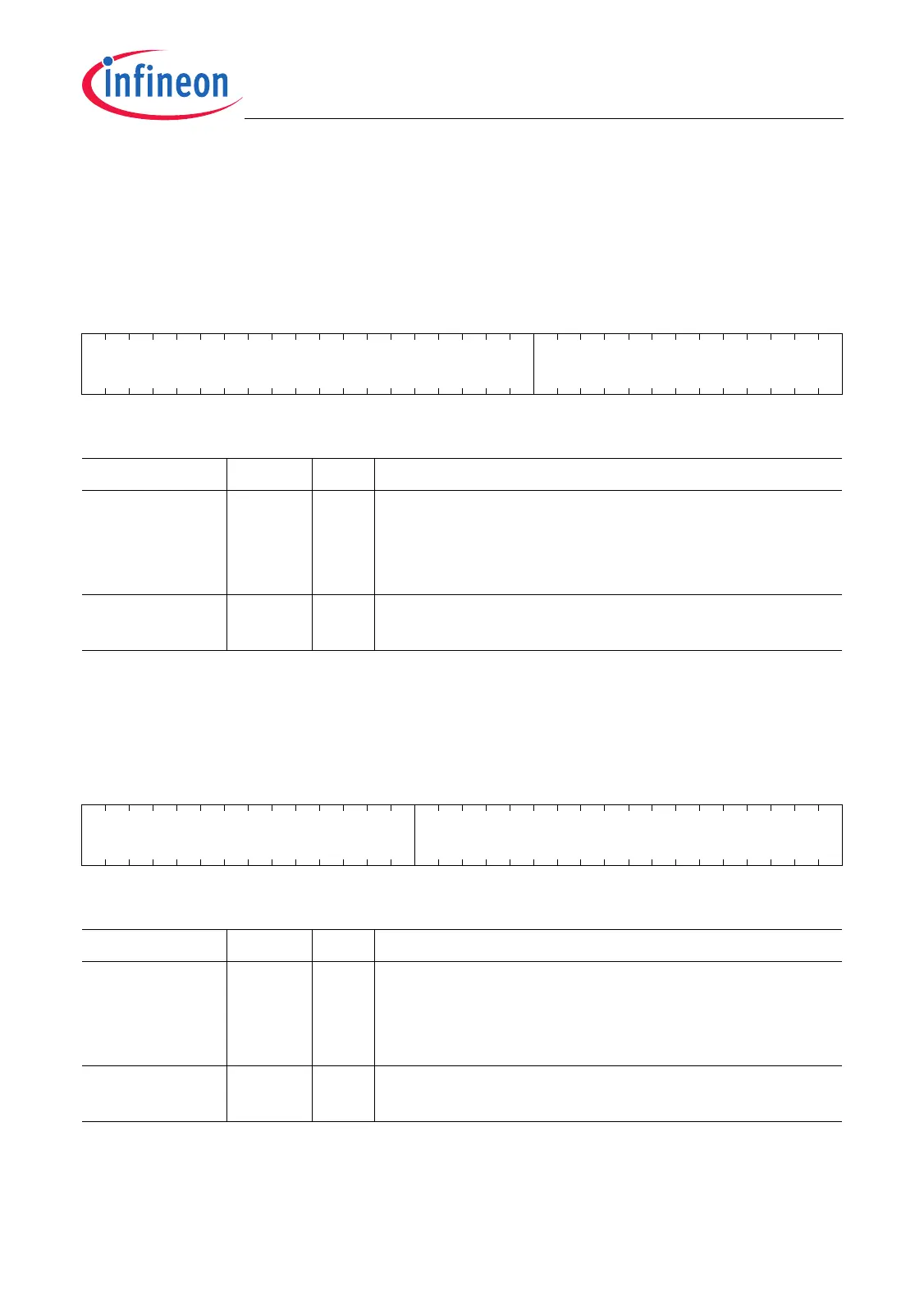

IRR11

Filter 1 Intermediate Result Register 1

(88

H

) Reset Value: 0000 0000

H

31 18 17 0

0IR

rrh

Field Bits Type Description

IR [17:0] rh Intermediate Result

This bit field contains the right-aligned intermediate

result of filter 1.

IR is cleared when writing GCR.RSTFn = 1.

0 [31:18] r Reserved

Read as 0.

Loading...

Loading...