TC1796

System Units (Vol. 1 of 2)

On-Chip System Buses and Bus Bridges

User’s Manual 6-48 V2.0, 2007-07

Buses, V2.0

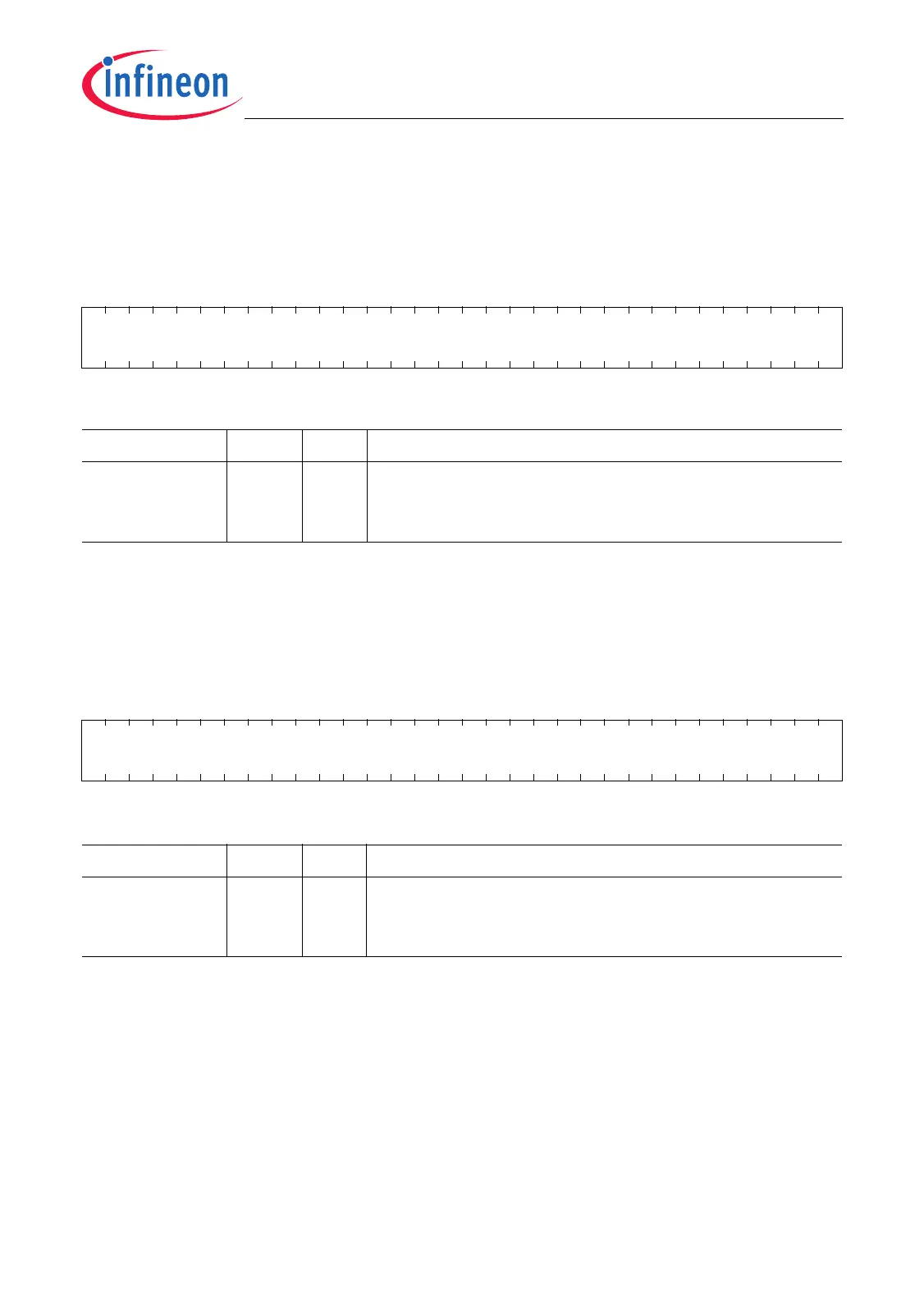

SBCU_DBADR1

SBCU Debug Address 1 Register (38

H

) Reset Value: 0000 0000

H

RBCU_DBADR1

RBCU Debug Address 1 Register (38

H

) Reset Value: 0000 0000

H

31 0

ADR1

rw

Field Bits Type Description

ADR1 [31:0] rw Debug Trigger Address 1

This register contains the address for the address 1

trigger event generation.

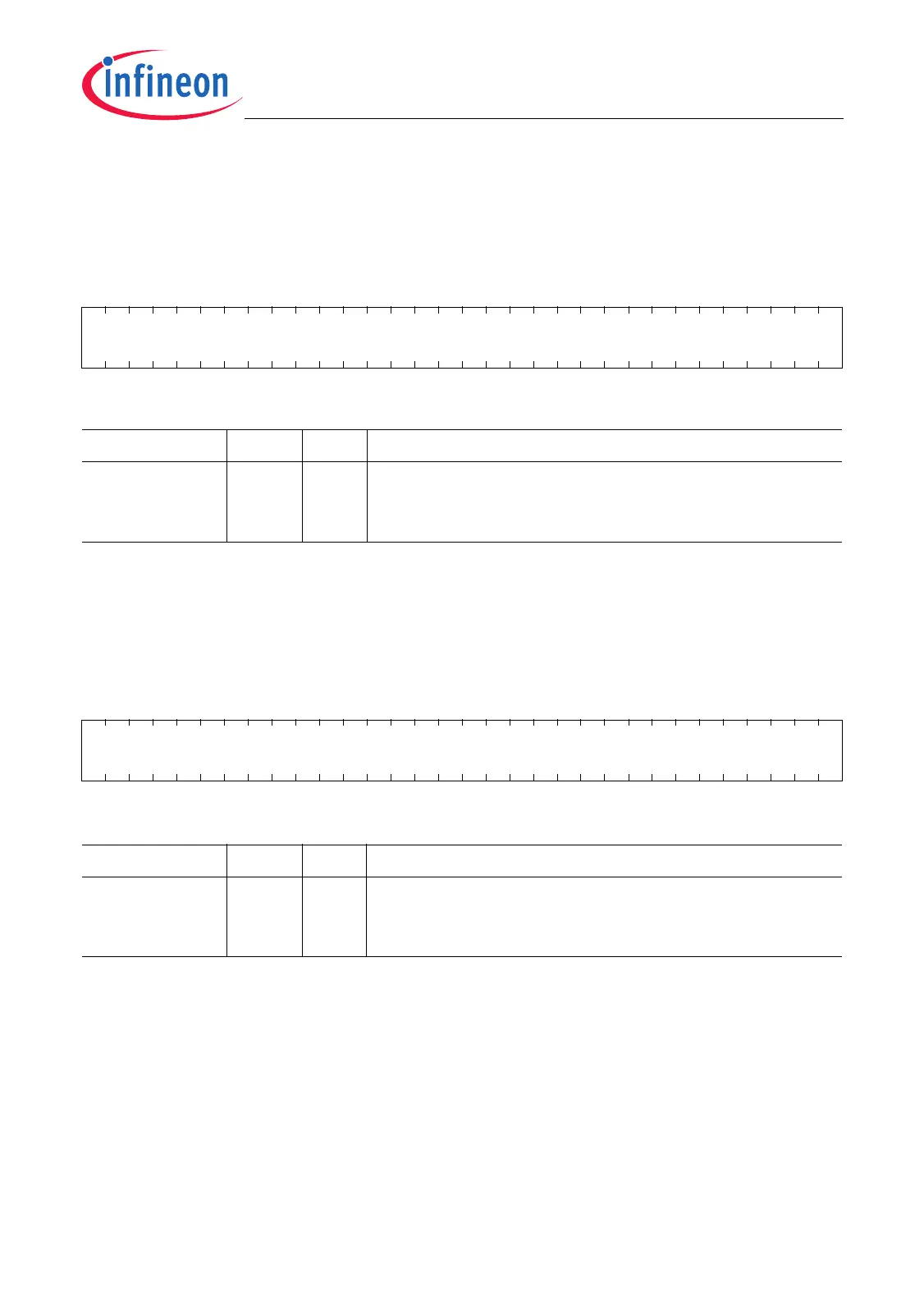

SBCU_DBADR2

SBCU Debug Address 2 Register (3C

H

) Reset Value: 0000 0000

H

RBCU_DBADR2

RBCU Debug Address 2 Register (3C

H

) Reset Value: 0000 0000

H

31 0

ADR2

rw

Field Bits Type Description

ADR2 [31:0] rw Debug Trigger Address 2

This register contains the address for the address 2

trigger event generation.

Loading...

Loading...