TC1796

System Units (Vol. 1 of 2)

On-Chip System Buses and Bus Bridges

User’s Manual 6-53 V2.0, 2007-07

Buses, V2.0

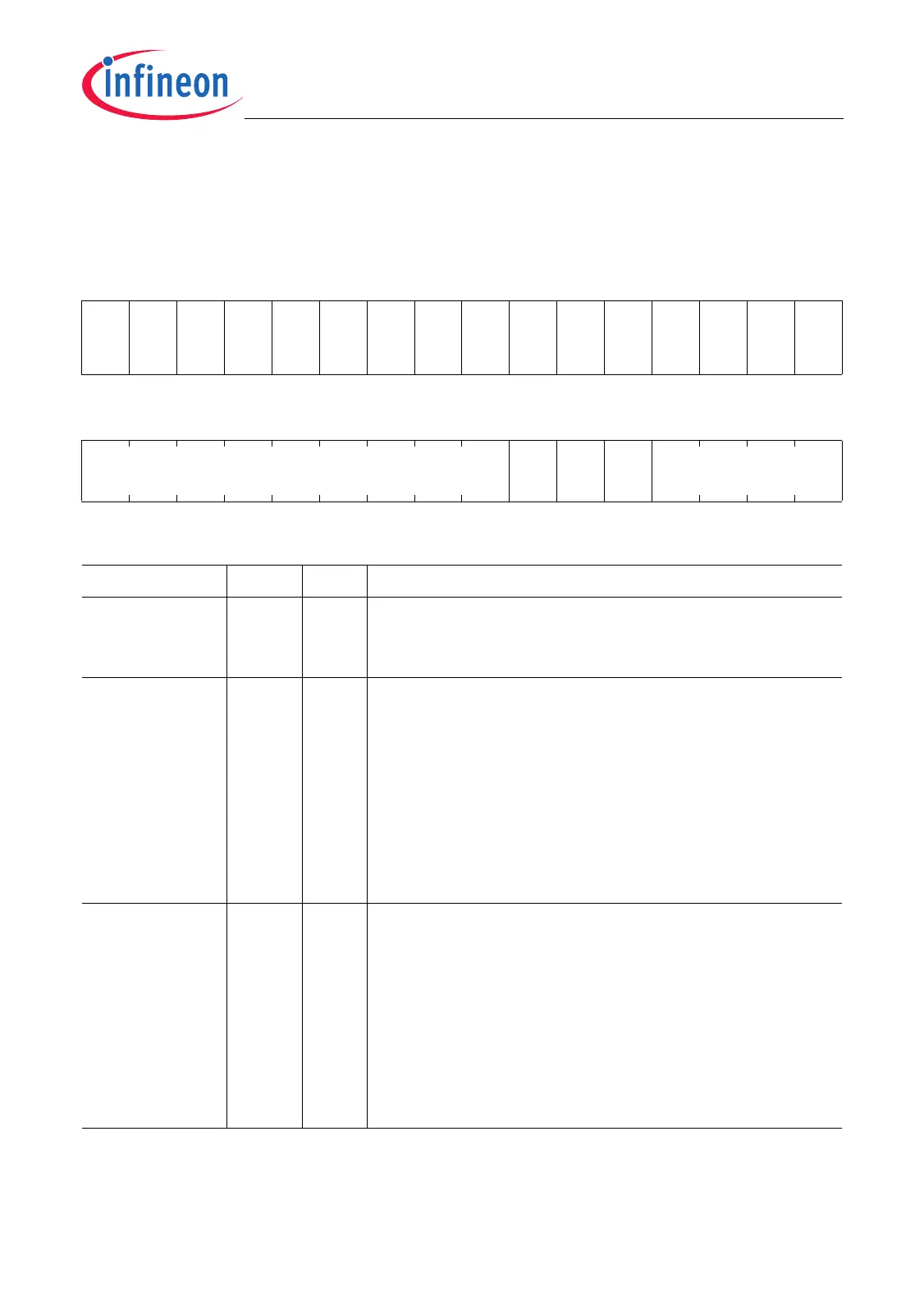

RBCU_DBGNTT

RBCU Debug Trapped Master Register

(44

H

) Reset Value: FFFF FFFF

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

CH

NR

17

CH

NR

16

CH

NR

15

CH

NR

14

CH

NR

13

CH

NR

12

CH

NR

11

CH

NR

10

CH

NR

07

CH

NR

06

CH

NR

05

CH

NR

04

CH

NR

03

CH

NR

02

CH

NR

01

CH

NR

00

rh rh rh rh rh rh rh rh rh rh rh rh rh rh rh rh

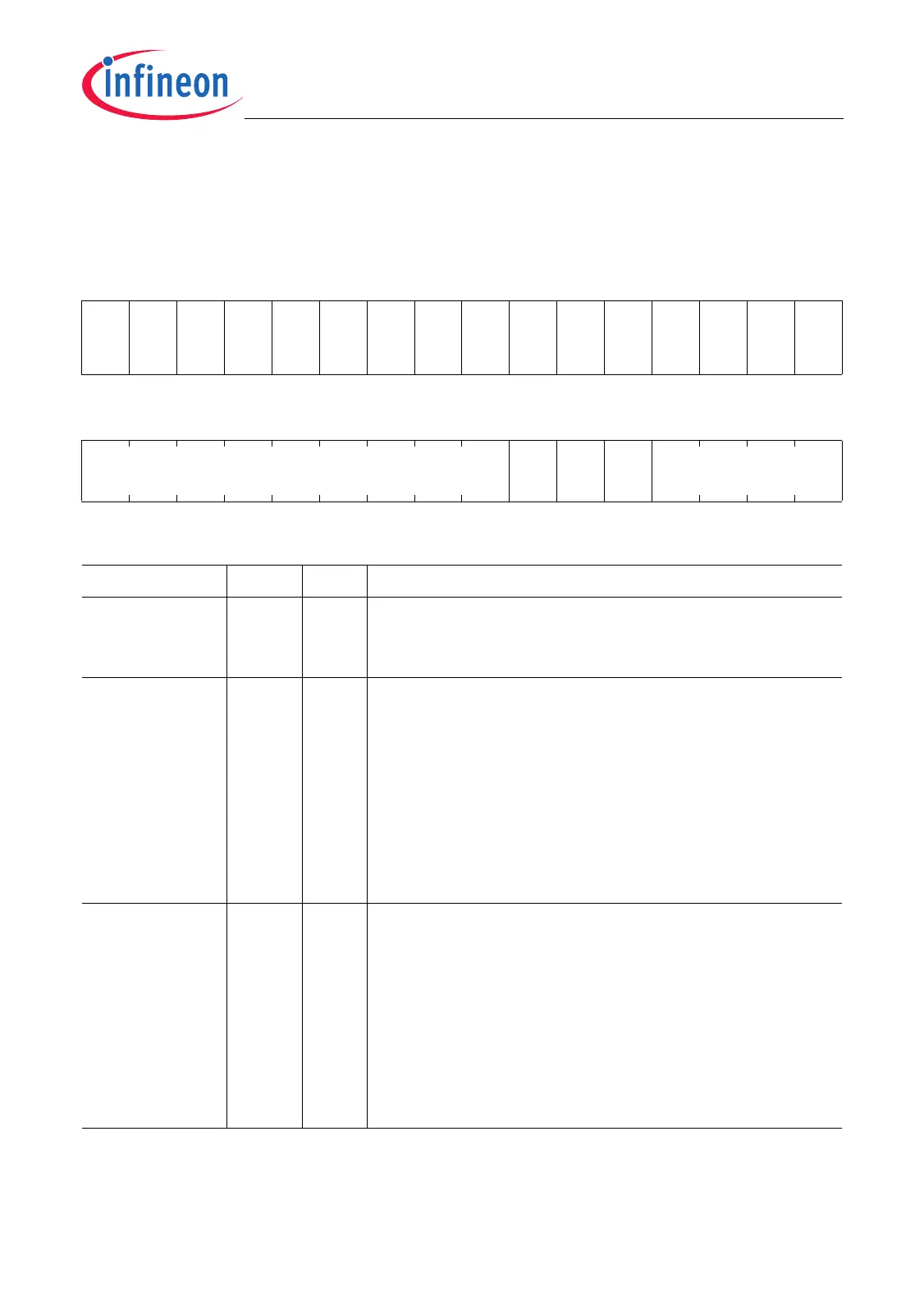

1514131211109876543210

1

DMA

L

1

DMA

H

1

rrhrrhr

Field Bits Type Description

1 [3:0],

5,

[15:7]

rw Reserved

Read as 1.

DMAH 2rhHigh-Priority DMA FPI Bus Master Status

This bit indicates whether the high-priority DMA

channels were RPB bus master when the break

trigger event occurred.

0

B

The high-priority DMA channels were not a

RPB bus master.

1

B

The high-priority DMA channels were RPB bus

master. Bits CHNRxy determine the DMA

channel number.

DMAL 4rhLow-Priority DMA FPI Bus Master Status

This bit indicates whether the low priority DMA

channels were RPB bus master when the break

trigger event occurred.

0

B

The low priority DMA channels were not a RPB

bus master.

1

B

The low priority DMA channels were RPB bus

master. Bits CHNRxy determine the DMA

channel number.

Loading...

Loading...