TC1796

System Units (Vol. 1 of 2)

Direct Memory Access Controller

User’s Manual 12-81 V2.0, 2007-07

DMA, V2.0

The Channel Interrupt Control Register control the interrupts generation.

DMA_CHICR0x (x = 0-7)

DMA Channel 0x Interrupt Control Register

(x*20

H

+88

H

) Reset Value: 0000 0000

H

DMA_CHICR1x (x = 0-7)

DMA Channel 1x Interrupt Control Register

(x*20

H

+188

H

) Reset Value: 0000 0000

H

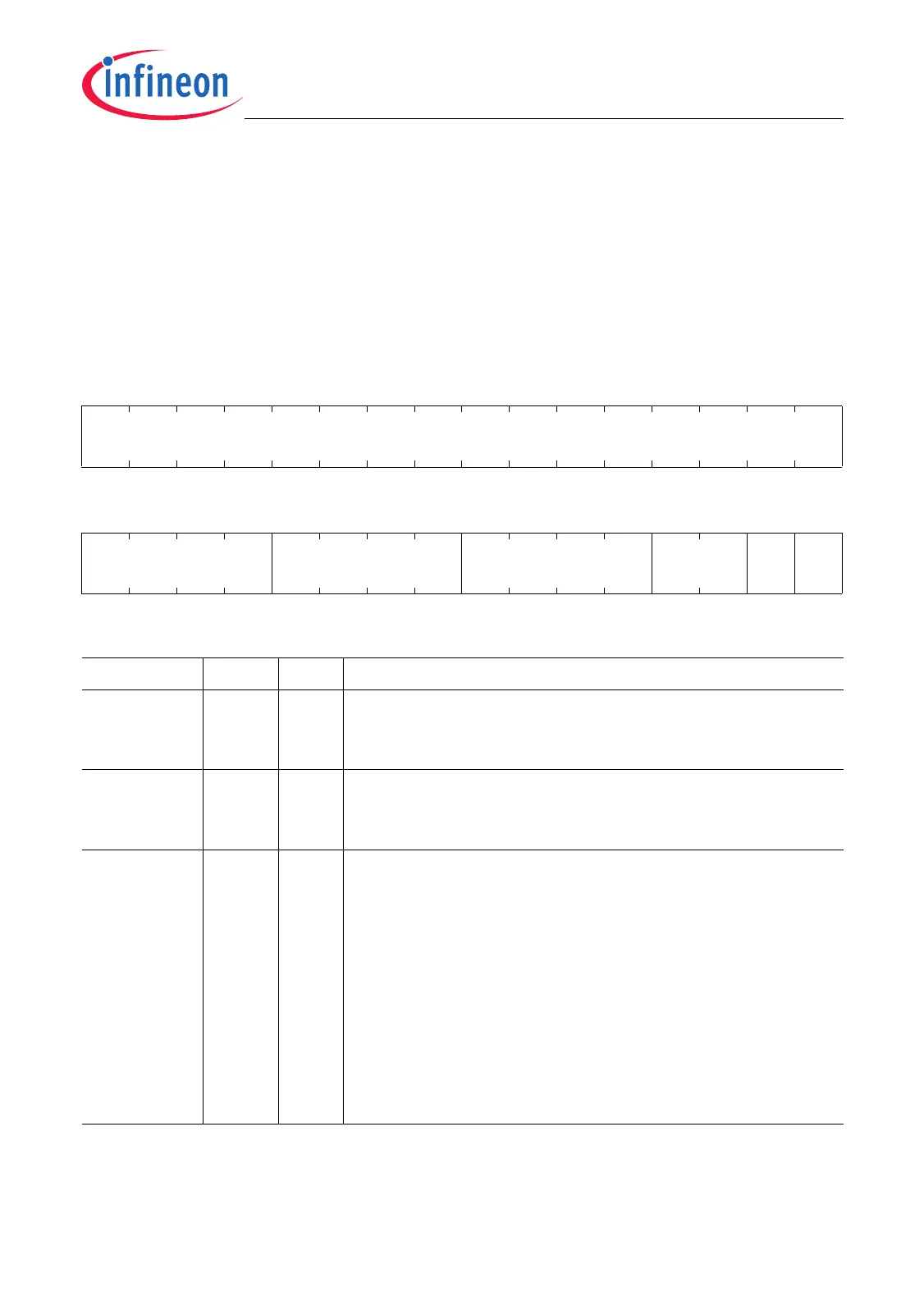

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

IRDV INTP WRPP INTCT

WRP

DE

WRP

SE

rw rw rw rw rw rw

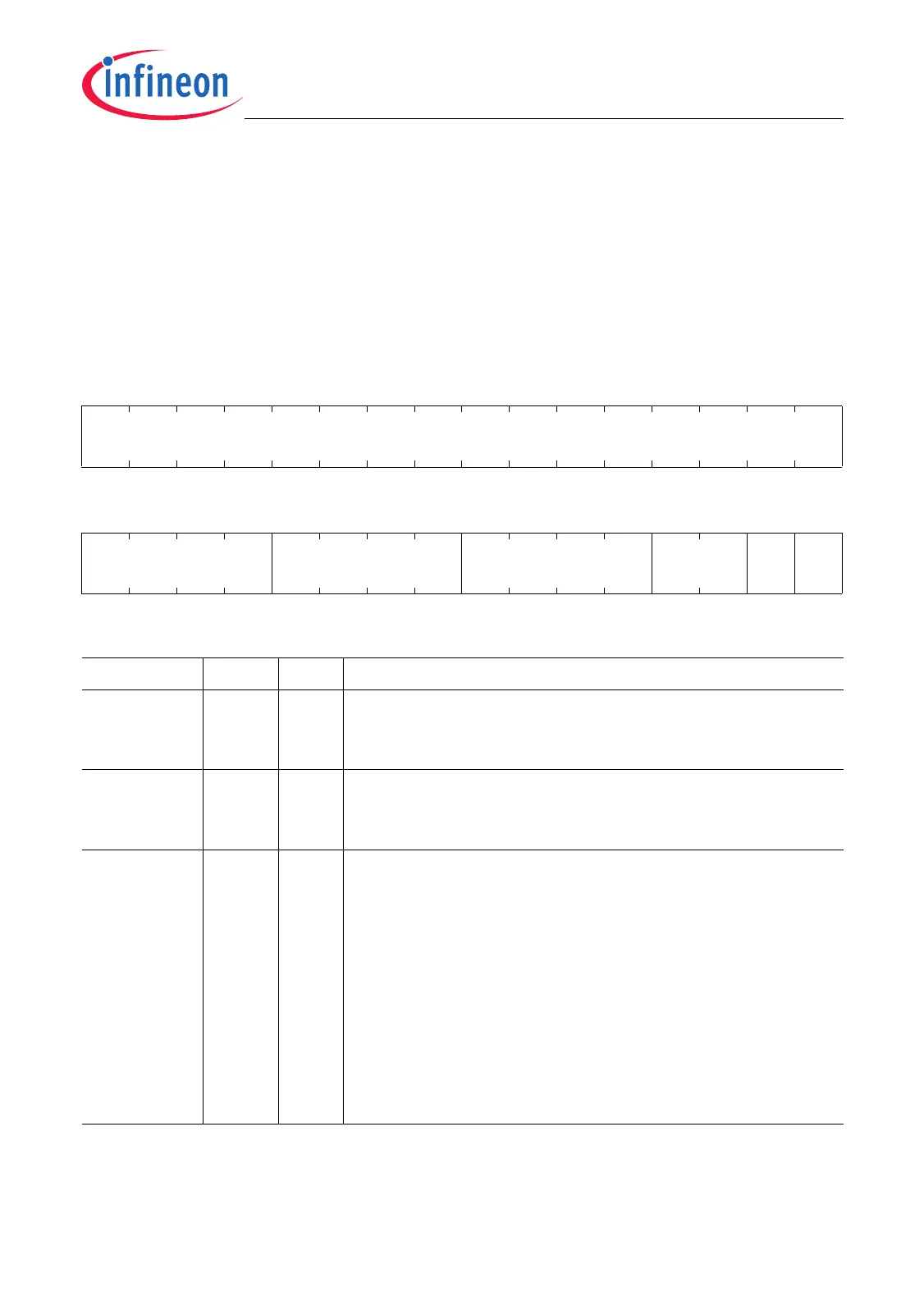

Field Bits Type Description

WRPSE 0rwWrap Source Enable

0

B

Wrap source buffer interrupt disabled

1

B

Wrap source buffer interrupt enabled

WRPDE 1rwWrap Destination Enable

0

B

Wrap destination buffer interrupt disabled

1

B

Wrap destination buffer interrupt enabled

INTCT [3:2] rw Interrupt Control

00

B

No interrupt will be generated on changing the

TCOUNT value. The bit INTSR.ICHmx is set when

TCOUNT equals IRDV.

01

B

No interrupt will be generated on changing the

TCOUNT value. The bit INTSR.ICHmx is set when

TCOUNT is decremented.

10

B

An interrupt is generated and bit INTSR.ICHmx is

set each time TCOUNT equals IRDV.

11

B

Interrupt is generated and bit INTSR.ICHmx is set

each time TCOUNT is decremented.

Loading...

Loading...