www.ti.com

Instruction Set

1097

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

High-End Timer (N2HET) Module

23.6.3.12 ECNT (Event Count)

Syntax ECNT {

[brk={OFF | ON}]

[next={label | 9-bit unsigned integer}]

[reqnum={3-bit unsigned integer}

[request={NOREQ | GENREQ | QUIET}]

[control={OFF | ON}]

[prv={OFF | ON}]

[cond_addr={label | 9-bit unsigned integer}]

pin={pin number}

event={NAF | FALL | RISE | BOTH | ACCUHIGH | ACCULOW}

[reg={A | B | R| S | T | NONE}]

[irq={OFF | ON}]

[data={25-bit unsigned integer]

}

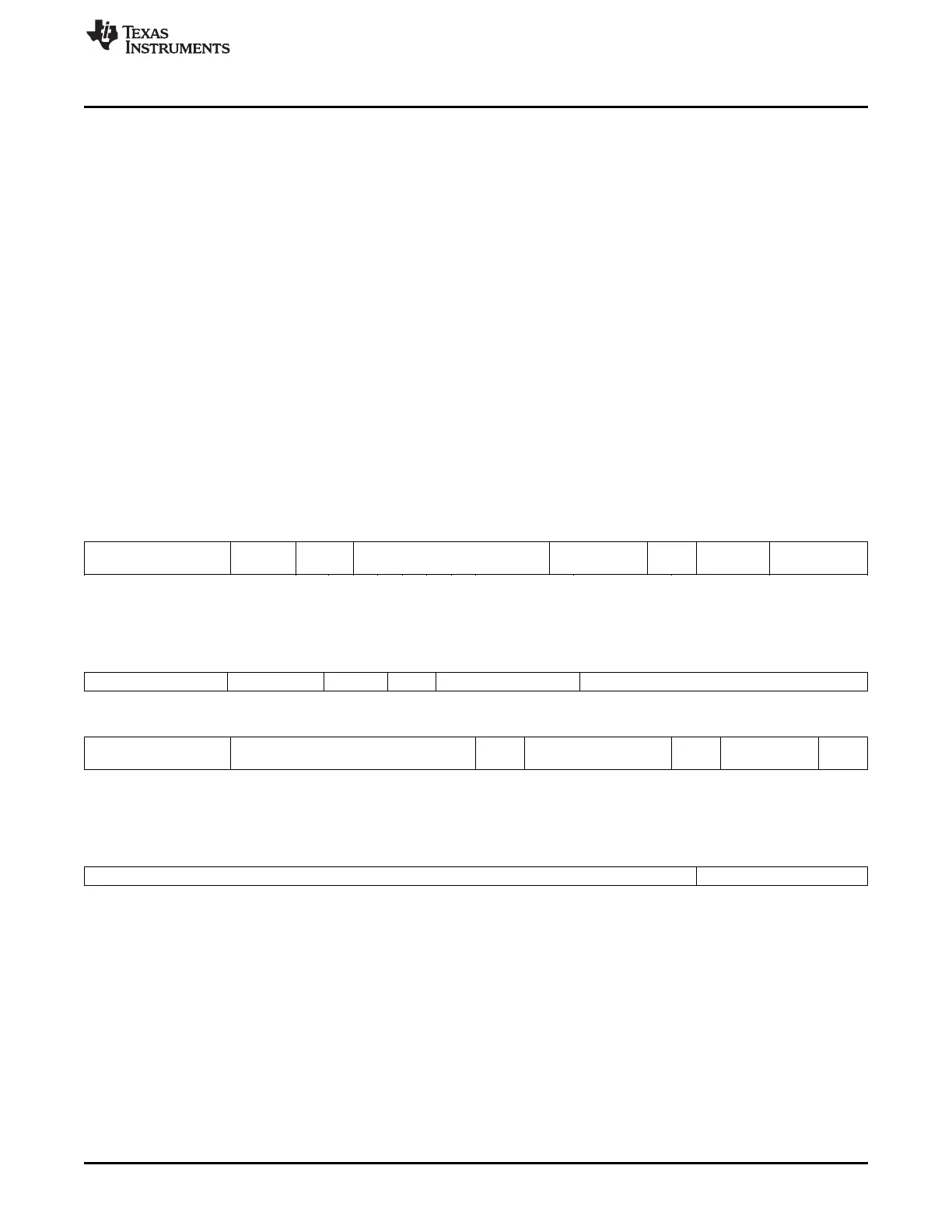

Figure 23-147. ECNT Program Field (P31:P0)

31 26 25 23 22 21 13 12 9 8 7 6 5 0

0 Request

Number

BRK Next program address 1010 Res. 01 Reserved

6 3 1 9 4 1 2 6

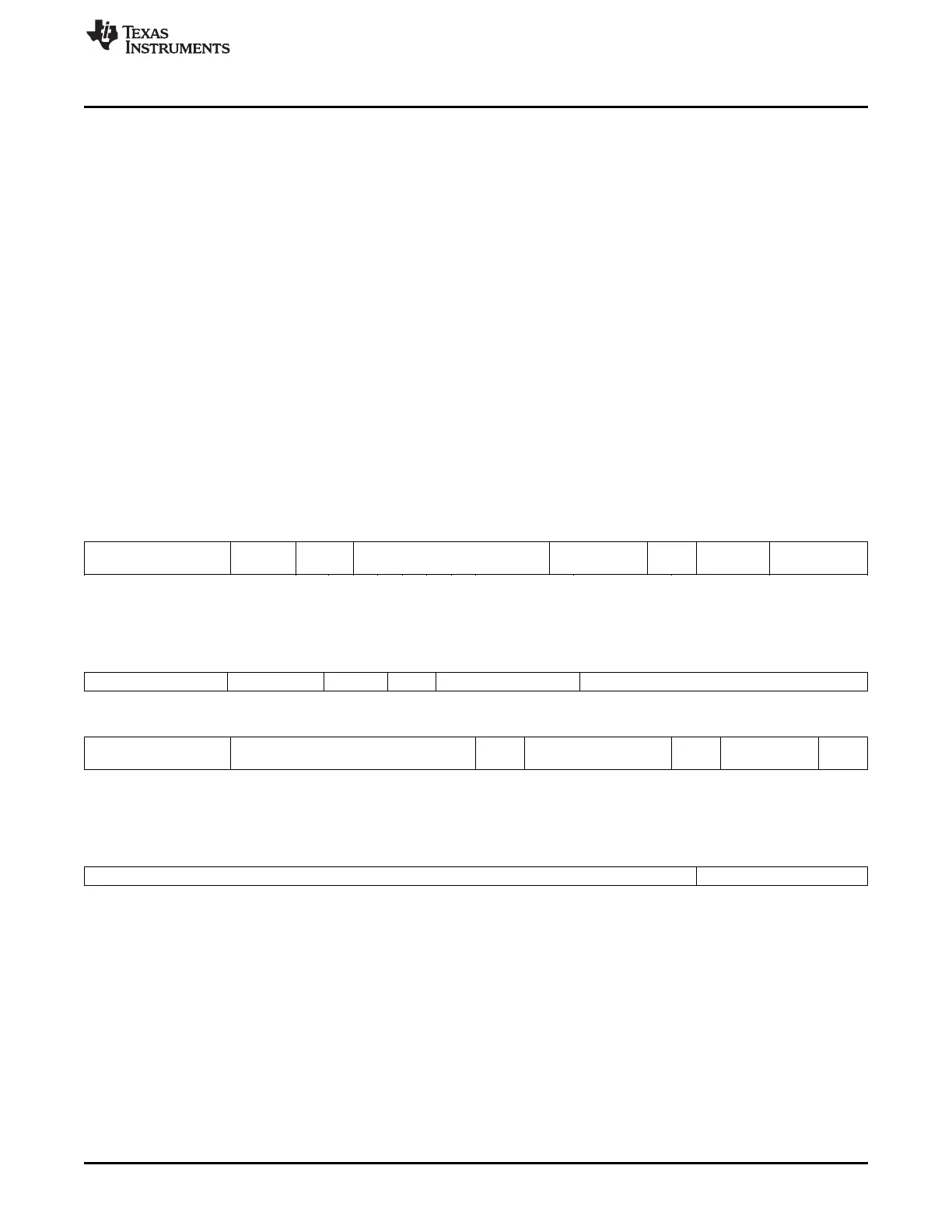

Figure 23-148. ECNT Control Field (C31:C0)

31 29 28 27 26 25 24 22 21 16

Reserved Request type Control Prv. Reserved Conditional address

3 2 1 1 3 9

15 13 12 8 7 6 4 3 2 1 0

Conditional address Pin select Ext

Reg

Event Res. Register select Int.

ena

9 5 1 3 1 2 1

Figure 23-149. ECNT Data Field (D31:D0)

31 7 6 0

Data Reserved

25 7

Cycles One cycle

Register modified Selected Register (A, B, R, S, T or none)

Description This instruction defines a specialized 25-bit virtual counter used as an event

counter or pulse accumulator (see Table 23-85). The counter value is stored

in the data field [D31:D7] and the selected register. If one of the 32-bit

registers (R,S,T) is selected, the 25 bit count value is stored left justified in the

register with zeros in the seven least significant bits.

When an event count condition is specified, the counter value is incremented

on a pin edge condition or on the NAF condition (NAF is defined in ACNT).

This instruction can be used with all pins.

Loading...

Loading...