www.ti.com

FlexRay Module Registers

1281

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

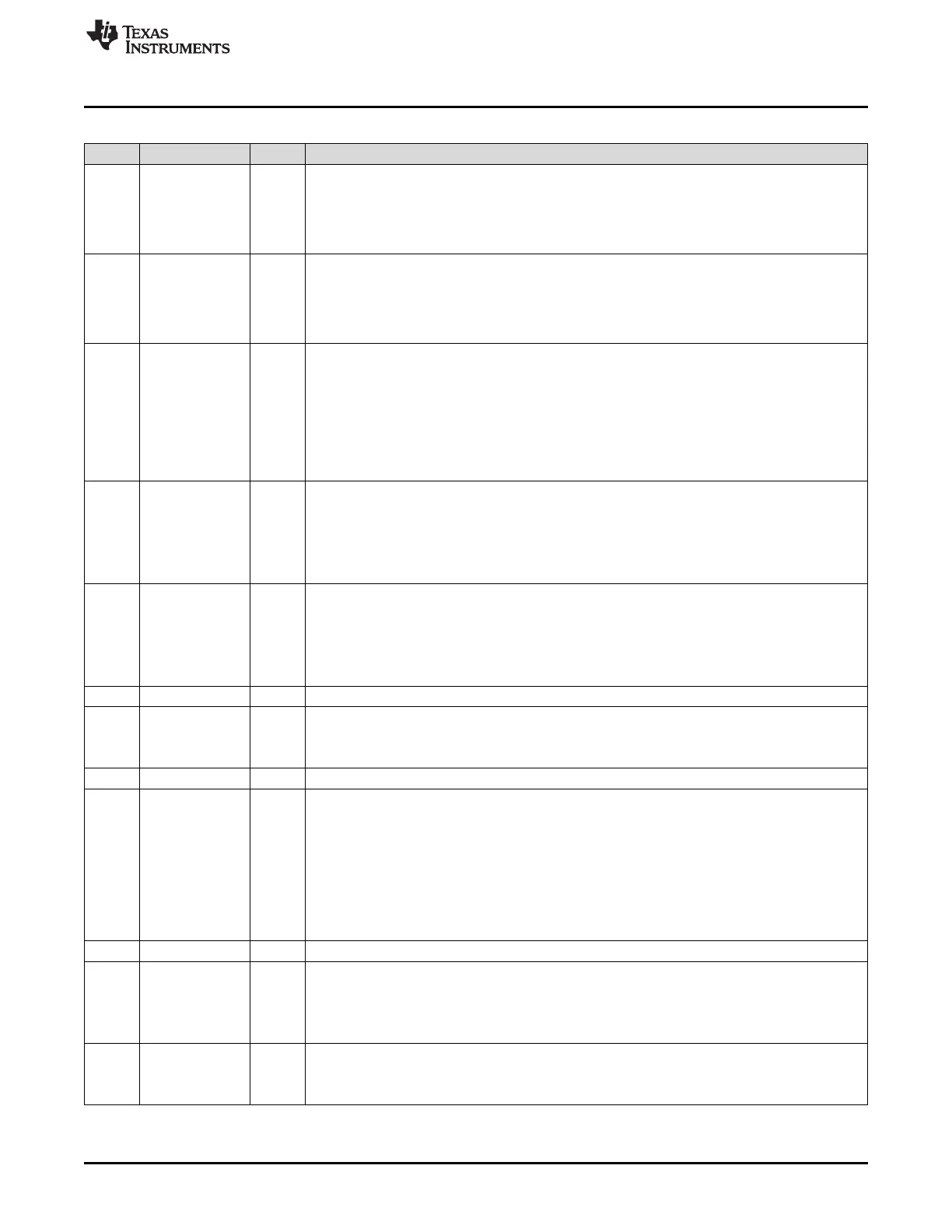

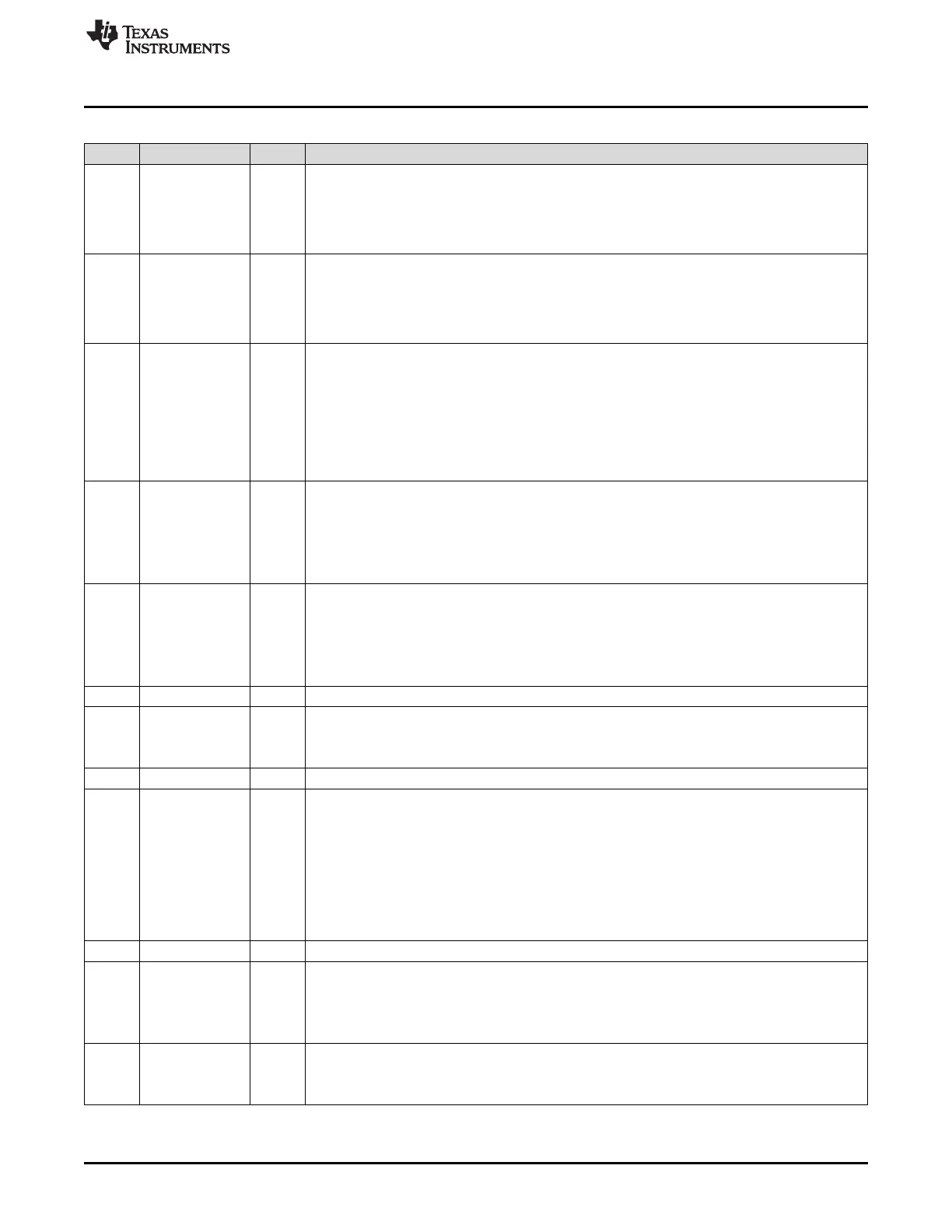

Table 26-21. Global Control Set/Reset (GCS/R) Field Descriptions

Bit Field Value Description

31 ENDVBM Endianness Correction on VBusp Master.

0 Endianness correction switched off (Endianness is default: Little Endianness equal to Big Endian

word invariant (ARM:BE-32), same as all other peripherals) (Example 32 Bit Word = ABCD).

1 Endianness correction switched on (E-Ray Register, Header and Payload Endianness is according

the configuration of bits ENDR0/1 ENDH0/1, ENDP0/1).

30 ENDVBS Endianness correction on VBusp Slave.

0 Endianness correction switched off (Endianness is default: Little Endianness equal to Big Endian

word invariant (ARM:BE-32), same as all other peripherals) (Example 32 Bit Word = ABCD).

1 Endianness correction switched on (E-Ray Register, Header and Payload Endianness is according

the configuration of bits ENDR0/1, ENDH0/1, ENDP0/1).

29-28 ENDR Endianness Correction for No (header or payload) Data Sink Access.

Byte-order control of CPU access to E-Ray register, Transfer Unit register and Transfer Unit ram

data. Data transferred between CPU and data sink will be corrected.

0 Remapped to ABCDh.

1h Remapped to BADCh.

2h Remapped to CDABh.

3h Remapped to DCBAh.

27-26 ENDH Endianness Correction for Header.

0 Remapped to ABCDh.

1h Remapped to BADCh.

2h Remapped to CDABh.

3h Remapped to DCBAh.

25-24 ENDP Endianness Correction for Payload.

0 Remapped to ABCDh.

1h Remapped to BADCh.

2h Remapped to CDABh.

3h Remapped to DCBAh.

23-22 Reserved 0 Reads return 0. Writes have no effect.

21 PRIO Transfer Priority.

0 TTSM gets higher priority than TTCC.

1 TTCC gets higher priority than TTSM.

20 Reserved 0 Reserved

19-16 PEL ECC Lock.

5h ECC interrupt generation for TCR is switched off. ECC protection for message RAM, transient

buffer RAMs, input buffer RAMs and output buffer RAMs is switched off.

Others ECC interrupt generation for TCR is switched on. ECC protection for message RAM, transient

buffer RAMs, input buffer RAMs and output buffer RAMs is switched on.

Note: For TCR, PEL enables or disables the ECC multi-bit error interrupt generation. While the

ECC feature is disabled, the ECC generation is still ongoing and the error indication by the ECC

interrupt flag (PE) in the Transfer Error Interrupt Flag register (TEIF) remains active. Only the ECC

interrupt generation gets disabled.

15 Reserved 0 Reads return 0. Writes have no effect.

14 CETESM Clear ETESM Register.

Clear all bits of Enable Transfer on Event to System Memory register.

0 Do not clear the register.

1 Clear the register when bit is set from 0 to 1.

13 CTTCC Clear TTCC Register.

0 Do not clear the register.

1 Clear the register when bit is set from 0 to 1.

Loading...

Loading...