www.ti.com

DCAN Control Registers

1457

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Controller Area Network (DCAN) Module

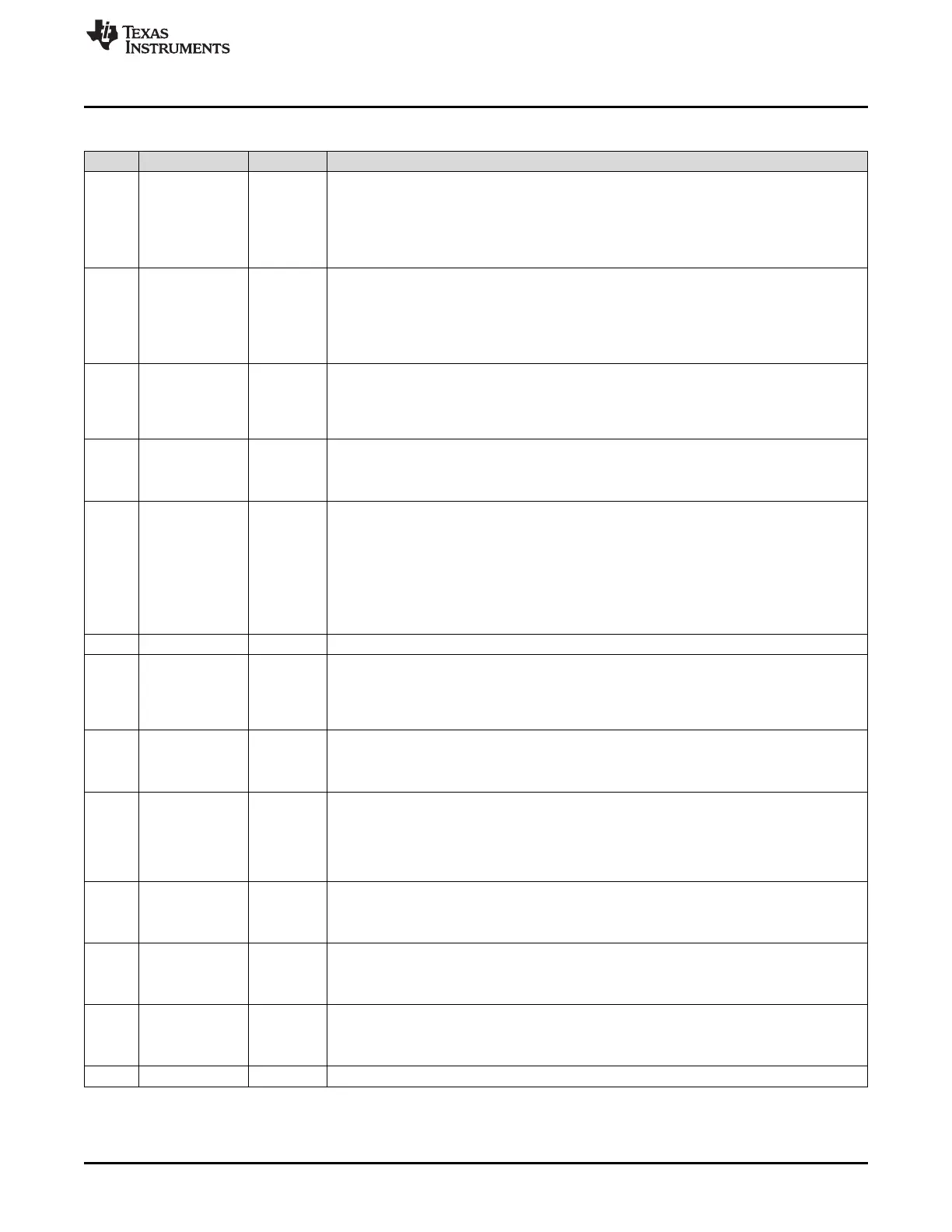

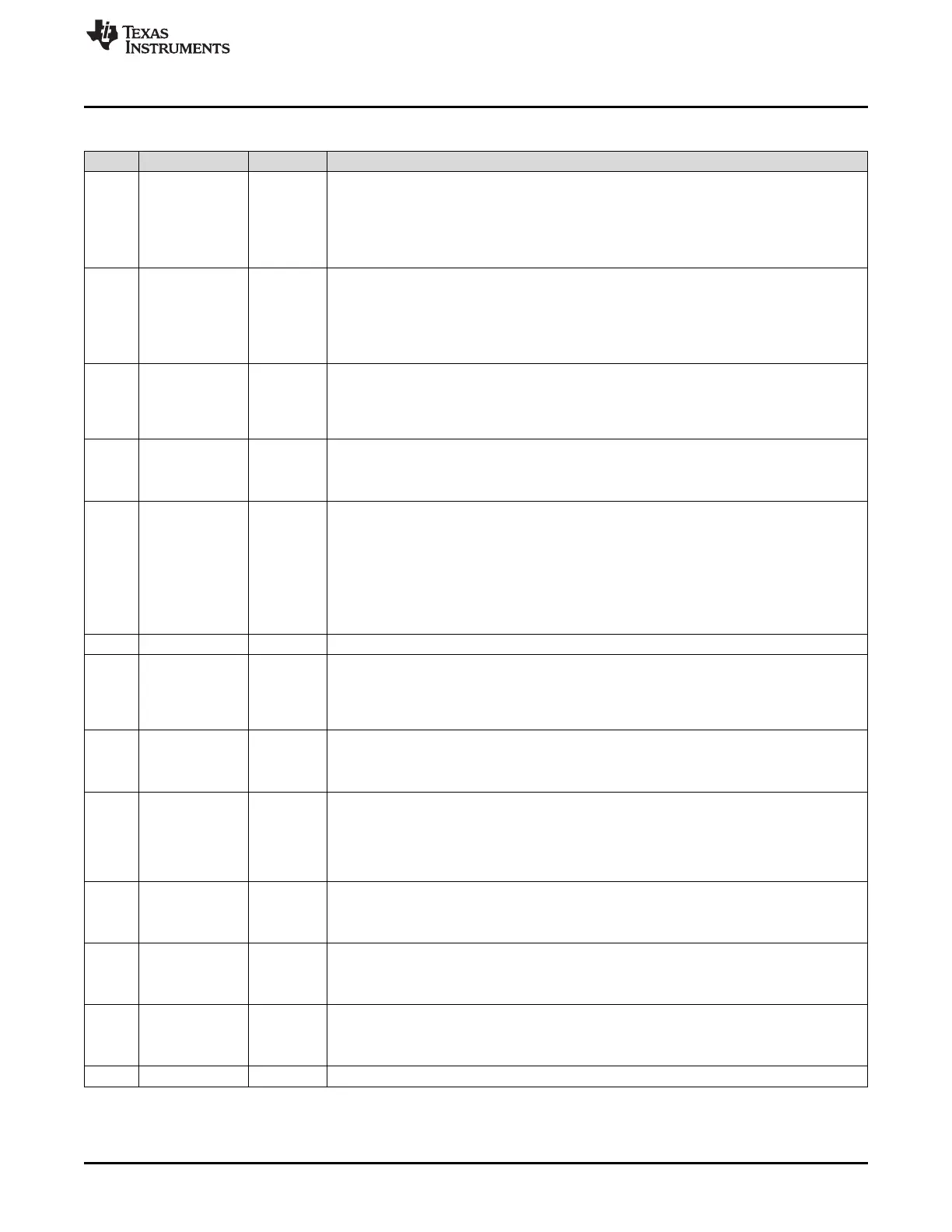

Table 27-7. CAN Control Register (DCAN CTL) Field Descriptions (continued)

Bit Field Value Description

19 DE2 Enable DMA request line for IF2.

0 Disabled

1 Enabled

Note: A pending DMA request for IF2 remains active until first access to one of the IF2

registers.

18 DE1 Enable DMA request line for IF1.

0 Disabled

1 Enabled

Note: A pending DMA request for IF1 remains active until first access to one of the IF1

registers.

17 IE1 Interrupt line 1 enable.

0 Disabled. Module Interrupt DCAN1INT is always low.

1 Enabled. Interrupts will assert line DCAN1INT to one; line remains active until pending

interrupts are processed.

16 InitDbg Internal Init state while debug access.

0 Not in debug mode, or debug mode requested but is not entered.

1 Debug mode requested and is internally entered; the DCAN is ready for debug accesses.

15 SWR SW reset enable.

0 Normal operation.

1 Module is forced to reset state. This bit will automatically get cleared after execution of SW

reset after one VBUSP clock cycle.

Note: To execute SW reset the following procedure is necessary:

1. Set Init bit to shut down CAN communication.

2. Set SWR bit additionally to Init bit.

14 Reserved 0 This bit is always read as 0. Writes have no effect.

13-10 PMD SECDED enable.

5h SECDED function is disabled.

All other

values

SECDED function is enabled.

9 ABO Auto-Bus-On enable.

0 The Auto-Bus-On feature is disabled.

1 The Auto-Bus-On feature is enabled.

8 IDS Interruption debug support enable.

0 When Debug/Suspend mode is requested, DCAN will wait for a started transmission or

reception to be completed before entering Debug/Suspend mode.

1 When Debug/Suspend mode is requested, DCAN will interrupt any transmission or reception,

and enter Debug/Suspend mode immediately.

7 Test Test mode enable.

0 Normal operation.

1 Test mode.

6 CCE Configuration change enable.

0 The CPU has no write access to the BTR Config register.

1 The CPU has write access to the BTR configuration register (when Init bit is set).

5 DAR Disable automatic retransmission.

0 Automatic Retransmission of not successful messages is enabled.

1 Automatic Retransmission is disabled.

4 Reserved 0 This bit is always read as 0. Writes have no effect.

Loading...

Loading...