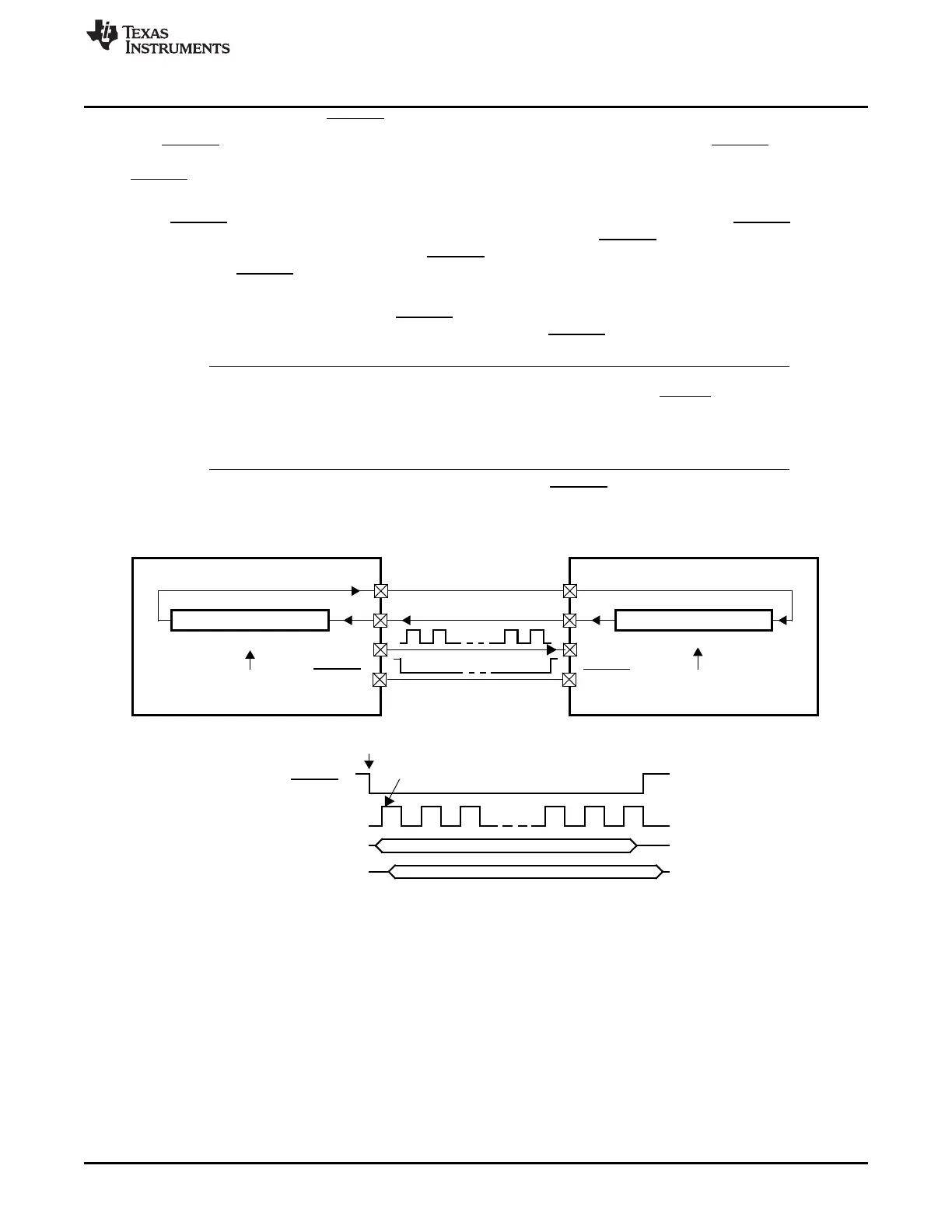

Master

Slave

(Master = 1; CLKMOD = 1)

(Master = 0; CLKMOD = 0)

SPIDAT0 SPIDAT0

MSB LSB

MSB

LSB

Write to SPIDAT0

SPISOMI

SPISIMO

SPISOMI

SPISIMO

SPICLK SPICLK

SPIENA SPIENA

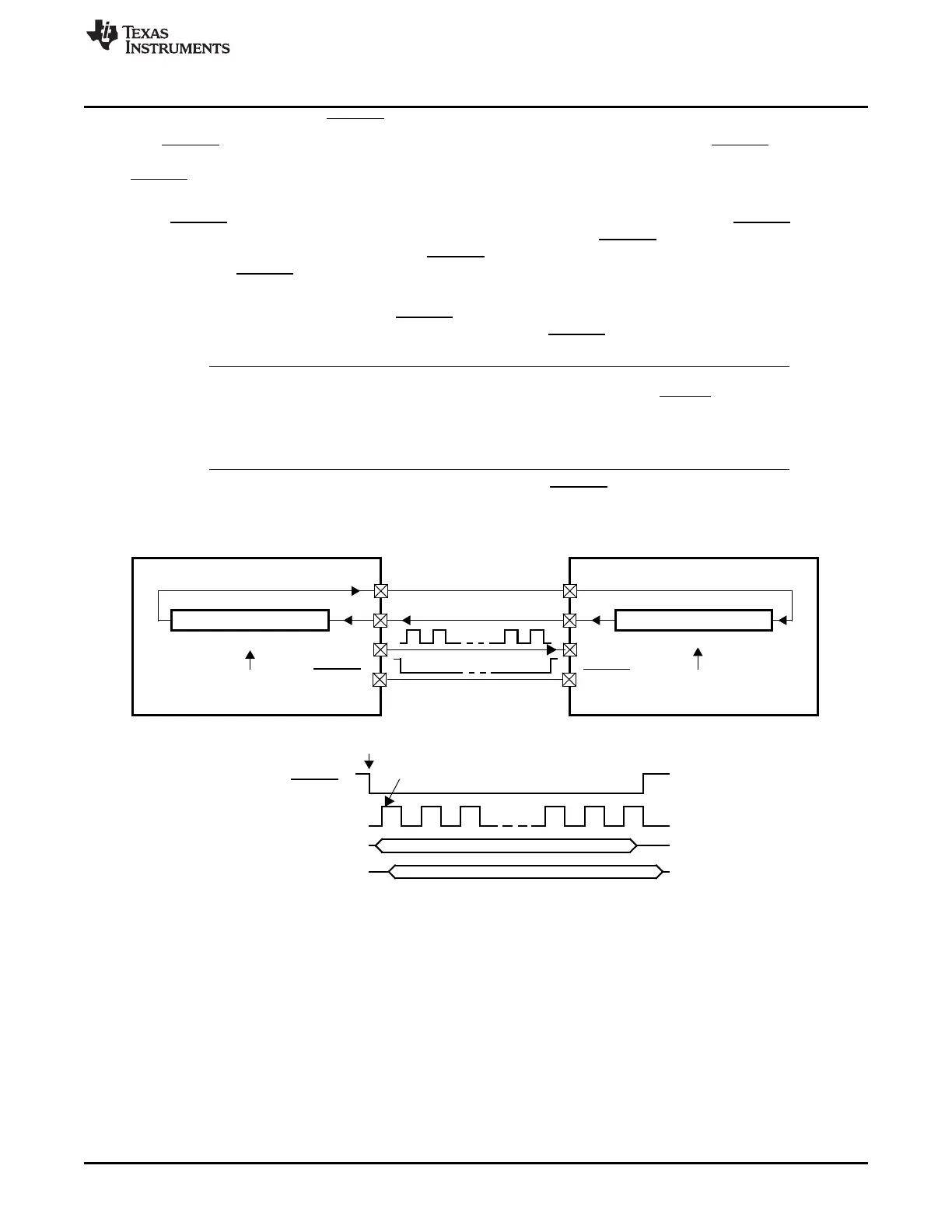

Write to SPIDAT0

Write to SPIDAT0 (SLAVE)

Write to SPIDAT0 (master)

SPICLK

SPISIMO

SPISOMI

SPIENA

www.ti.com

Basic Operation

1509

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Multi-Buffered Serial Peripheral Interface Module (MibSPI) with Parallel Pin

Option (MibSPIP)

28.2.5.2.2 Four-Pin Option with SPIENA

The SPIENA operates as a WAIT signal pin. For both the slave and the master, the SPIENA pin must be

configured to be functional (SPIPC0[8] = 1). In this mode, an active-low signal from the slave on the

SPIENA pin allows the master SPI to drive the clock pulse stream. A high signal tells the master to hold

the clock signal (and delay SPI activity).

If the SPIENA pin is in high-impedance mode (ENABLE_HIGHZ = 1), the slave will put SPIENA into the

high-impedance once it completes receiving a new character. If the SPIENA pin is in push-pull mode

(ENABLE_HIGHZ = 0), the slave will drive SPIENA to 1 once it completes receiving a new character. The

slave will drive SPIENA low again for the next word to transfer, after new data is written to the slave TX

shift register.

In master mode (CLKMOD = 1), if the SPIENA pin is configured as functional, then the pin acts as an

input pin. If configured as a slave SPI and as functional, the SPIENA pin acts as an output pin.

NOTE: During a transfer, if a slave-mode SPI detects a deassertion of its chip select before its

internal character length counter overflows, then it places SPISOMI and SPIENA (if

ENABLE_HIGHZ bit is set to 1) in high-impedance mode. Once this condition has occurred,

if a SPICLK edge is detected while the chip select is deasserted, then the SPI stops that

transfer and sets an DLENERR error flag and generates an interrupt (if enabled).

Figure 28-8. Operation with SPIENA

Loading...

Loading...