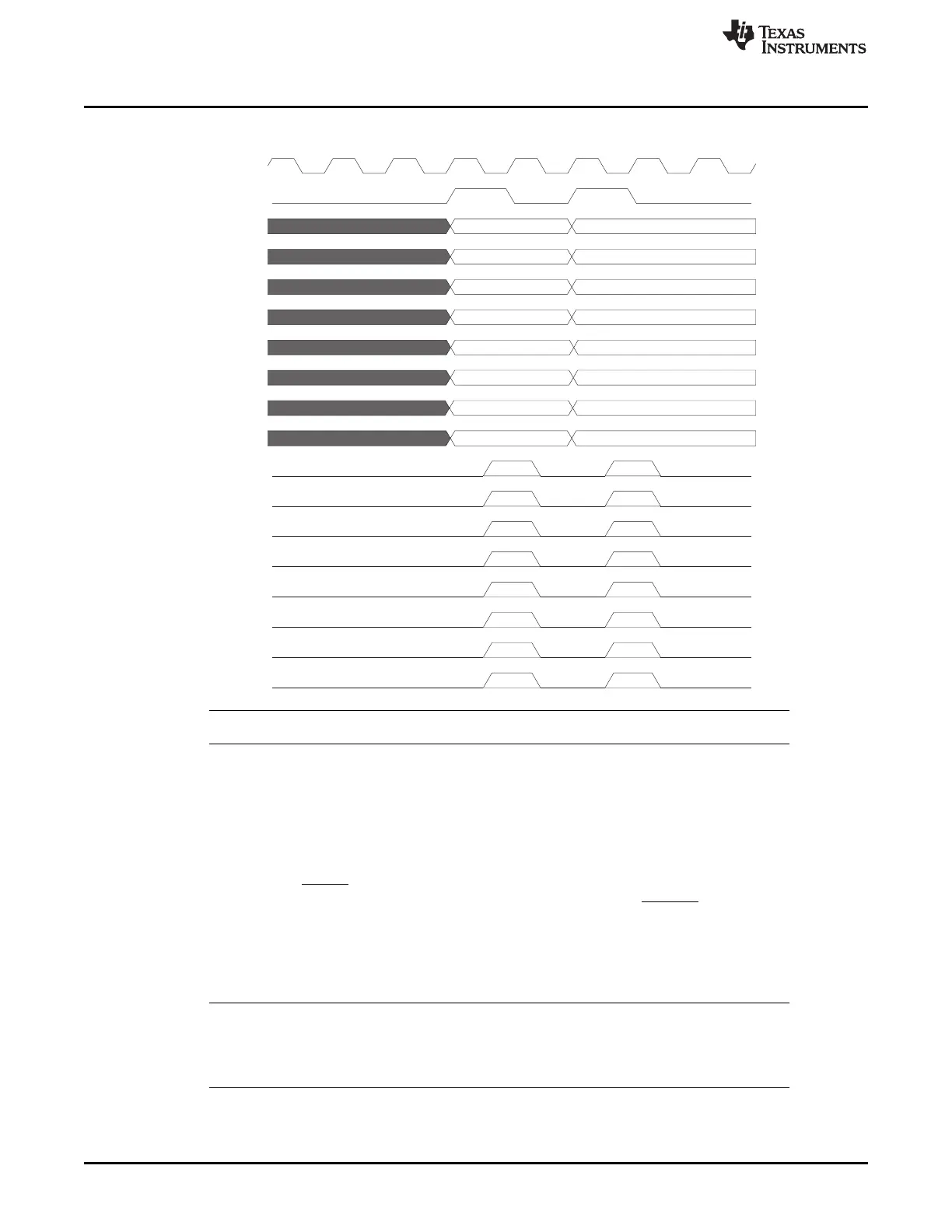

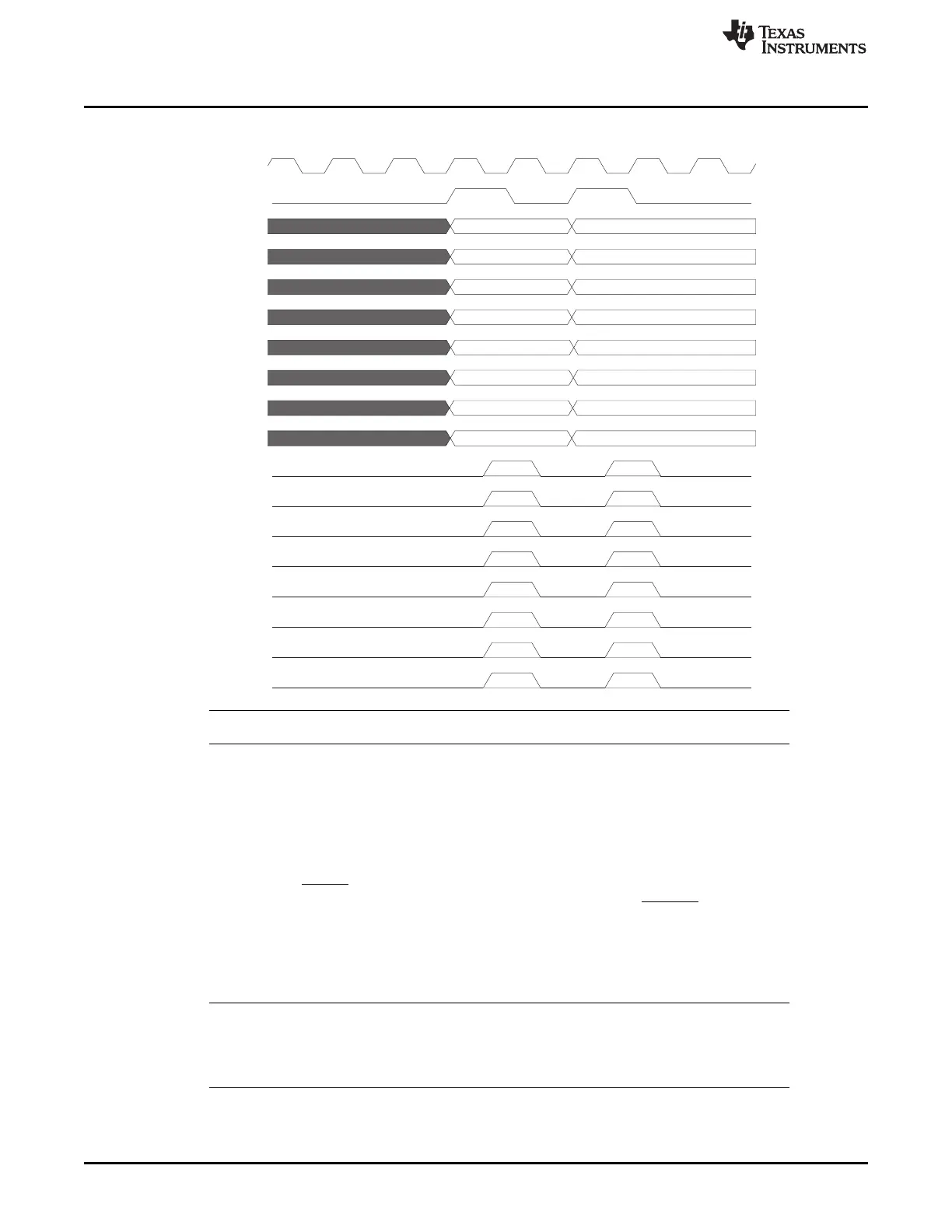

15 14

13 12

11 10

9 8

7 6

5 4

3 2

1 0

15 14

13 12

11 10

9 8

7 6

5 4

3 2

1 0

VCLK

SPICLK

SIMO[7]

SIMO[6]

SIMO[5]

SIMO[4]

SIMO[3]

SIMO[2]

SIMO[1]

SIMO[0]

SOMI[7]

SOMI[6]

SOMI[5]

SOMI[4]

SOMI[3]

SOMI[2]

SOMI[1]

SOMI[0]

Basic Operation

www.ti.com

1526

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Multi-Buffered Serial Peripheral Interface Module (MibSPI) with Parallel Pin

Option (MibSPIP)

Figure 28-29. 8 Pins Parallel Mode Timing Diagram (Phase 0, Polarity 0)

NOTE: Modulo Count Parallel Mode is not supported in this device.

28.2.6.7 MibSPI Slave in Multi-buffer Configuration

When operating in slave mode, the MibSPI uses the chip-select pins 0 to 3 to generate a trigger to the

corresponding Transfer Group. For example, putting 0000 on the chip-select pins triggers Transfer Groups

0 and putting 0001 triggers TG1. When the value 1111 is set to the chip-select, the MibSPI is deselected,

that is Transfer Group 15 is not available in slave mode. The remaining chip-select pins should stay in

GPIO mode. In slave mode, the fields like trigger source and trigger event are not taken into account by

the sequencer. Only the SPICS pins can trigger a Transfer Group. The chip-select trigger operates as a

level-sensitive trigger. However, when the MibSPI is in 3-pin or 4-pin with SPIENA mode, just one

Transfer Group can be triggered and it is restricted to Transfer Group 0 (TG0). In slave mode, the PRST

field should be cleared to 0. If the corresponding Transfer Group is enabled, the multi-buffer reads the

current buffer of the TG and writes it into SPIDAT1. If Transfer Group is disabled, the multi-buffer does not

update the SPIDAT1 register.

NOTE: If the selected Transfer Group is disabled and no update of the SPIDAT1 register has been

done, the data to be transferred is meaningless. Even the received data will not be copied to

the multi-buffer RAM. However it will be available on SPIBUF register until it is overwritten by

the subsequent receive data.

Loading...

Loading...