www.ti.com

Control Registers

1539

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Multi-Buffered Serial Peripheral Interface Module (MibSPI) with Parallel Pin

Option (MibSPIP)

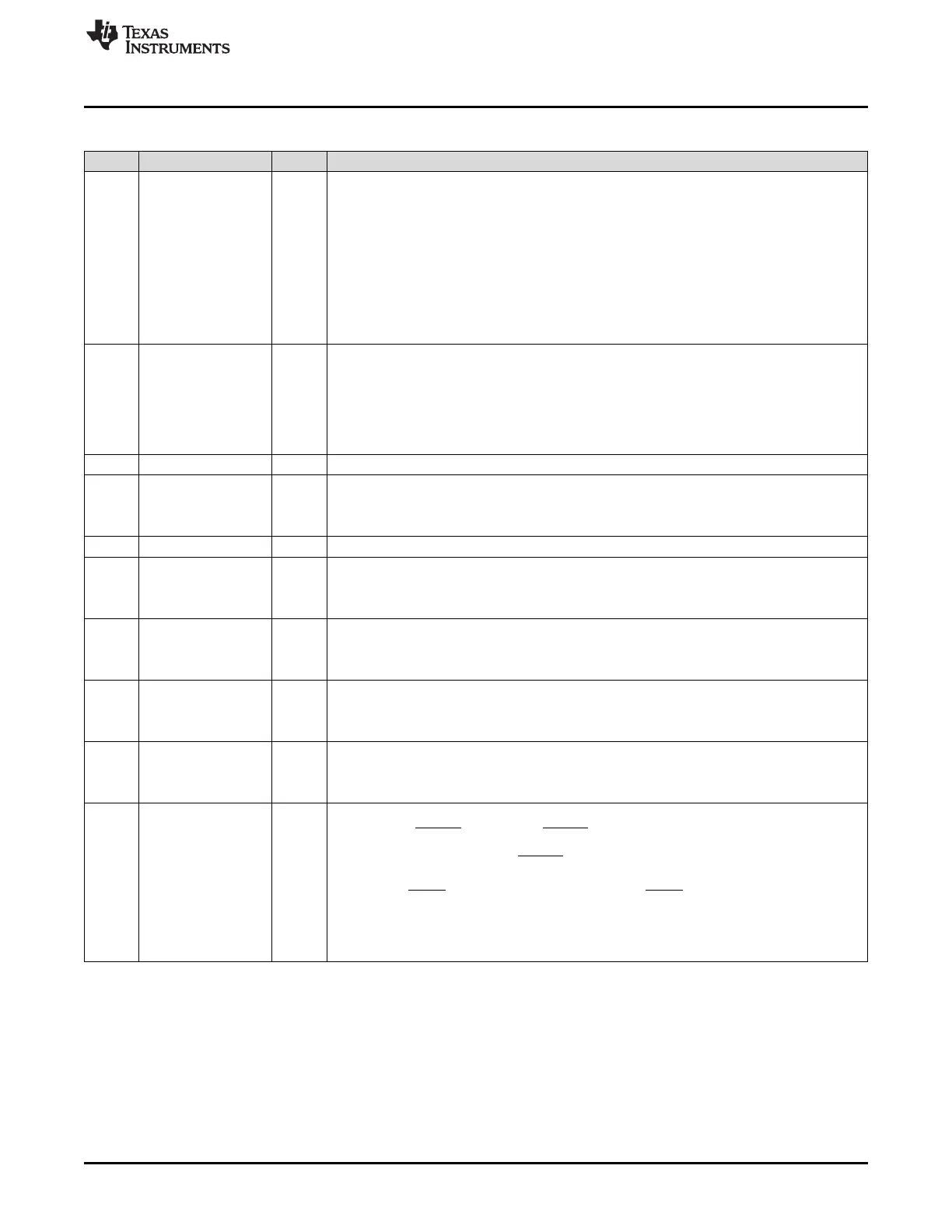

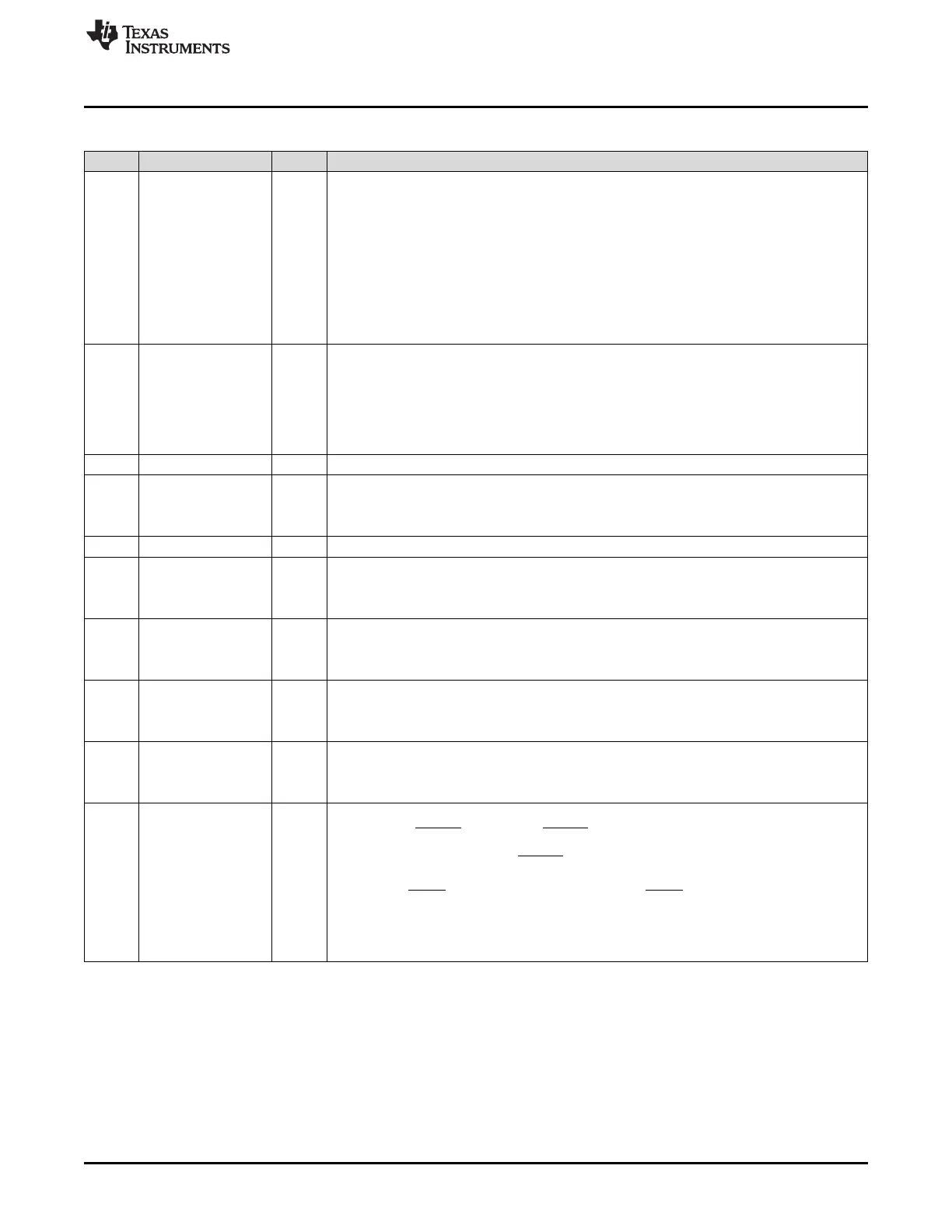

Table 28-11. SPI Interrupt Register (SPIINT0) Field Descriptions (continued)

Bit Field Value Description

9 TXINTENA Causes an interrupt to be generated every time data is written to the shift register, so that the

next word can be written to TXBUF. Setting this bit will generate an interrupt if the TXINTFLG

bit (SPI Flag Register (SPIFLG)[9]) is set to 1.

0 No interrupt will be generated upon TXINTFLG being set to 1.

1 An interrupt will be generated upon TXINTFLG being set to 1.

The transmitter empty interrupt is valid in compatibility mode of SPI only. In multi-buffered

mode, this interrupts will not be generated, even if it is enabled.

Note: An interrupt request will be generated as soon as this bit is set to 1. By default it

will be generated on the INT0 line. The SPILVL register can be programmed to change

the interrupt line.

8 RXINTENA Causes an interrupt to be generated when the RXINTFLAG bit (SPI Flag Register (SPIFLG)[8])

is set by hardware.

0 Interrupt will not be generated.

1 Interrupt will be generated.

The receiver full interrupt is valid in compatibility mode of SPI only. In multi-buffered mode, this

interrupts will not be generated, even if it is enabled.

7 Reserved 0 Reads return 0. Writes have no effect.

6 RXOVRNINTENA Overrun interrupt enable.

0 Overrun interrupt will not be generated.

1 Overrun interrupt will be generated.

5 Reserved 0 Reads return 0. Writes have no effect.

4 BITERRENA Enables interrupt on bit error.

0 No interrupt asserted upon bit error.

1 Enables interrupt on bit error.

3 DESYNCENA Enables interrupt on desynchronized slave. DESYNCENA is used in master mode only.

0 No interrupt asserted upon desynchronization error.

1 An interrupt is asserted on desynchronization of the slave (DESYNC = 1).

2 PARERRENA Enables interrupt-on-parity-error.

0 No interrupt asserted on parity error.

1 An interrupt is asserted on a parity error.

1 TIMEOUTENA Enables interrupt on ENA signal time-out.

0 No interrupt asserted upon ENA signal time-out.

1 An interrupt is asserted on a time-out of the ENA signal.

0 DLENERRENA Data length error interrupt enable. A data length error occurs under the following conditions.

Master: When SPIENA is used, if the SPIENA pin from the slave is deasserted before the

master has completed its transfer, the data length error is set. That is, if the character length

counter has not overflowed while SPIENA deassertion is detected, then it means that the slave

has neither received full data from the master nor has it transmitted complete data.

Slave: When SPICS pins are used, if the incoming valid SPICS pin is deactivated before the

character length counter overflows, then the data length error is set.

0 No interrupt is generated upon data length error.

1 An interrupt is asserted when a data-length error occurs.

Loading...

Loading...