www.ti.com

Control Registers

1553

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Multi-Buffered Serial Peripheral Interface Module (MibSPI) with Parallel Pin

Option (MibSPIP)

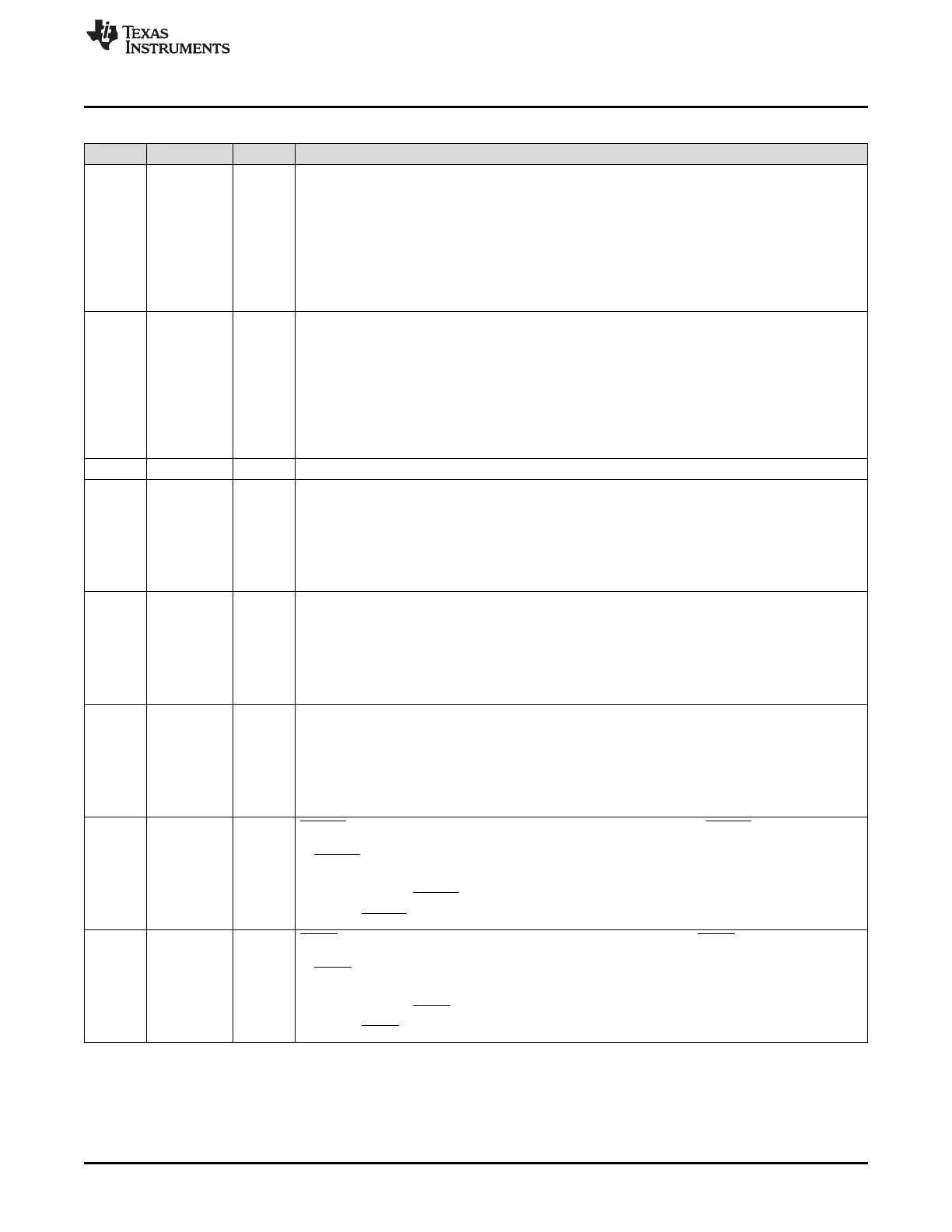

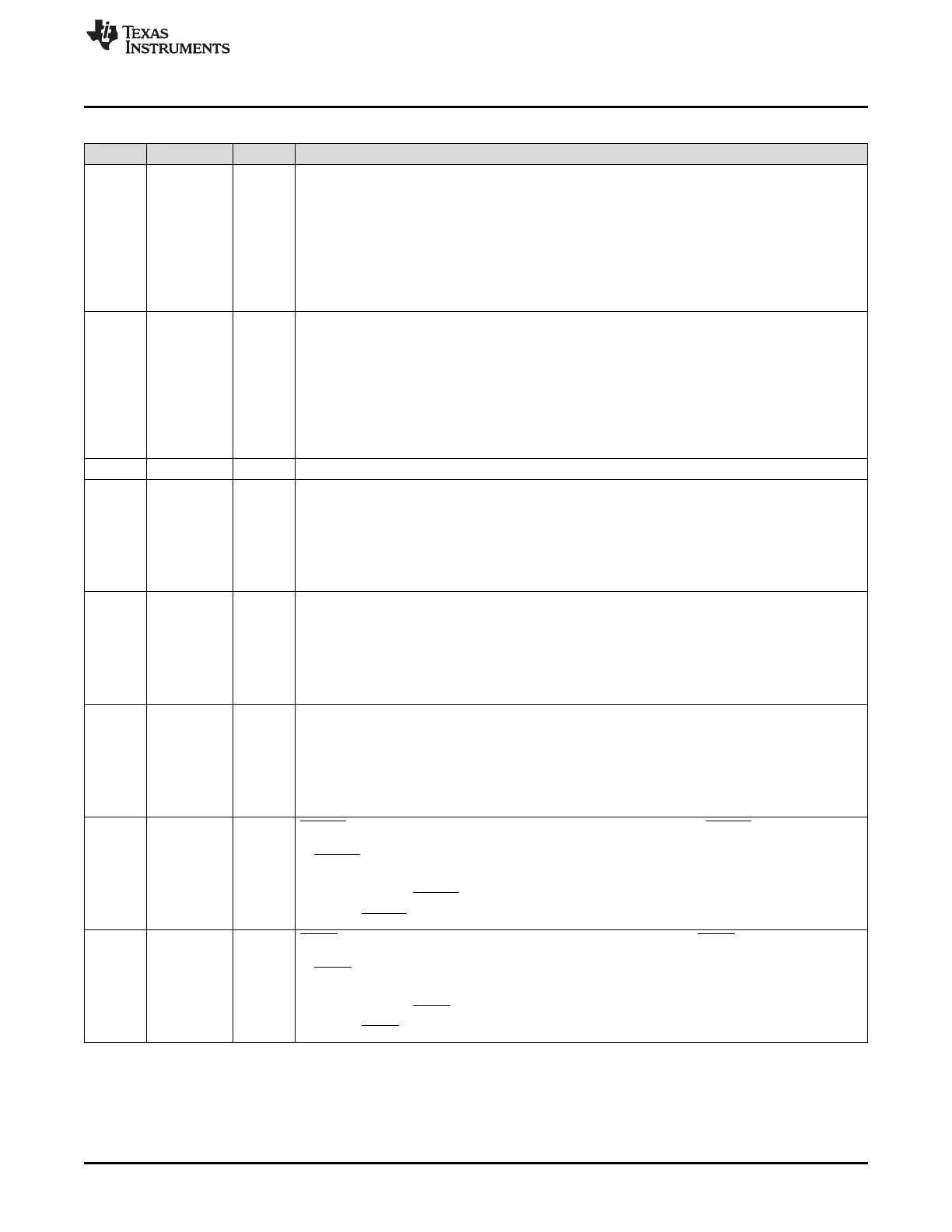

Table 28-20. SPI Pin Control Register 6 (SPIPC6) Field Descriptions

Bit Field Value Description

31-24 SOMIPDR SPISOMIx open drain enable. This bit enables open drain capability for the SPISOMIx pin if the

following conditions are met:

• SOMIDIRx = 1 (SPISOMIx pin configured in GIO mode as an output)

• SOMIDOUTx = 1

Bit 11 or bit 24 can both be used to enable open-drain for SOMI0. If a 32-bit write is performed,

bit 11 will have priority over bit 24.

0 The output value on the SPISOMIx pin is logic 1.

1 Output pin SPISOMIx is in a high-impedance state.

23-16 SIMOPDR SPISIMOx open drain enable. This bit enables open drain capability for the SPISIMOx pin if the

following conditions are met:

• SIMODIRx = 1 (SPISIMOx pin configured in GIO mode as an output)

• SIMODOUTx = 1

Bit 10 or bit 16 can both be used to enable open-drain for SIMO0. If a 32-bit write is performed,

bit 10 will have priority over bit 16.

0 The output value on SPISIMOx pin is logic 1.

1 Output pin SPISIMOx is in a high-impedance state.

15-12 Reserved 0 Reads return 0. Writes have no effect.

11 SOMIPDR0 SOMI0 open-drain enable. This bit enables open-drain capability for SOMI0 if the following conditions

are met.

• SOMI0 pin configured in GIO mode as output pin

• Output value on SPISOMI0 pin is logic 1.

0 Output value 1 of SPISOMI0 pin is logic 1.

1 Output value 1 of SPISOMI0 is high-impedance.

10 SIMOPDR0 SPISIMO0 open-drain enable. This bit enables open -drain capability for the SPISIMO0 pin if the

following conditions are met.

• SIMO0 pin configured in GIO mode as output pin

• Output value on SPISIMO0 pin is logic 1.

0 Output value 1 of SPISIMO0 pin is logic 1.

1 Output value 1 of SPISIMO0 is high-impedance.

9 CLKPDR CLK open drain enable. This bit enables open drain capability for the pin CLK if the following

conditions are met:

• SPICLK pin configured in GIO mode as an output pin

• SPICLKDOUT = 1

0 Output value on CLK pin is logic 1.

1 Output pin CLK is in a high-impedance state.

8 ENAPDR SPIENA open drain enable. This bit enables open drain capability for the SPIENA pin, if the following

conditions are met:

• SPIENA pin configured in GIO mode as an output pin

• SPIENADOUT = 1

0 Output value on the SPIENA pin is logic 1.

1 Output pin SPIENA is in a high-impedance state.

7-0 SCSPDR SPICS open drain enable. This bit enables open drain capability for the SPICS pin, if the following

conditions are met:

• SPICS pin configured in GIO mode as an output pin

• SCSDOUT = 1

0 Output value on the SPICS pin is logic 1.

1 Output pin SPICS is in a high-impedance state.

Loading...

Loading...