www.ti.com

System and Peripheral Control Registers

201

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

2.5.1.48 Global Status Register (GLBSTAT)

The GLBSTAT register, shown in Figure 2-55 and described in Table 2-67, indicates the FMzPLL (PLL1)

slip status and the oscillator fail status.

NOTE: PLL and OSC fail behavior

The device behavior after a PLL slip or an oscillator failure is configured in the PLLCTL1

register.

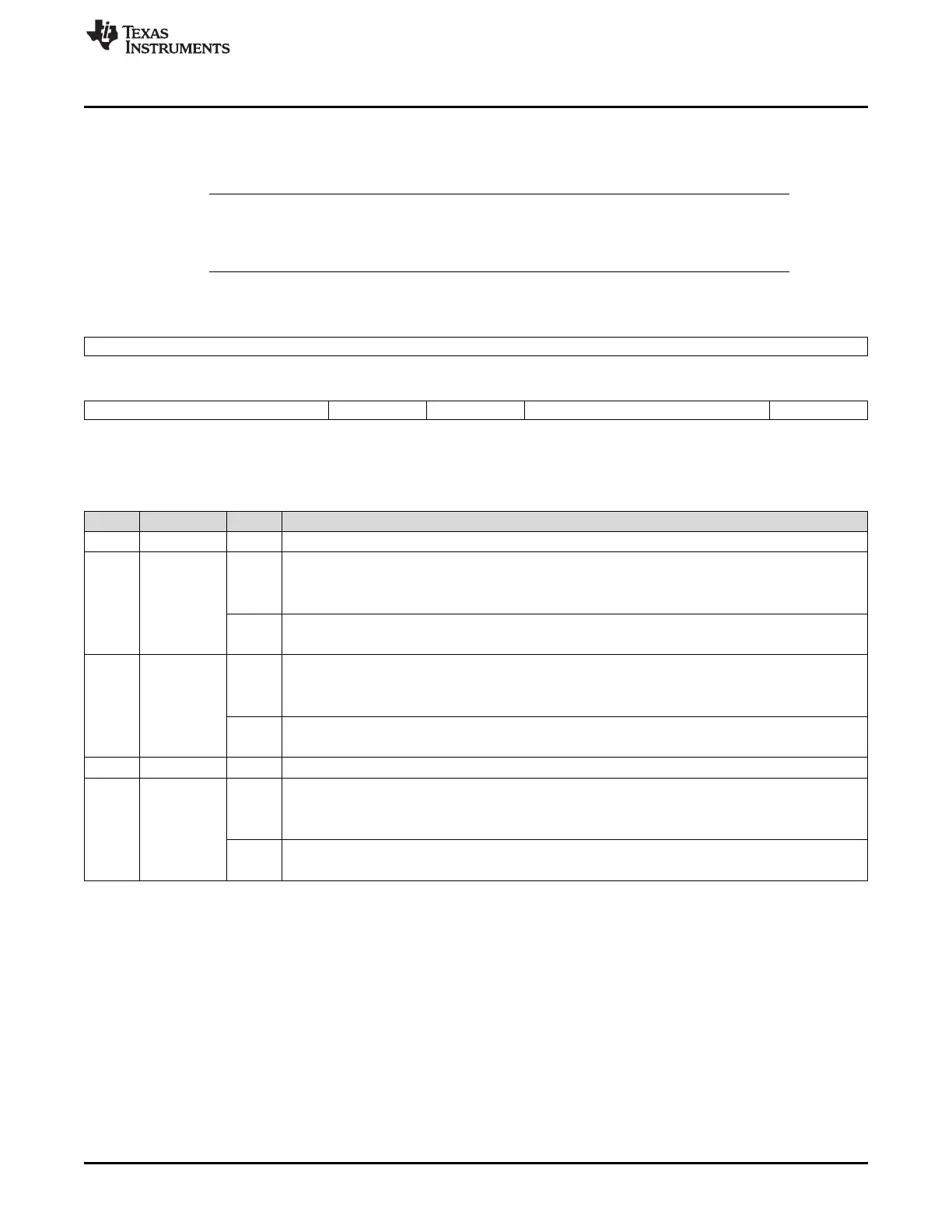

Figure 2-55. Global Status Register (GLBSTAT) (offset = ECh)

31 16

Reserved

R-0

15 10 9 8 7 1 0

Reserved FBSLIP RFSLIP Reserved OSCFAIL

R-0 R/W1C-n R/W1C-n R-0 R/W1C-n

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to Clear; -n = value after reset

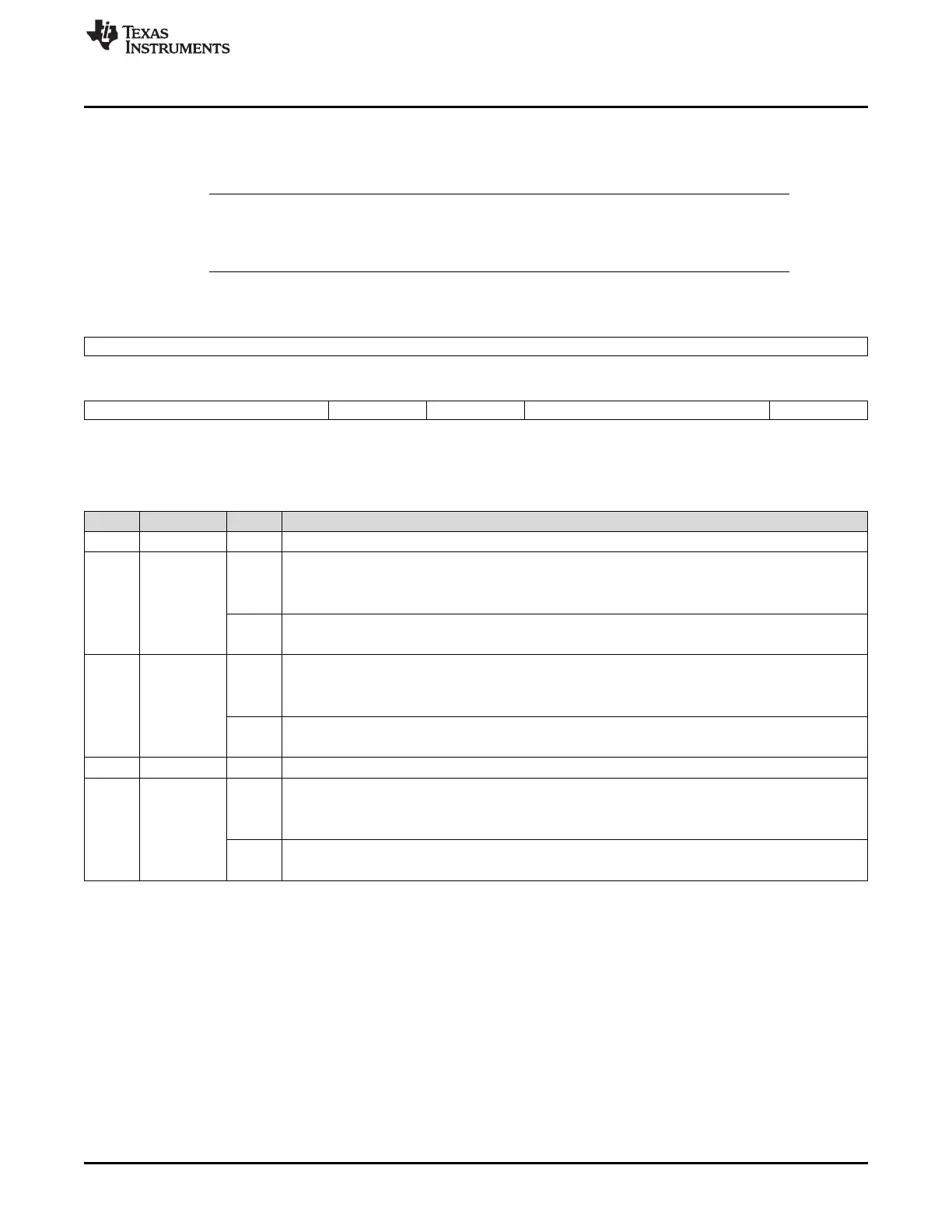

Table 2-67. Global Status Register (GLBSTAT) Field Descriptions

Bit Field Value Description

31-10 Reserved 0 Reads return 0. Writes have no effect.

9 FBSLIP PLL over cycle slip detection. (cleared by nPORRST, maintains its previous value for all other resets).

0 Read: No PLL over cycle slip has been detected.

Write: The bit is unchanged.

1 Read: A PLL over cycle slip has been detected.

Write: The bit is cleared to 0.

8 RFSLIP PLL under cycle slip detection. (cleared by nPORRST, maintains its previous value for all other resets).

0 Read: No PLL under cycle slip has been detected.

Write: The bit is unchanged.

1 Read: A PLL under cycle slip has been detected.

Write: The bit is cleared to 0.

7-1 Reserved 0 Reads return 0. Writes have no effect.

0 OSCFAIL Oscillator fail flag bit. (cleared by nPORRST, maintains its previous value for all other resets).

0 Read: No oscillator failure has been detected.

Write: The bit is unchanged.

1 Read: An oscillator failure has been detected.

Write: The bit is cleared to 0.

Loading...

Loading...