www.ti.com

ePWM Registers

2101

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Enhanced Pulse Width Modulator (ePWM) Module

35.4.8 Digital Compare Submodule Registers

35.4.8.1 Digital Compare A Control Register (DCACTL)

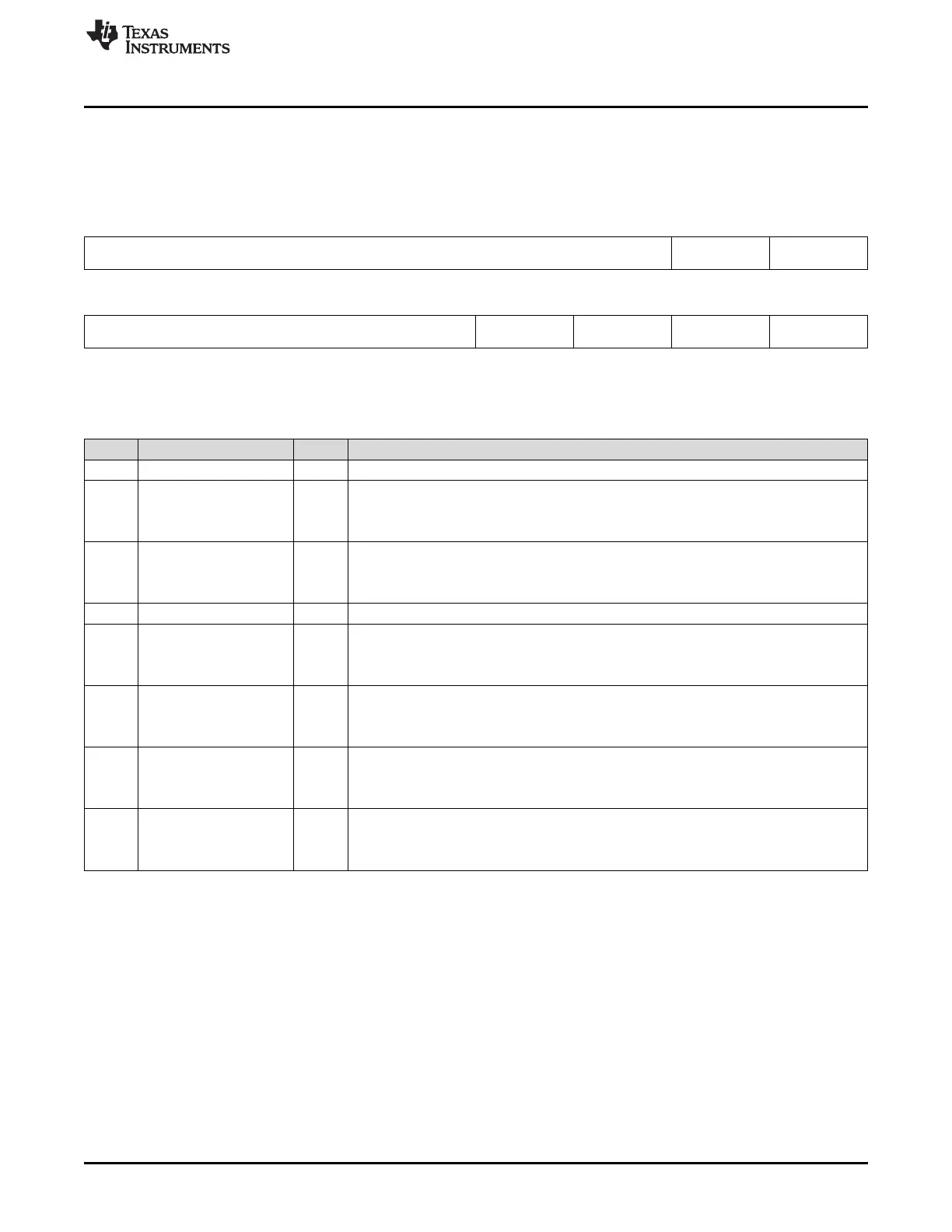

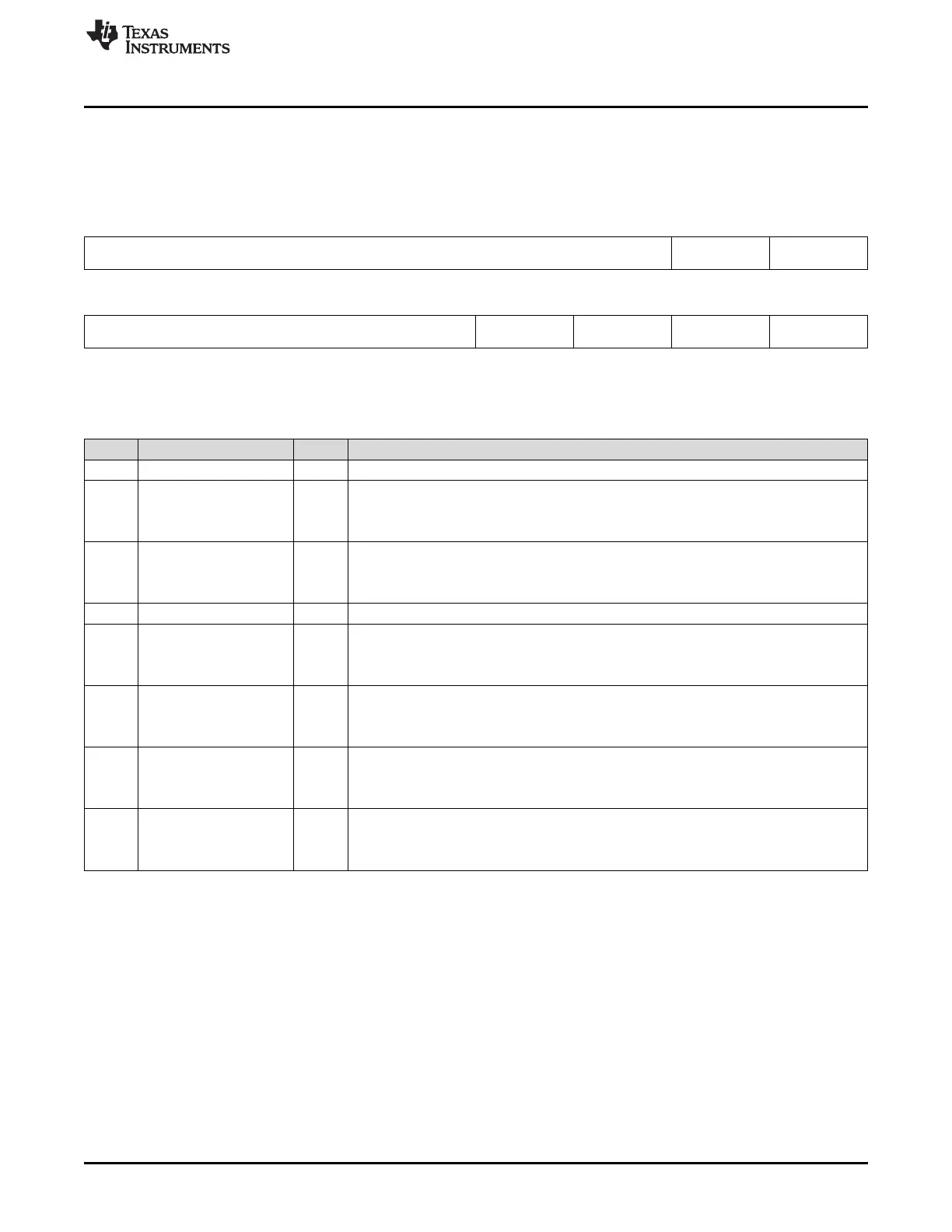

Figure 35-91. Digital Compare A Control Register (DCACTL) [offset = 60h]

15 10 9 8

Reserved EVT2FRC

SYNCSEL

EVT2SRCSEL

R-0 R/W-0 R/W-0

7 4 3 2 1 0

Reserved EVT1SYNCE EVT1SOCE EVT1FRC

SYNCSEL

EVT1SRCSEL

R-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 35-51. Digital Compare A Control Register (DCACTL) Field Descriptions

Bit Field Value Description

15-10 Reserved 0 Reserved

9 EVT2FRC SYNCSEL DCAEVT2 Force Synchronization Signal Select.

0 Source Is Synchronous Signal.

1 Source Is Asynchronous Signal.

8 EVT2SRCSEL DCAEVT2 Source Signal Select.

0 Source Is DCAEVT2 Signal.

1 Source Is DCEVTFILT Signal.

7-4 Reserved 0 Reserved

3 EVT1SYNCE DCAEVT1 SYNC Enable.

0 SYNC Generation is disabled.

1 SYNC Generation is enabled.

2 EVT1SOCE DCAEVT1 SOC Enable.

0 SOC Generation is disabled.

1 SOC Generation is enabled .

1 EVT1FRC SYNCSEL DCAEVT1 Force Synchronization Signal Select.

0 Source Is Synchronous Signal.

1 Source Is Asynchronous Signal.

0 EVT1SRCSEL DCAEVT1 Source Signal Select.

0 Source Is DCAEVT1 Signal.

1 Source Is DCEVTFILT Signal.

Loading...

Loading...