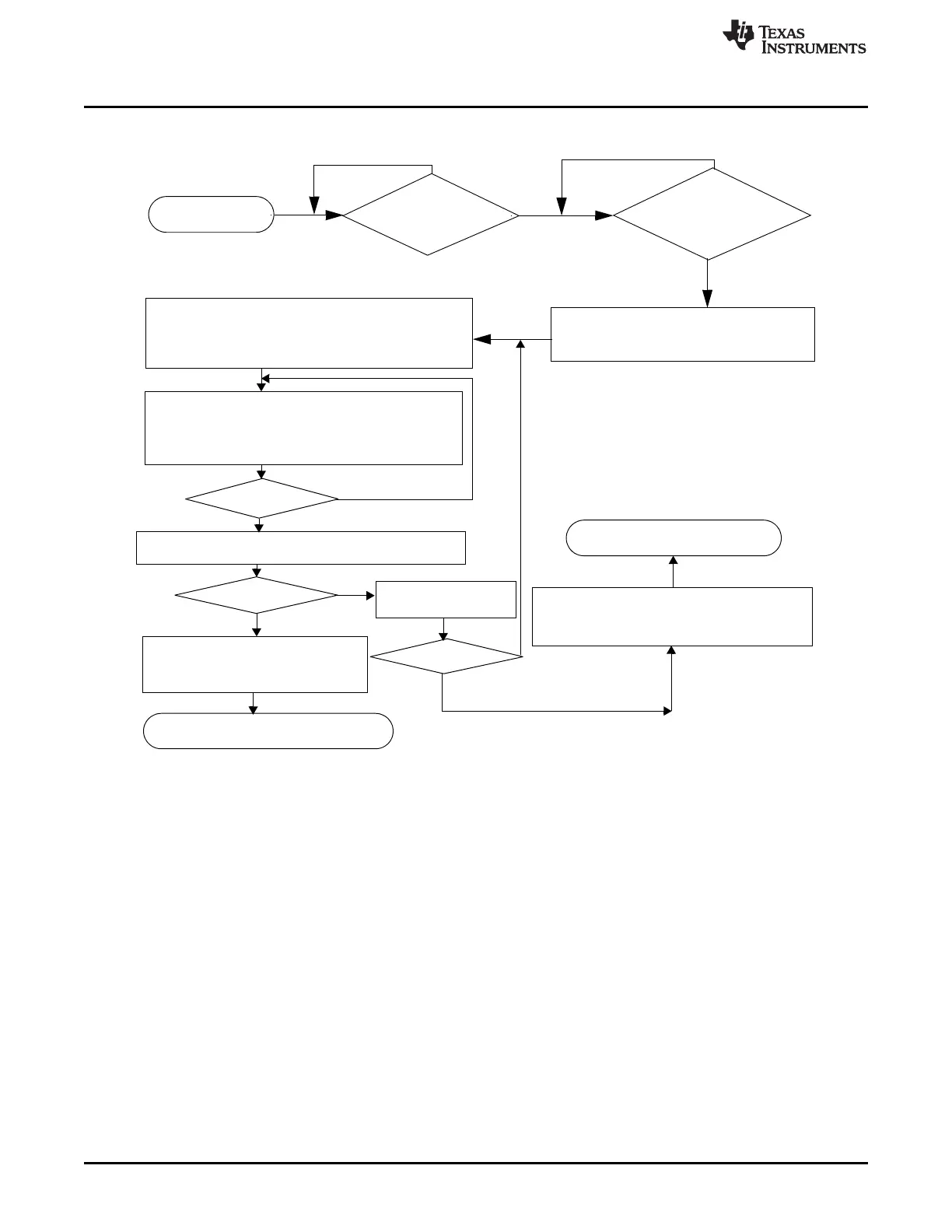

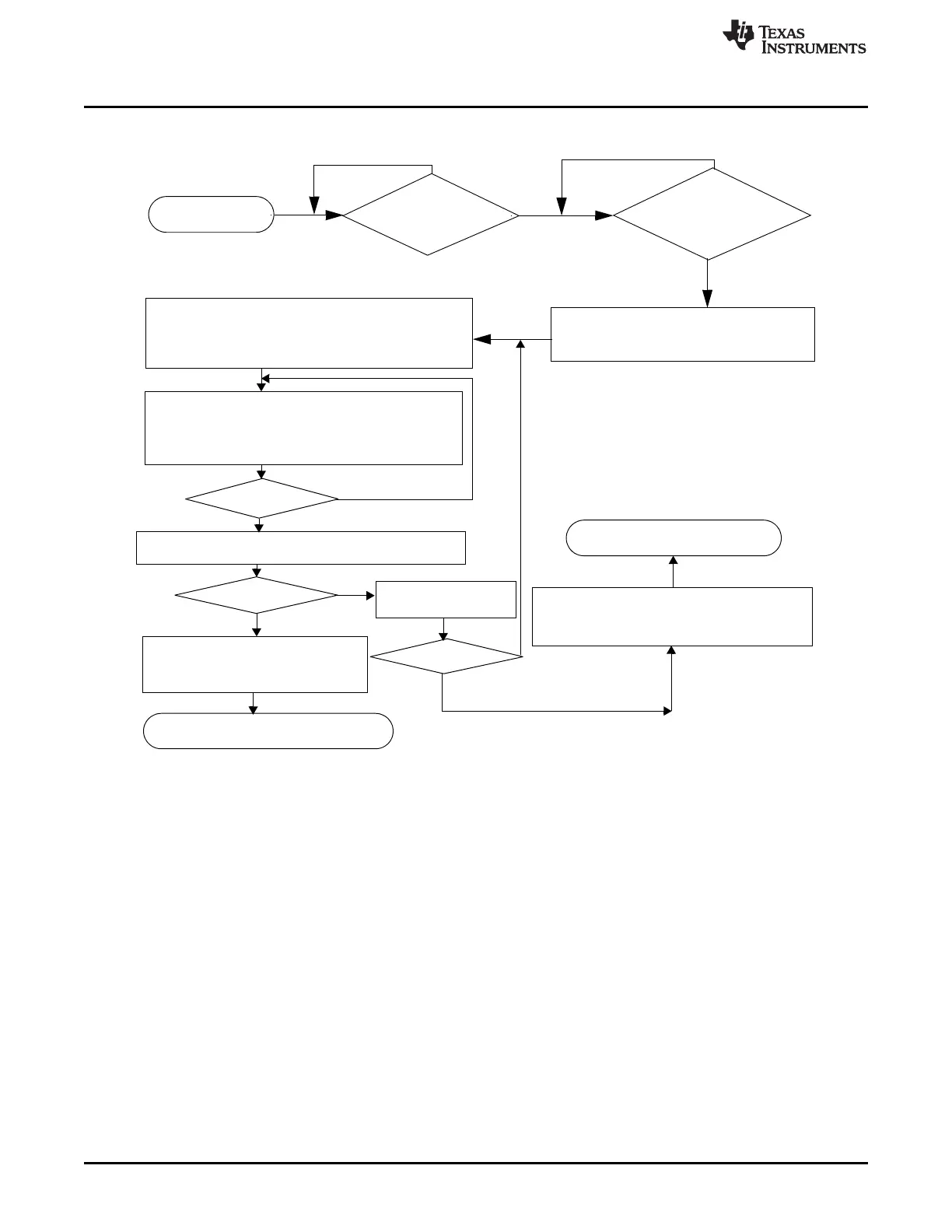

NO

YES

YES

misr mismatch?

Increment CICR

NO

YES

NO

Intervals done

YES

YES

Start

NO

NO

Has the segment

or core/ip under test asserted

its idle state acknowledge

signal

The STC reads the MICRO code from ROM

and saves the seed_cntrl_data and Gloden

MISR for the next interval (CICR + 1)

(CICR is 0 for the first time selftest run);

The STC reads the seed_data into buffers

based on seed_cntrl_bits generate DBIST

control signals and shift the seed through

shadow_si ports of DBIT

Read the MISR value into STC from the dbist,

to compare with Golden MISR

The STC enable forces the CPU bus

to idle transaction mode

Is Self Test

Enabled?

All patterns

completed?

End of Self Test

(Disable the STC_ENA Key)

The STC Updates the STC status registers

and generates CPU reset and stc_testerr_o

End of Self Test

(Disable the STC_ENA Key)

Set the STC complete flag in the

STC status registers.

STC asserts the CPU reset

Loading...

Loading...