RTI Control Registers

www.ti.com

616

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Real-Time Interrupt (RTI) Module

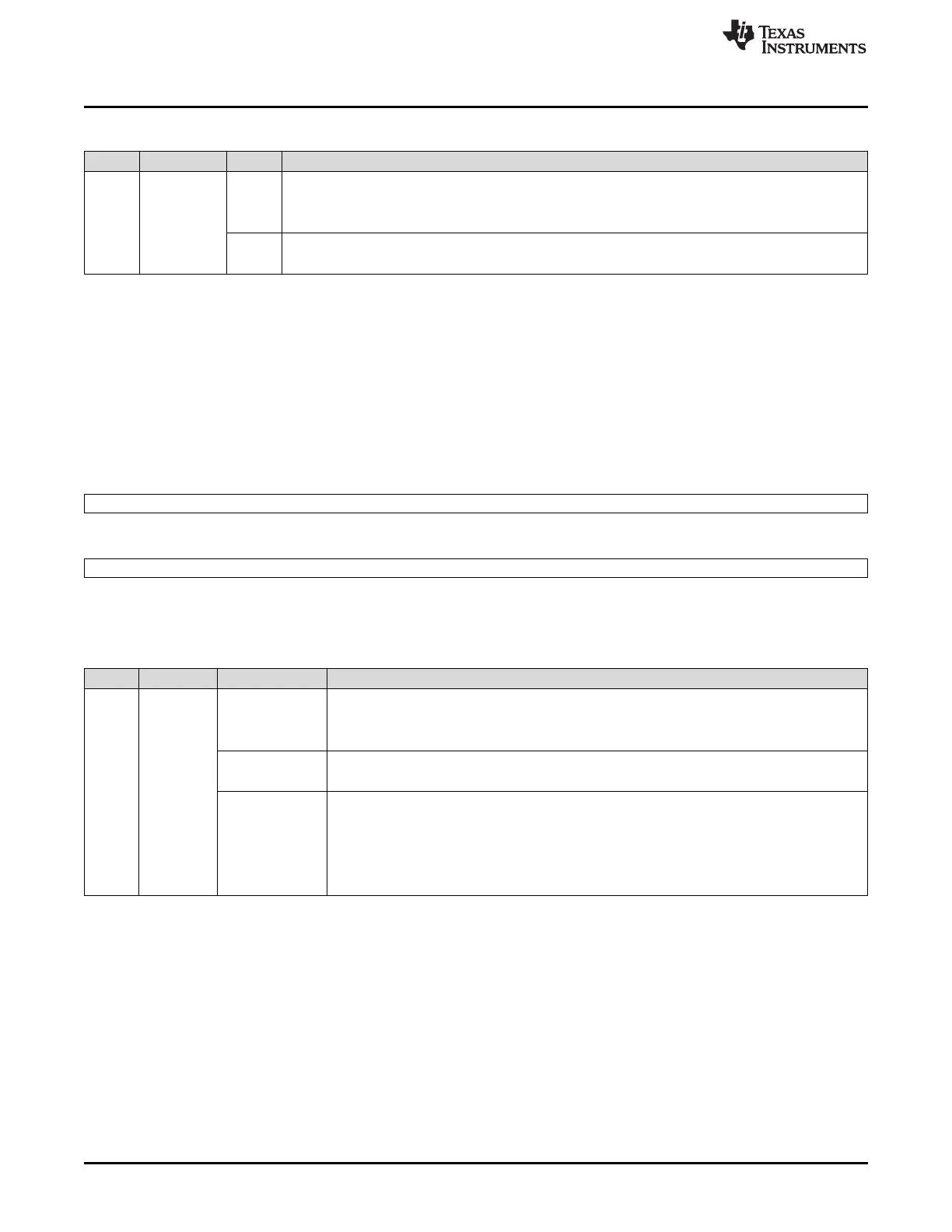

Table 17-28. RTI Interrupt Flag Register (RTIINTFLAG) Field Descriptions (continued)

Bit Field Value Description

0 INT0 Interrupt flag 0. These bits determine if an interrupt due to a Compare 0 match is pending.

0 Read: No interrupt is pending.

Write: Bit is unchanged.

1 Read: Interrupt is pending.

Write: Bit is cleared to 0.

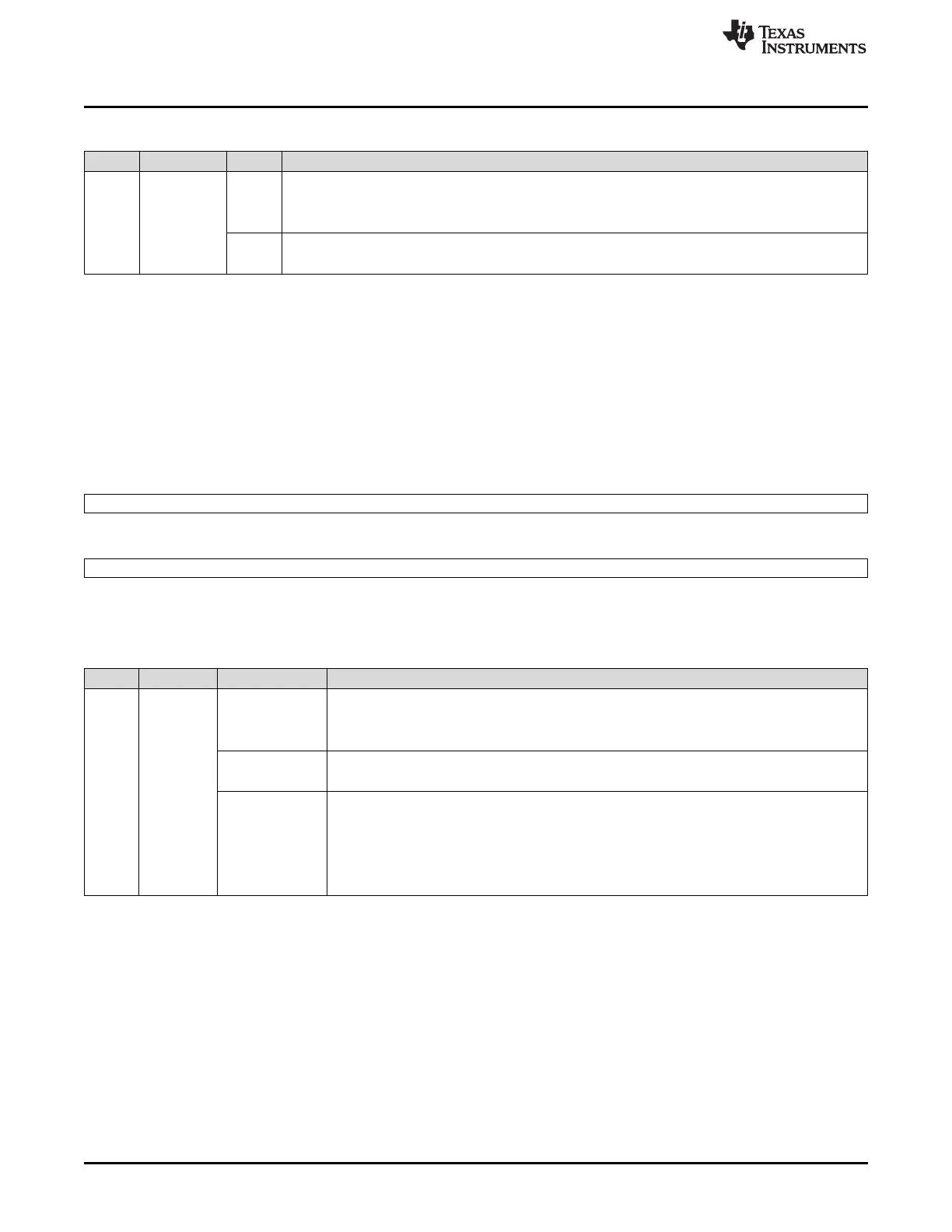

17.3.28 Digital Watchdog Control Register (RTIDWDCTRL)

The software has to write to the DWDCTRL field in order to enable the DWD, as described below. Once

enabled, the watchdog can only be disabled by a system reset. The application cannot disable the

watchdog. However should the RTICLK source be changed to a source that is unimplemented it will have

the same effect as disabling the watchdog. This register is shown in Figure 17-38 and described in

Table 17-28.

Figure 17-39. Digital Watchdog Control Register (RTIDWDCTRL) [offset = 90h]

31 16

DWDCTRL

R/WP-5312h

15 0

DWDCTRL

R/WP-ACEDh

LEGEND: R/W = Read/Write; WP = Write in privileged mode only; -n = value after reset

Table 17-29. Digital Watchdog Control Register (RTIDWDCTRL) Field Descriptions

Bit Field Value Description

31-0 DWDCTRL Digital Watchdog Control.

5312 ACEDh Read: DWD counter is disabled.

Write: State of DWD counter is unchanged (stays enabled or disabled).

A985 59DAh Read: DWD counter is enabled.

Write: DWD counter is enabled.

All other values Read: DWD counter state is unchanged (enabled or disabled).

Write: State of DWD counter is unchanged (stays enabled or disabled).

Note: Once the enable value is written, all other future writes are blocked. In other words, once

DWD is enabled, it can only be disabled by system reset or power on reset. However should

the RTICLK source be changed to a source that is unimplemented it will have the same effect

as disabling the watchdog.

Loading...

Loading...