www.ti.com

VIM Control Registers

695

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Vectored Interrupt Manager (VIM) Module

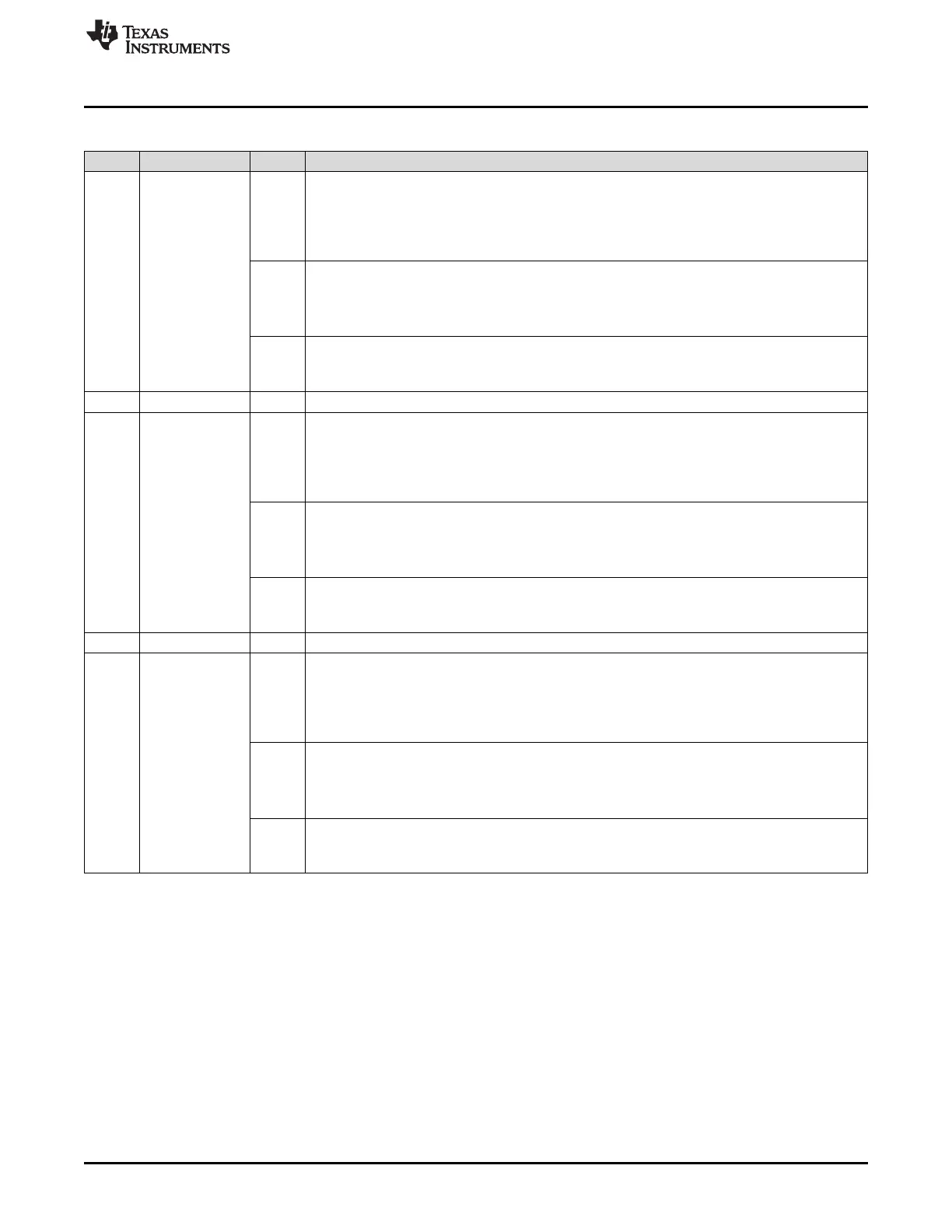

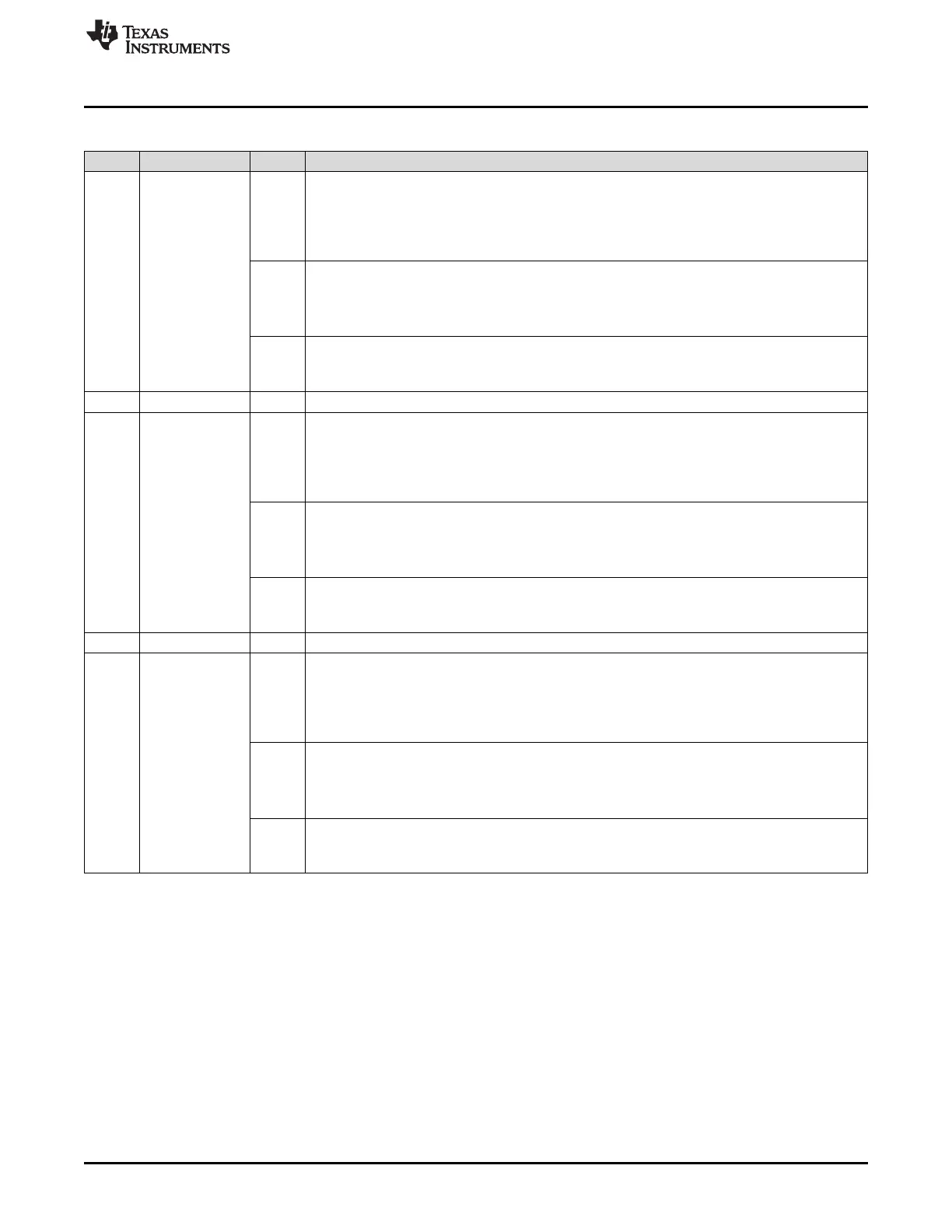

Table 19-24. Interrupt Control Registers (CHANCTRL[0:31]) Field Descriptions (continued)

Bit Field Value Description

22-16 CHANMAPx

1

CHANMAPx

1

(6-0). Interrupt CHANx

1

mapping control. These bits determine which interrupt request

the priority channel CHANx

1

maps to:

0 Read: Interrupt request 0 maps to channel priority CHANx

1

.

Write: The default value of this bit after reset is given in Table 19-23. The channel priority CHANx

1

is set with the interrupt request.

1h Read: Interrupt request 1 maps to channel priority CHANx

1

.

Write: The default value of this bit after reset is given in Table 19-23. The channel priority CHANx

1

is set with the interrupt request.

: :

7Fh Read: Interrupt request 127 maps to channel priority CHANx

1

.

Write: The default value of this bit after reset is given in Table 19-23. The channel priority CHANx

1

is set with the interrupt request.

15 Reserved 0 Reads are indeterminate and writes have no effect.

14-8 CHANMAPx

2

CHANMAPx

2

(6-0). Interrupt CHANx

2

mapping control. These bits determine which interrupt request

the priority channel CHANx

2

maps to:

0 Read: Interrupt request 0 maps to channel priority CHANx

2

.

Write: The default value of this bit after reset is given in Table 19-23. The channel priority CHANx

2

is set with the interrupt request.

1h Read: Interrupt request 1 maps to channel priority CHANx

2

.

Write: The default value of this bit after reset is given in Table 19-23. The channel priority CHANx

2

is set with the interrupt request.

: :

7Fh Read: Interrupt request 127 maps to channel priority CHANx

2

.

Write: The default value of this bit after reset is given in Table 19-23. The channel priority CHANx

2

is set with the interrupt request.

7 Reserved 0 Reads are indeterminate and writes have no effect.

6-0 CHANMAPx

3

CHANMAPx

3

(6-0). Interrupt CHANx

3

mapping control. These bits determine which interrupt request

the priority channel CHANx

3

maps to:

0 Read: Interrupt request 0 maps to channel priority CHANx

3

.

Write: The default value of this bit after reset is given in Table 19-23. The channel priority CHANx

3

is set with the interrupt request.

1h Read: Interrupt request 1 maps to channel priority CHANx

3

.

Write: The default value of this bit after reset is given in Table 19-23. The channel priority CHANx

3

is set with the interrupt request.

: :

7Fh Read: Interrupt request 127 maps to channel priority CHANx

3

.

Write: The default value of this bit after reset is given in Table 19-23. The channel priority CHANx

3

is set with the interrupt request.

Loading...

Loading...