www.ti.com

Module Operation

711

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Direct Memory Access Controller (DMA) Module

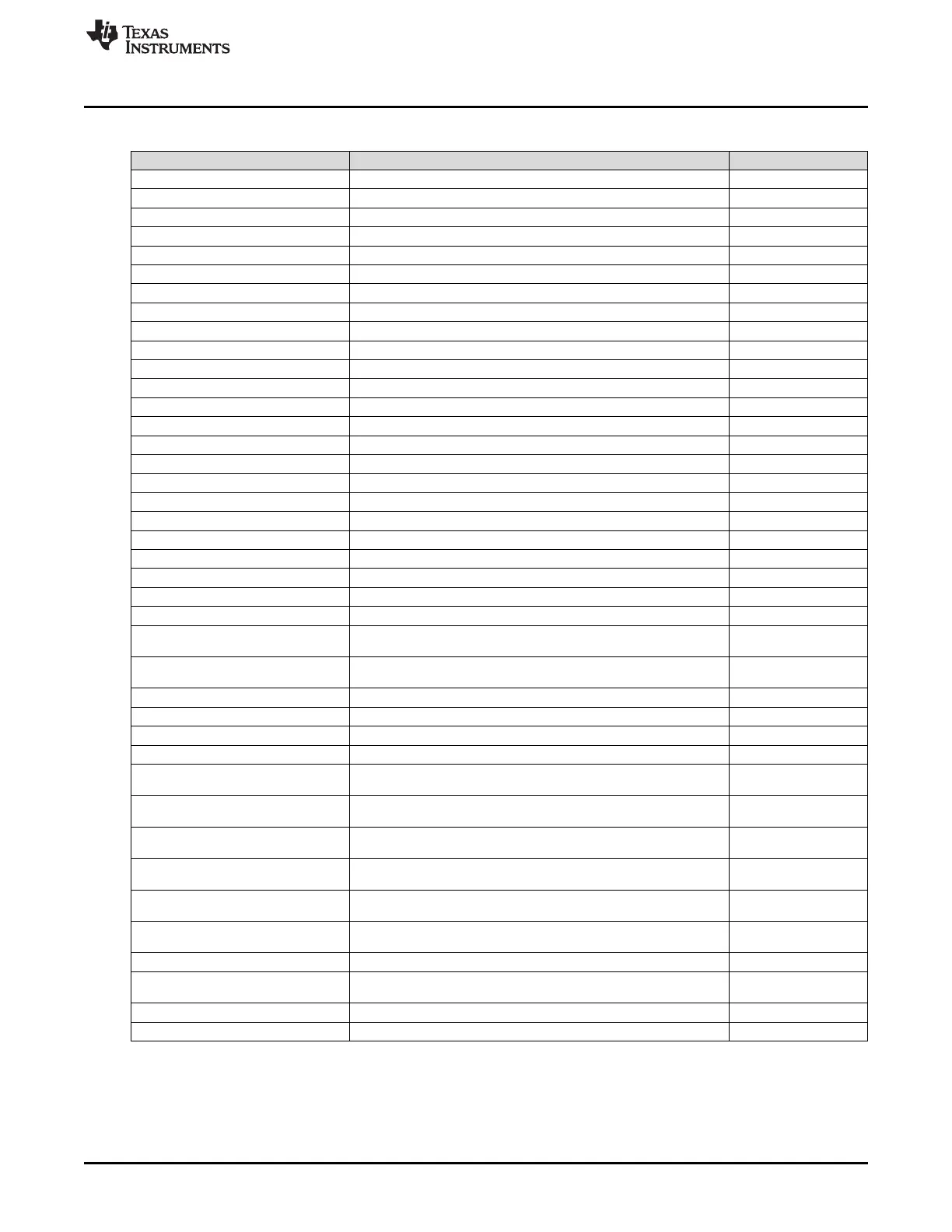

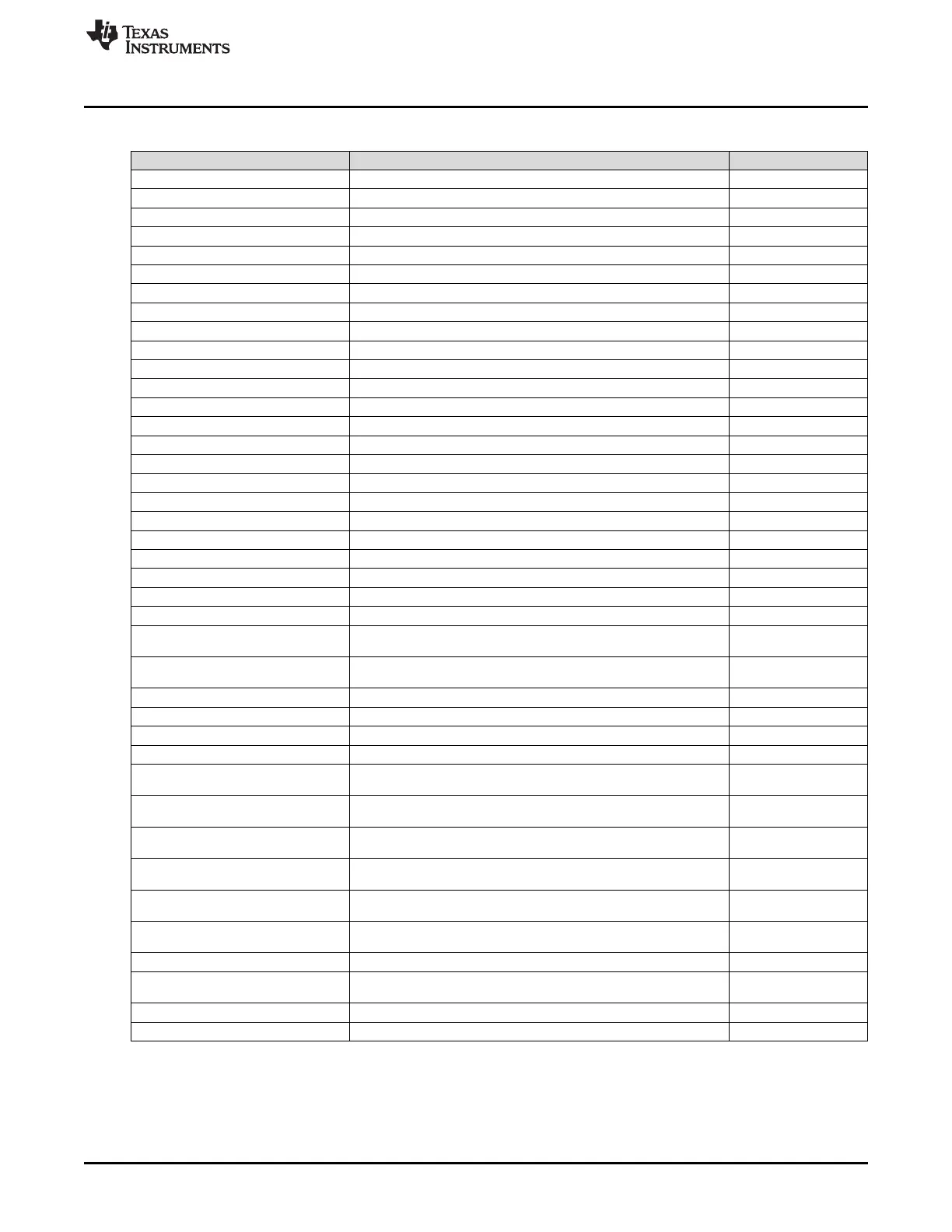

Table 20-3. DMA Request Line Connection (continued)

Modules DMA Request Sources DMA Request

MIBSPI1 / MIBSPI3 / DCAN1 MIBSPI1[4] / MIBSPI3[4] / DCAN1 IF1 DMAREQ[8]

MIBSPI1 / MIBSPI3 / DCAN2 MIBSPI1[5] / MIBSPI3[5] / DCAN2 IF1 DMAREQ[9]

MIBADC1 / I2C / MIBSPI5 MIBADC1 G1 / I2C receive / MIBSPI5[4] DMAREQ[10]

MIBADC1 / I2C / MIBSPI5 MIBADC1 G2 / I2C transmit / MIBSPI5[5] DMAREQ[11]

RTI / MIBSPI1 / MIBSPI3 RTI DMAREQ0 / MIBSPI1[6] / MIBSPI3[6] DMAREQ[12]

RTI / MIBSPI1 / MIBSPI3 RTI DMAREQ1 / MIBSPI1[7] / MIBSPI3[7] DMAREQ[13]

MIBSPI3 / MibADC2 / MIBSPI5 MIBSPI3[1]

(1)

/ MibADC2 event / MIBSPI5[6] DMAREQ[14]

MIBSPI3 / MIBSPI5 MIBSPI3[0]

(2)

/ MIBSPI5[7] DMAREQ[15]

MIBSPI1 / MIBSPI3 / DCAN1 / MibADC2 MIBSPI1[8] / MIBSPI3[8] / DCAN1 IF3 / MibADC2 G1 DMAREQ[16]

MIBSPI1 / MIBSPI3 / DCAN3 / MibADC2 MIBSPI1[9] / MIBSPI3[9] / DCAN3 IF1 / MibADC2 G2 DMAREQ[17]

RTI / MIBSPI5 RTI DMAREQ2 / MIBSPI5[8] DMAREQ[18]

RTI / MIBSPI5 RTI DMAREQ3 / MIBSPI5[9] DMAREQ[19]

NHET1 / NHET2 / DCAN3 NHET1 DMAREQ[4] / NHET2 DMAREQ[4] / DCAN3 IF2 DMAREQ[20]

NHET1 / NHET2 / DCAN3 NHET1 DMAREQ[5] / NHET2 DMAREQ[5] / DCAN3 IF3 DMAREQ[21]

MIBSPI1 / MIBSPI3 / MIBSPI5 MIBSPI1[10] / MIBSPI3[10] / MIBSPI5[10] DMAREQ[22]

MIBSPI1 / MIBSPI3 / MIBSPI5 MIBSPI1[11] / MIBSPI3[11] / MIBSPI5[11] DMAREQ[23]

NHET1 / NHET2 / MIBSPI4 / MIBSPI5 NHET1 DMAREQ[6] / NHET2 DMAREQ[6] / MIBSPI4[1]

(1)

/ MIBSPI5[12] DMAREQ[24]

NHET1 / NHET2 / MIBSPI4 / MIBSPI5 NHET1 DMAREQ[7] / NHET2 DMAREQ[7] / MIBSPI4[0]

(2)

/ MIBSPI5[13] DMAREQ[25]

CRC1 / MIBSPI1 / MIBSPI3 CRC1 DMAREQ[0] / MIBSPI1[12] / MIBSPI3[12] DMAREQ[26]

CRC1 / MIBSPI1 / MIBSPI3 CRC1 DMAREQ[1] / MIBSPI1[13] / MIBSPI3[13] DMAREQ[27]

LIN1 / MIBSPI5 LIN1 receive / MIBSPI5[14] DMAREQ[28]

LIN1 / MIBSPI5 LIN1 transmit / MIBSPI5[15] DMAREQ[29]

MIBSPI1 / MIBSPI3 / SCI3 / MIBSPI5 MIBSPI1[14] / MIBSPI3[14] / SCI3 receive / MIBSPI5[1]

(1)

DMAREQ[30]

MIBSPI1 / MIBSPI3 / SCI3 / MIBSPI5 MIBSPI1[15] / MIBSPI3[15] / SCI3 transmit / MIBSPI5[0]

(2)

DMAREQ[31]

I2C2 / ePWM1 / MIBSPI2 / MIBSPI4 /

GIOA

I2C2 receive / ePWM1_SOCA / MIBSPI2[2] / MIBSPI4[2] / GIOA[0] DMAREQ[32]

I2C2 / ePWM 1 / MIBSPI2 / MIBSPI4 /

GIOA

I2C2 transmit / ePWM1_SOCB / MIBSPI2[3] / MIBSPI4[3] /GIOA[1] DMAREQ[33]

ePWM2 / MIBSPI2 / MIBSPI4 / GIOA ePWM2_SOCA / MIBSPI2[4] / MIBSPI4[4] / GIOA[2] DMAREQ[34]

ePWM2 / MIBSPI2 / MIBSPI4 / GIOA ePWM2_SOCB / MIBSPI2[5] / MIBSPI4[5] / GIOA[3] DMAREQ[35]

ePWM3 / MIBSPI2 / MIBSPI4 / GIOA ePWM3_SOCA / MIBSPI2[6] / MIBSPI4[6] / GIOA[4] DMAREQ[36]

ePWM3 / MIBSPI2 / MIBSPI4 / GIOA ePWM3_SOCB / MIBSPI2[7] / MIBSPI4[7] / GIOA[5] DMAREQ[37]

CRC2 / ePWM4 / MIBSPI2 / MIBSPI4 /

GIOA

CRC2 DMAREQ[0] / ePWM4_SOCA / MIBSPI2[8] / MIBSPI4[8] / GIOA[6] DMAREQ[38]

CRC2 / ePWM4 / MIBSPI2 / MIBSPI4

/GIOA

CRC2 DMAREQ[1] / ePWM4_SOCB / MIBSPI2[9] / MIBSPI4[9] / GIOA[7] DMAREQ[39]

LIN2 / ePWM5 / MIBSPI2 / MIBSPI4 /

GIOB

LIN2 receive / ePWM5_SOCA / MIBSPI2[10] / MIBSPI4[10] / GIOB[0] DMAREQ[40]

LIN2 / ePWM5 / MIBSPI2 / MIBSPI4 /

GIOB

LIN2 transmit / ePWM5_SOCB / MIBSPI2[11] / MIBSPI4[11] / GIOB[1] DMAREQ[41]

SCI4 / ePWM6 / MIBSPI2 / MIBSPI4 /

GIOB

SCI4 receive / ePWM6_SOCA / MIBSPI2[12] / MIBSPI4[12] / GIOB[2] DMAREQ[42]

SCI4 / ePWM6 / MIBSPI2 / MIBSPI4 /

GIOB

SCI4 transmit / ePWM6_SOCB / MIBSPI2[13] / MIBSPI4[13] / GIOB[3] DMAREQ[43]

ePWM7 / MIBSPI2 / MIBSPI4 / GIOB ePWM7_SOCA / MIBSPI2[14] / MIBSPI4[14] / GIOB[4] DMAREQ[44]

ePWM7 / MIBSPI2 / MIBSPI4 / GIOB /

DCAN4

ePWM7_SOCB / MIBSPI2[15] / MIBSPI4[15] / GIOB[5] / DCAN4 IF1 DMAREQ[45]

GIOB / DCAN4 GIOB[6] / DCAN4_IF2 DMAREQ[46]

GIOB / DCAN4 GIOB[7] / DCAN4_IF3 DMAREQ[47]

Loading...

Loading...