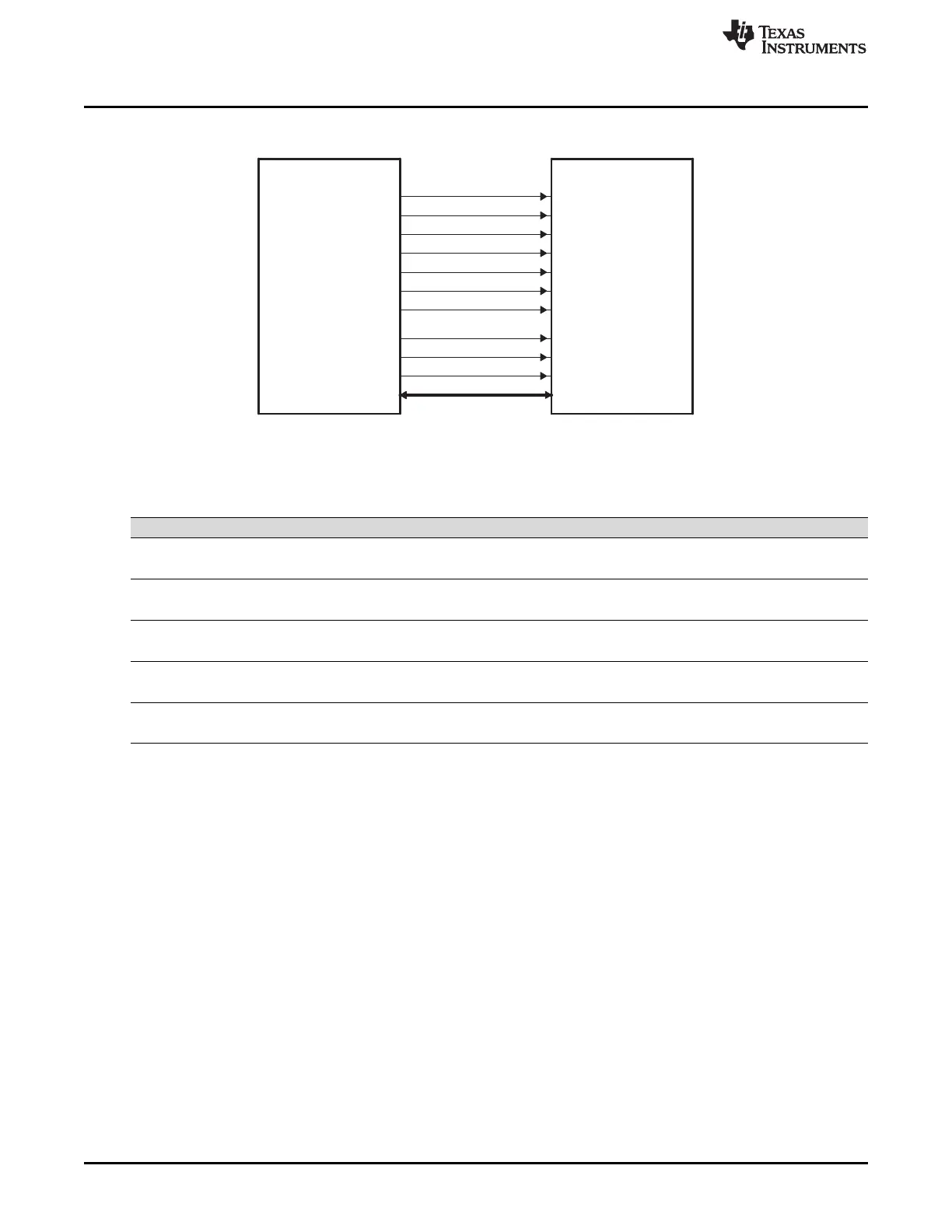

EMIF_nCS[0]

EMIF_nCAS

EMIF_nRAS

EMIF_nWE

EMIF_CLK

EMIF_CKE

EMIF_BA[0]

EMIF_A[10:0]

EMIF_nDQM[0]

EMIF_nDQM[1]

EMIF_D[15:0]

EMIF

nCE

nCAS

nRAS

nWE

CLK

CKE

BA[0]

A[10:0]

LDQM

UDQM

DQ[15:0]

SDRAM

512 x 16

x 2 bank

EMIF Module Architecture

www.ti.com

800

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

External Memory Interface (EMIF)

Figure 21-4. EMIF to 512K × 16 × 2 bank SDRAM Interface

Table 21-6. 16-bit EMIF Address Pin Connections

SDRAM Size Width Banks Device Address Pins

16M bits ×16 2 SDRAM A[10:0]

EMIF EMIF_A[10:0]

64M bits ×16 4 SDRAM A[11:0]

EMIF EMIF_A[11:0]

128M bits ×16 4 SDRAM A[11:0]

EMIF EMIF_A[11:0]

256M bits x16 4 SDRAM A[12:0]

EMIF EMIF_A[12:0]

512M bits x16 4 SDRAM A[12:0]

EMIF EMIF_A[12:0]

Loading...

Loading...