TC1796

Peripheral Units (Vol. 2 of 2)

General Purpose Timer Array (GPTA)

User’s Manual 24-151 V2.0, 2007-07

GPTA, V2.0

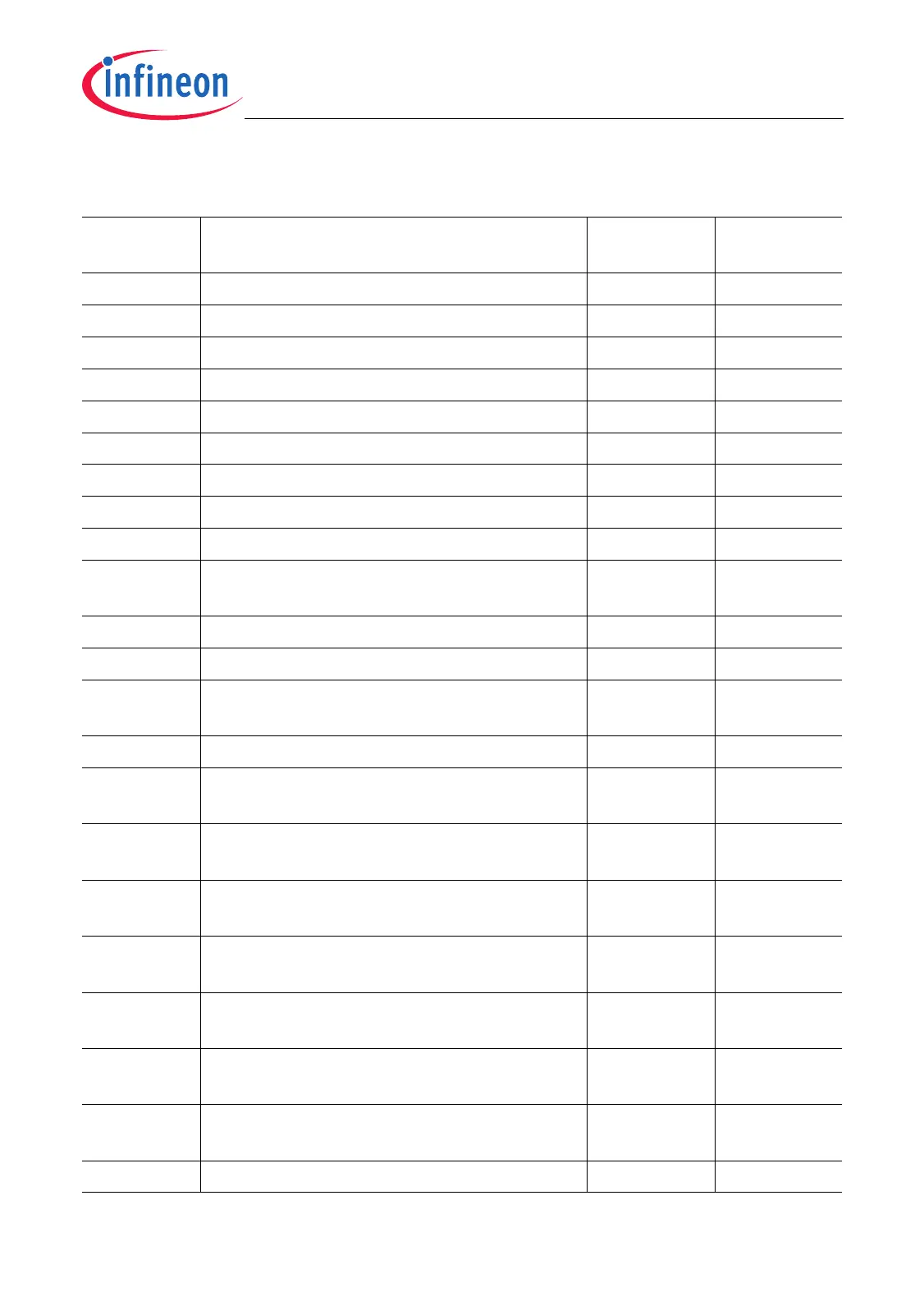

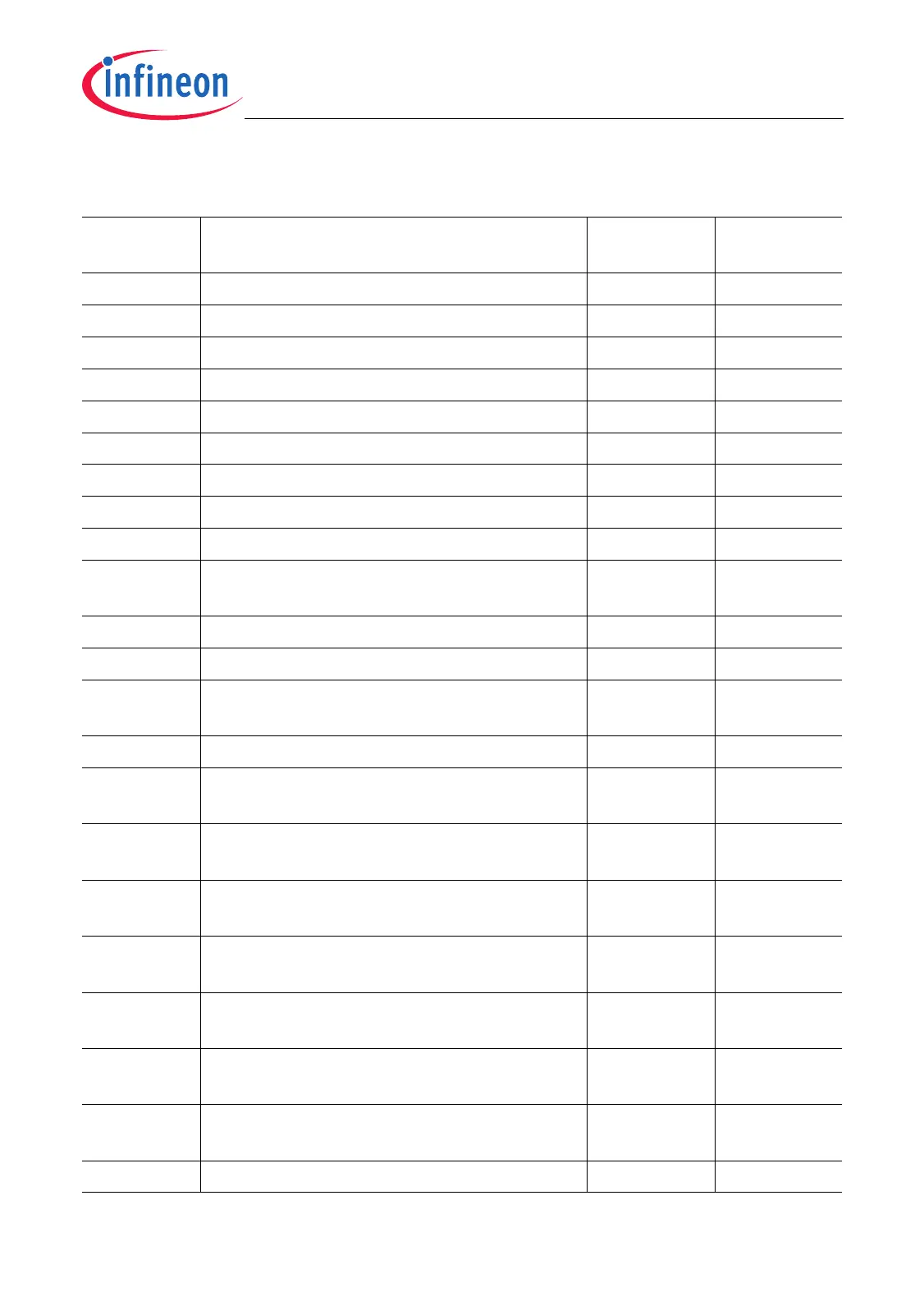

Table 24-17 Registers Overview - GPTA0 and GPTA1 Kernel Registers

Register

Short Name

Register Long Name Offset

Address

Description

see

ID Module Identification Register 008

H

Page 24-154

SRSC0 Service Request State Clear Register 0 010

H

Page 24-206

SRSS0 Service Request State Set Register 0 014

H

Page 24-208

SRSC1 Service Request State Clear Register 1 018

H

Page 24-209

SRSS1 Service Request State Set Register 1 01C

H

Page 24-210

SRSC2 Service Request State Clear Register 2 020

H

Page 24-211

SRSS2 Service Request State Set Register 2 024

H

Page 24-212

SRSC3 Service Request State Clear Register 3 028

H

Page 24-213

SRSS3 Service Request State Set Register 3 02C

H

Page 24-214

SRNR Service Request Node Redirection

Register

030

H

Page 24-215

MRACTL Multiplexer Register Array Control Register 038

H

Page 24-191

MRADIN Multiplexer Register Array Data In Register 03C

H

Page 24-193

MRADOUT Multiplexer Register Array Data Out

Register

040

H

Page 24-193

FPCSTAT Filter and Prescaler Cell Status Register 044

H

Page 24-155

FPCCTRk Filter and Prescaler Cell Control Register k

(k = 0-5)

048

H

+

k × 8

Page 24-156

FPCTIMk Filter and Prescaler Cell Timer Register k

(k = 0-5)

048

H

+

k × 8 + 4

Page 24-158

PDLCTR Phase Discrimination Logic Control

Register

078

H

Page 24-159

DCMCTRk Duty Cycle Measurement Control Register

k (k = 0-3)

080

H

+

k × 16

Page 24-161

DCMTIMk Duty Cycle Measurement Timer Register k

(k = 0-3)

080

H

+

k × 16 + 4

Page 24-163

DCMCAVk Duty Cycle Measurement Capture Register

k (k = 0-3)

080

H

+

k × 16 + 8

Page 24-163

DCMCOVk Duty Cycle Measurement

Capture/Compare Register k (k = 0-3)

080

H

+

k × 16 + 12

Page 24-164

PLLCTR Phase Locked Loop Control Register 0C0

H

Page 24-165

Loading...

Loading...