TC1796

Peripheral Units (Vol. 2 of 2)

General Purpose Timer Array (GPTA)

User’s Manual 24-152 V2.0, 2007-07

GPTA, V2.0

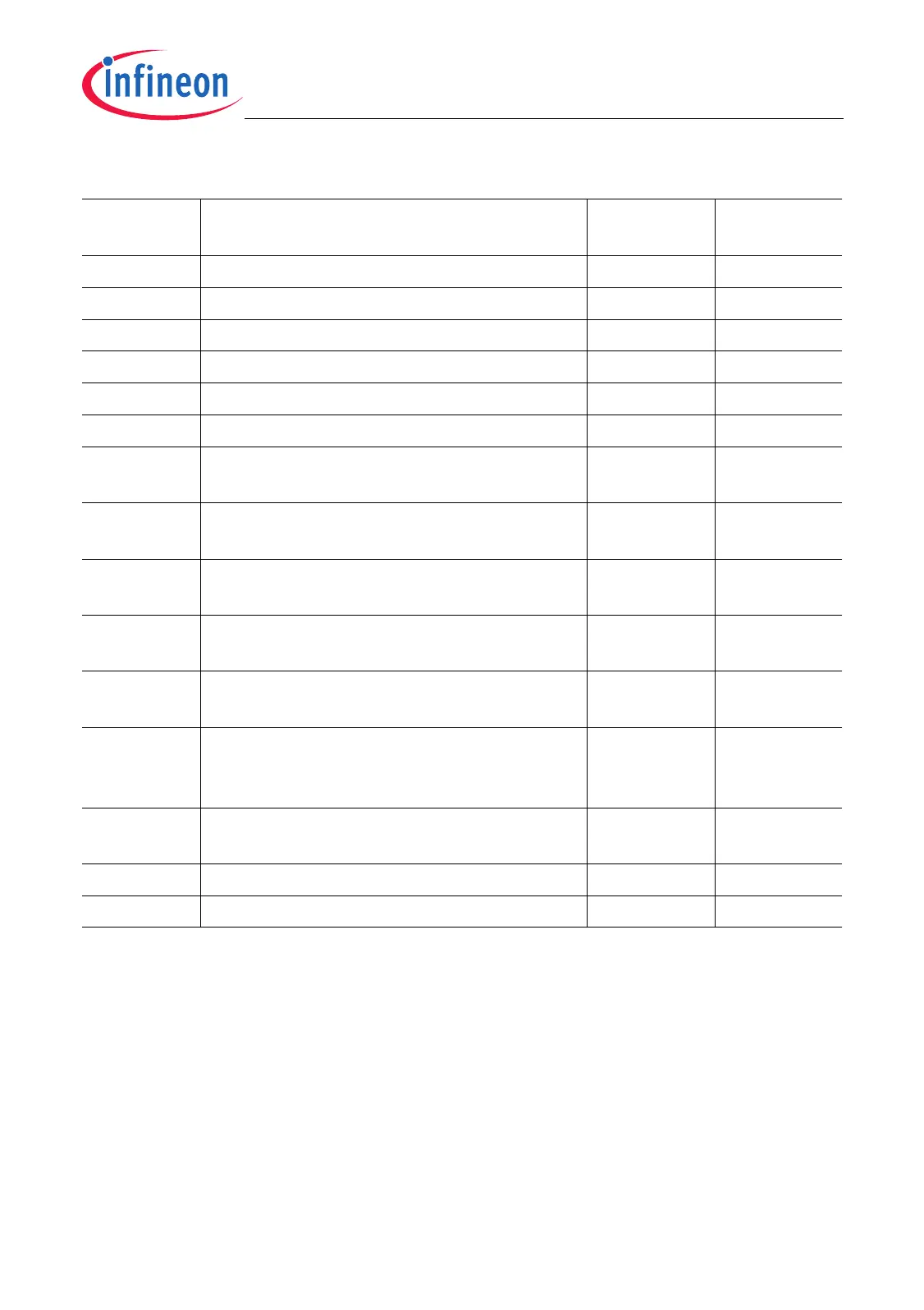

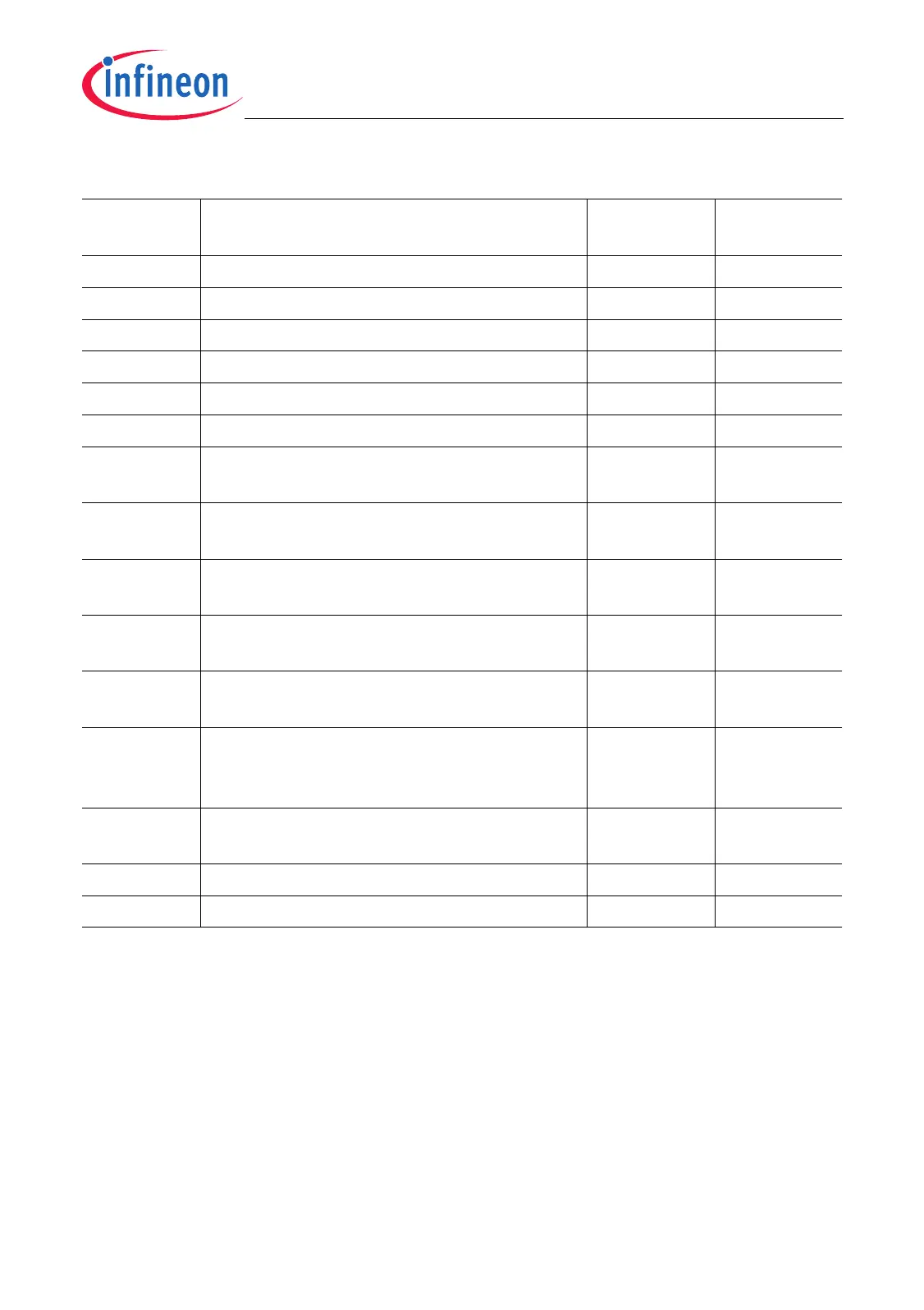

PLLMTI Phase Locked Loop Micro Tick Register 0C4

H

Page 24-166

PLLCNT Phase Locked Loop Counter Register 0C8

H

Page 24-167

PLLSTP Phase Locked Loop Step Register 0CC

H

Page 24-167

PLLREV Phase Locked Loop Reload Register 0D0

H

Page 24-168

PLLDTR Phase Locked Loop Delta Register 0D4

H

Page 24-168

CKBCTR Clock Bus Control Register 0D8

H

Page 24-173

GTCTRk Global Timer Control Register k

(k = 0, 1)

0E0

H

+

k × 16

Page 24-170

GTREVk Global Timer Reload Value Register k

(k = 0, 1)

0E0

H

+

k

×

16 + 4

Page 24-172

GTTIMk Global Timer Register k

(k = 0, 1)

0E0

H

+

k × 16 + 8

Page 24-171

GTCCTRk Global Timer Cell Control Register k

(k = 00-31)

100

H

+

k × 8

Page 24-175

Page 24-177

GTCXRk Global Timer Cell X Register k

(k = 00-31)

100

H

+

k × 8 + 4

Page 24-179

LTCCTRk Local Timer Cell Control Register k

(k = 00-62)

200

H

+

k × 8

Page 24-180

Page 24-183

Page 24-185

LTCXRk Local Timer Cell X Register k

(k = 00-62)

200

H

+

k × 8 + 4

Page 24-190

LTCCTR63 Local Timer Cell Control Register 63 3F8

H

Page 24-188

LTCXR63 Local Timer Cell X Register 63 3FC

H

Page 24-190

Table 24-17 Registers Overview - GPTA0 and GPTA1 Kernel Registers (cont’d)

Register

Short Name

Register Long Name Offset

Address

Description

see

Loading...

Loading...