TC1796

Peripheral Units (Vol. 2 of 2)

General Purpose Timer Array (GPTA)

User’s Manual 24-153 V2.0, 2007-07

GPTA, V2.0

Bit Protection

Bits with bit protection (this is valid, for example, for all bits in the Service Request State

Registers) are not changed during a read-modify-write instruction, for example when

hardware sets a request state bit between the read and the write of the read-modify-write

sequence. For bit protected bits it is guaranteed that a hardware setting operation always

has priority. Thus, no hardware triggered events are lost.

Bits with bit protection are marked in the corresponding bit descriptions.

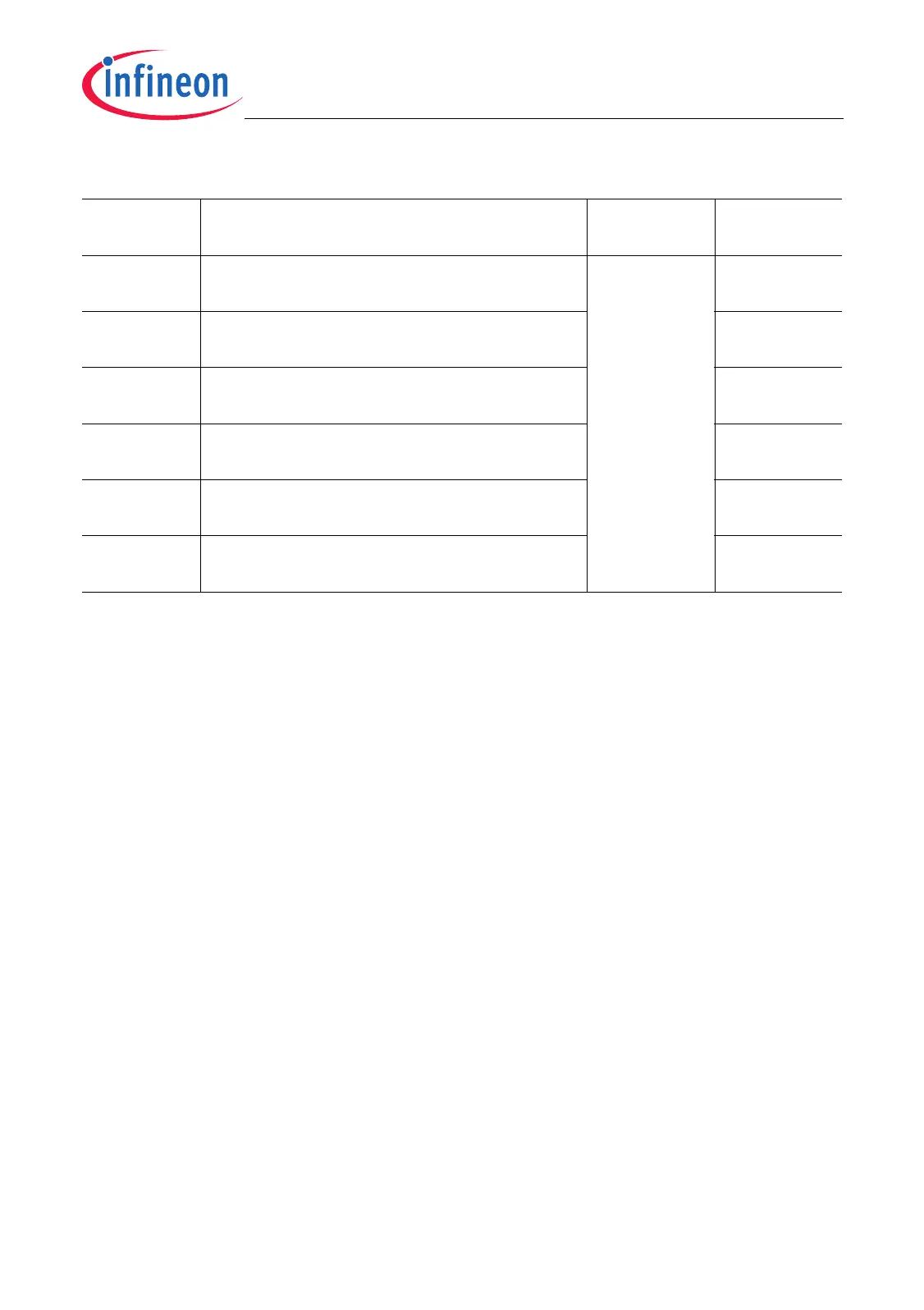

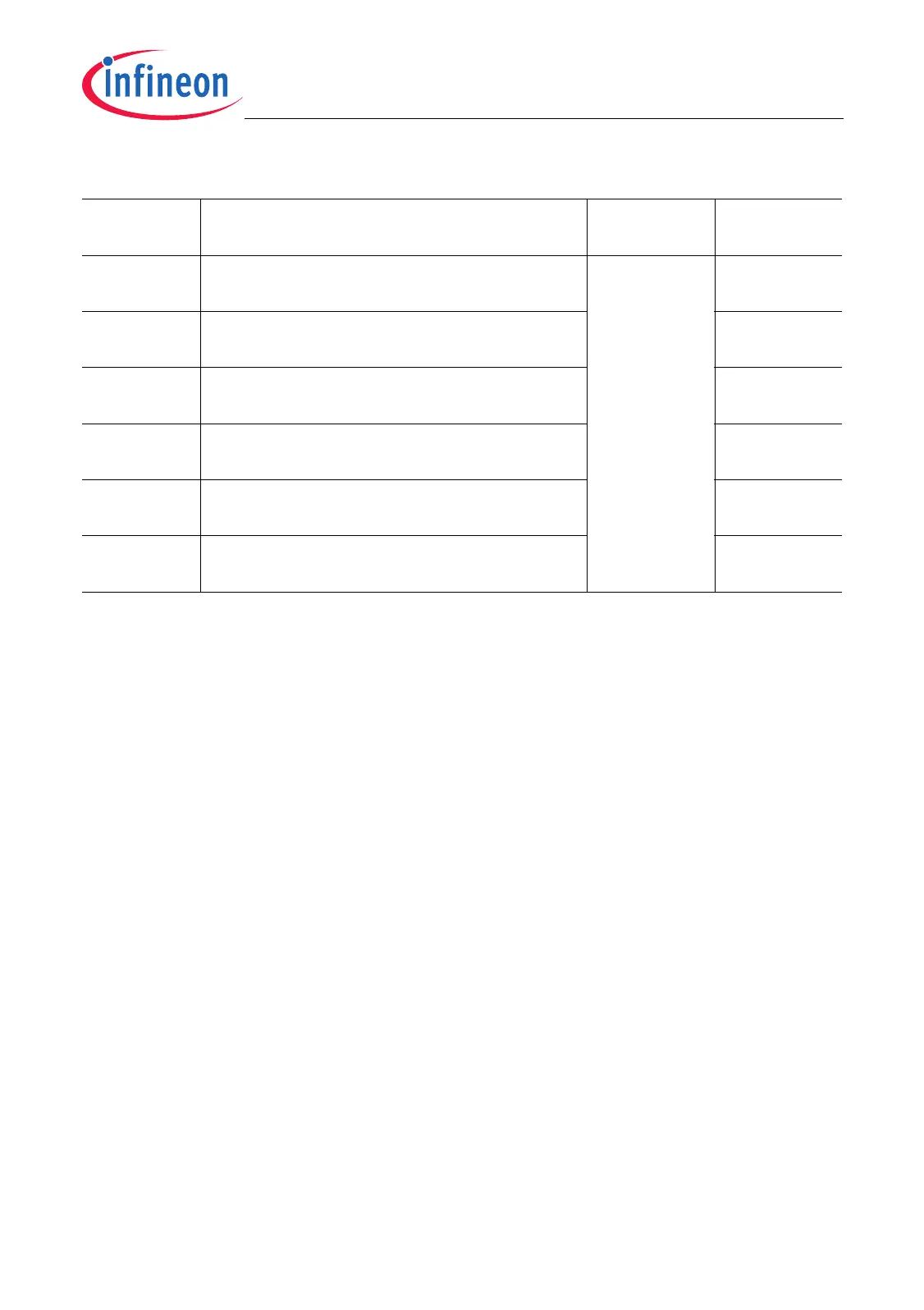

OMCRLg Output Multiplexer Control Register for

Lower Half of Group g (g = 0-13)

not directly

addressable;

see

Page 24-110

Page 24-194

OMCRLg Output Multiplexer Control Register for

Upper Half of Group g (g = 0-13)

Page 24-196

GIMCRLg Input Multiplexer Control Register for

Lower Half of GTC Group g (g = 3-0)

Page 24-198

GIMCRLg Input Multiplexer Control Register for

Lower Half of GTC Group g (g = 0-3)

Page 24-200

LIMCRLg Input Multiplexer Control Register for

Lower Half of LTC Group g (g = 0-7)

Page 24-202

LIMCRLg Input Multiplexer Control Register for

Upper Half of LTC Group g (g = 0-7)

Page 24-204

Table 24-17 Registers Overview - GPTA0 and GPTA1 Kernel Registers (cont’d)

Register

Short Name

Register Long Name Offset

Address

Description

see

Loading...

Loading...