www.ti.com

Memory Organization

123

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

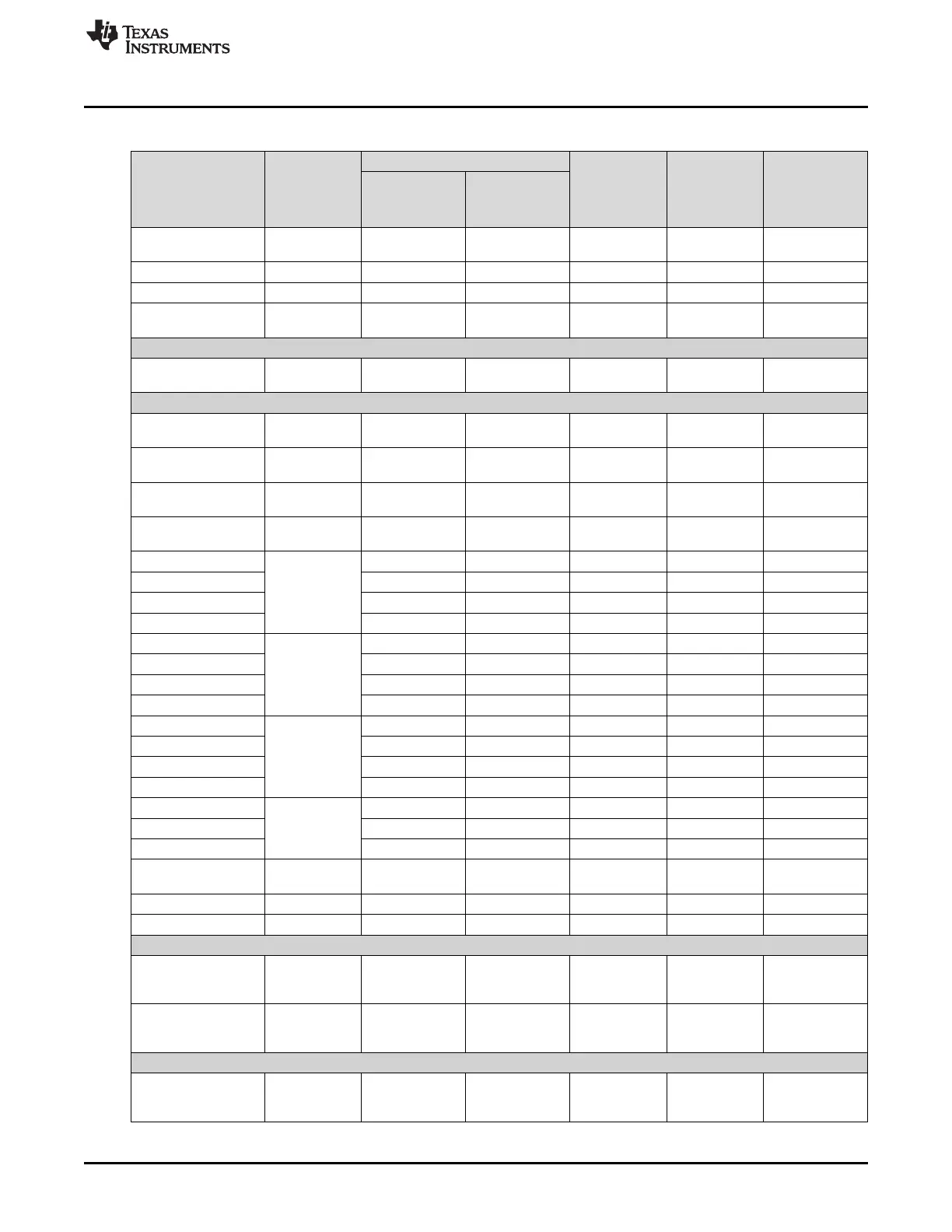

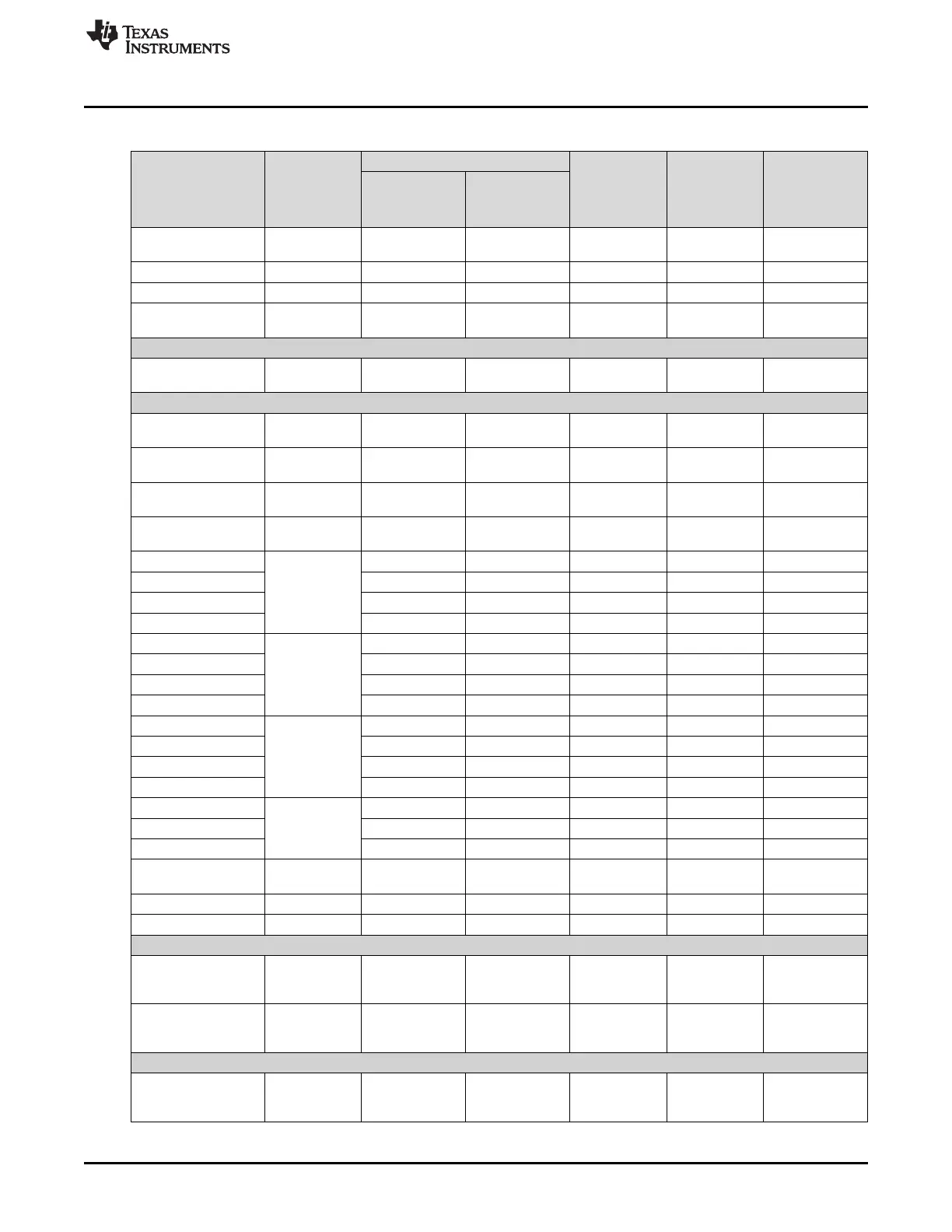

Table 2-2. Module Registers / Memories Memory-Map (continued)

Target Name

Memory

Select

Address Range

Frame Size Actual Size

Response for

Access to

Unimplemented

Locations in

FrameStart End

TI OTP-ECC,

EEPROM Bank

0xF00C_1C00 0xF00C_1FFF 1kB 128B Abort

EEPROM Bank-ECC 0xF010_0000 0xF01F_FFFF 1MB 16kB Abort

EEPROM Bank 0xF020_0000 0xF03F_FFFF 2MB 128kB Abort

Flash Data Space

ECC

0xF040_0000 0xF05F_FFFF 2MB 512kB Abort

Interconnect SDC MMR

Interconnect SDC

MMR

0xFA00_0000 0xFAFF_FFFF 16MB 16MB

Registers/Memories under PCR2 (Peripheral Segment 2)

CPPI Memory Slave

(Ethernet RAM)

PCS[41] 0xFC52_0000 0xFC52_1FFF 8kB 8kB Abort

CPGMAC Slave

(Ethernet Slave)

PS[30]-PS[31] 0xFCF7_8000 0xFCF7_87FF 2kB 2kB No Error

CPGMACSS Wrapper

(Ethernet Wrapper)

PS[29] 0xFCF7_8800 0xFCF7_88FF 256B 256B No Error

Ethernet MDIO

Interface

PS[29] 0xFCF7_8900 0xFCF7_89FF 256B 256B No Error

ePWM1 PS[28] 0xFCF7_8C00 0xFCF7_8CFF 256B 256B Abort

ePWM2 0xFCF7_8D00 0xFCF7_8DFF 256B 256B Abort

ePWM3 0xFCF7_8E00 0xFCF7_8EFF 256B 256B Abort

ePWM4 0xFCF7_8F00 0xFCF7_8FFF 256B 256B Abort

ePWM5 PS[27] 0xFCF7_9000 0xFCF7_90FF 256B 256B Abort

ePWM6 0xFCF7_9100 0xFCF7_91FF 256B 256B Abort

ePWM7 0xFCF7_9200 0xFCF7_92FF 256B 256B Abort

eCAP1 0xFCF7_9300 0xFCF7_93FF 256B 256B Abort

eCAP2 PS[26] 0xFCF7_9400 0xFCF7_94FF 256B 256B Abort

eCAP3 0xFCF7_9500 0xFCF7_95FF 256B 256B Abort

eCAP4 0xFCF7_9600 0xFCF7_96FF 256B 256B Abort

eCAP5 0xFCF7_9700 0xFCF7_97FF 256B 256B Abort

eCAP6 PS[25] 0xFCF7_9800 0xFCF7_98FF 256B 256B Abort

eQEP1 0xFCF7_9900 0xFCF7_99FF 256B 256B Abort

eQEP2 0xFCF7_9A00 0xFCF7_9AFF 256B 256B Abort

PCR2 registers PPSE[4]-

PPSE[5]

0xFCFF_1000 0xFCFF_17FF 2kB 2kB

NMPU (CPGMAC) PPSE[6] 0xFCFF_1800 0xFCFF_18FF 512B 512B Abort

EMIF Registers PPS[2] 0xFCFF_E800 0xFCFF_E8FF 256B 256B Abort

Cyclic Redundancy Checker (CRC) Module Register Frame

CRC1 0xFE00_0000 0xFEFF_FFFF 16MB 512kB Accesses above

0xFE000200

generate abort.

CRC2 0xFB00_0000 0xFBFF_FFFF 16MB 512kB Accesses above

0xFB000200

generate abort.

Memories under User PCR3 (Peripheral Segment 3)

MIBSPI5 RAM PCS[5] 0xFF0A_0000 0xFF0B_FFFF 128kB 2kB Abort for

accesses above

2KB

Loading...

Loading...