Data(31-0)

Data(31-0)

Address

Data(31-0)

Data(31-0)

Address-

Input Buffer

Message handler

Address

Output Buffer

Decoder

and Control

Control

Host CPU

Header Partition

Data Partition

Message RAM

[Shadow][Shadow]

Address

Module Operation

www.ti.com

1252

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

NOTE: Reconfiguration of message buffers may lead to the loss of messages and therefore has to

be used very carefully. In worst case (reconfiguration in consecutive cycles) it may happen

that a message buffer is never transmitted / updated from a received frame.

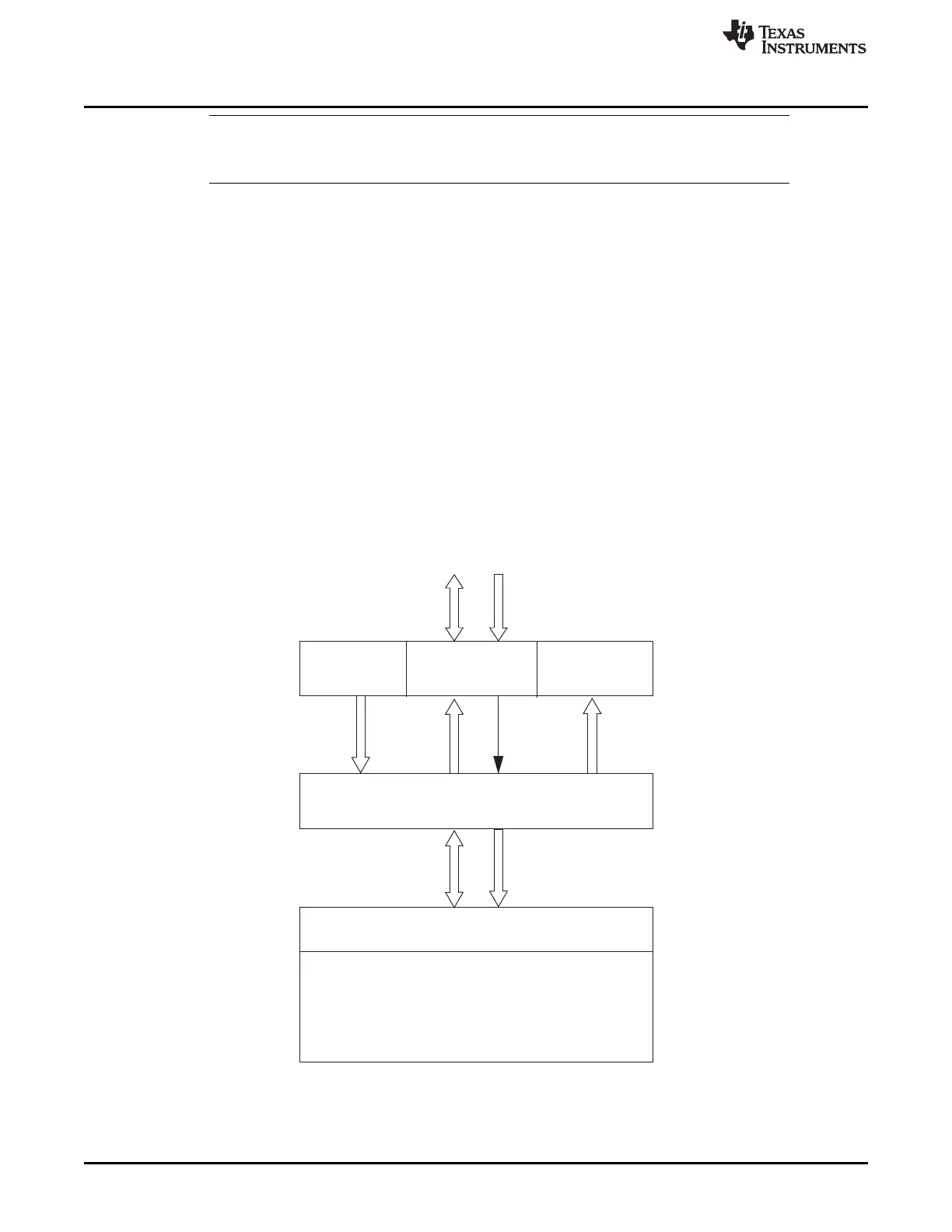

26.2.12.2 Host Access to Message RAM

The message transfer between input buffer and message RAM as well as between message RAM and

output buffer is triggered by the host CPU by writing the number of the target / source message buffer to

be accessed to the input or output buffer command request register (IBCR/OBCR).

The input / output buffer command mask registers can be used to write / read header and data section of

the selected message buffer separately.

If bit IBCM.STXR in the input buffer command mask register is set (STXR = 1), the transmission request

flag TXR of the selected message buffer is automatically set after the message buffer has been updated.

If bit IBCM.STXR in the input buffer command mask register is reset (STXR = 0), the transmission request

flag TXR of the selected message buffer is reset. This can be used to stop transmission from message

buffers operated in continuous mode.

Input buffer (IBF) and the output buffer (OBF) are built up as a double buffer structure. One half of this

double buffer structure is accessible by the host CPU (IBF host / OBF host), while the other half (IBF

shadow / OBF shadow) is accessed by the message handler for data transfers between IBF / OBF and

message RAM.

Figure 26-17. Host Access to Message RAM

Loading...

Loading...