FlexRay Module Registers

www.ti.com

1298

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

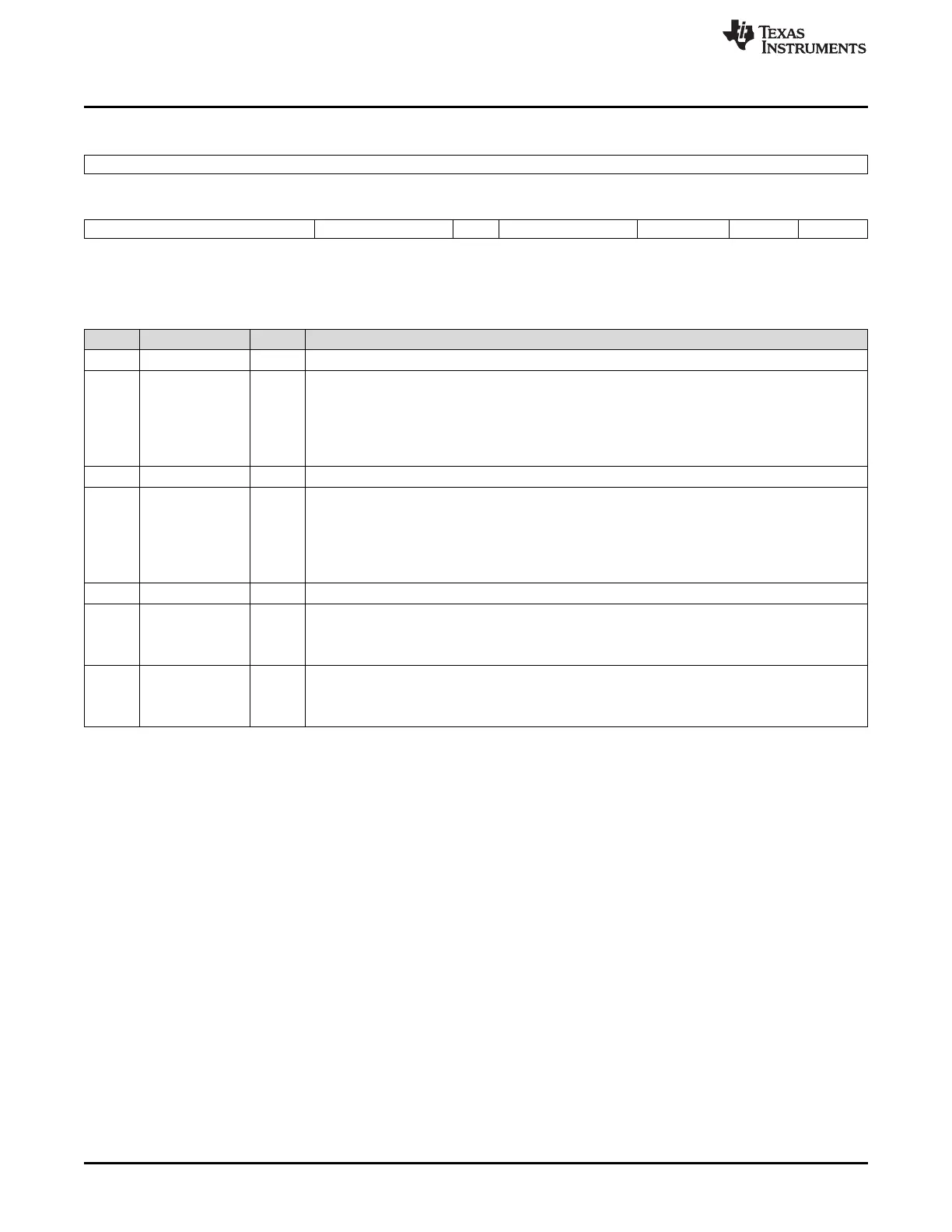

Figure 26-57. Transfer Error Interrupt Enable Reset (TEIRER) [offset_TU = 7Ch]

31 16

Reserved

R-0

15 11 10 8 7 6 4 3 2 1 0

Reserved RSTATE RSVD WSTATE Reserved TNRE FACE

R-0 R/WC-0 R-0 R/WC-0 R-0 R/WC-0 R/WC-0

LEGEND: R/W = Read/Write; R = Read only; C = Clear; -n = value after reset

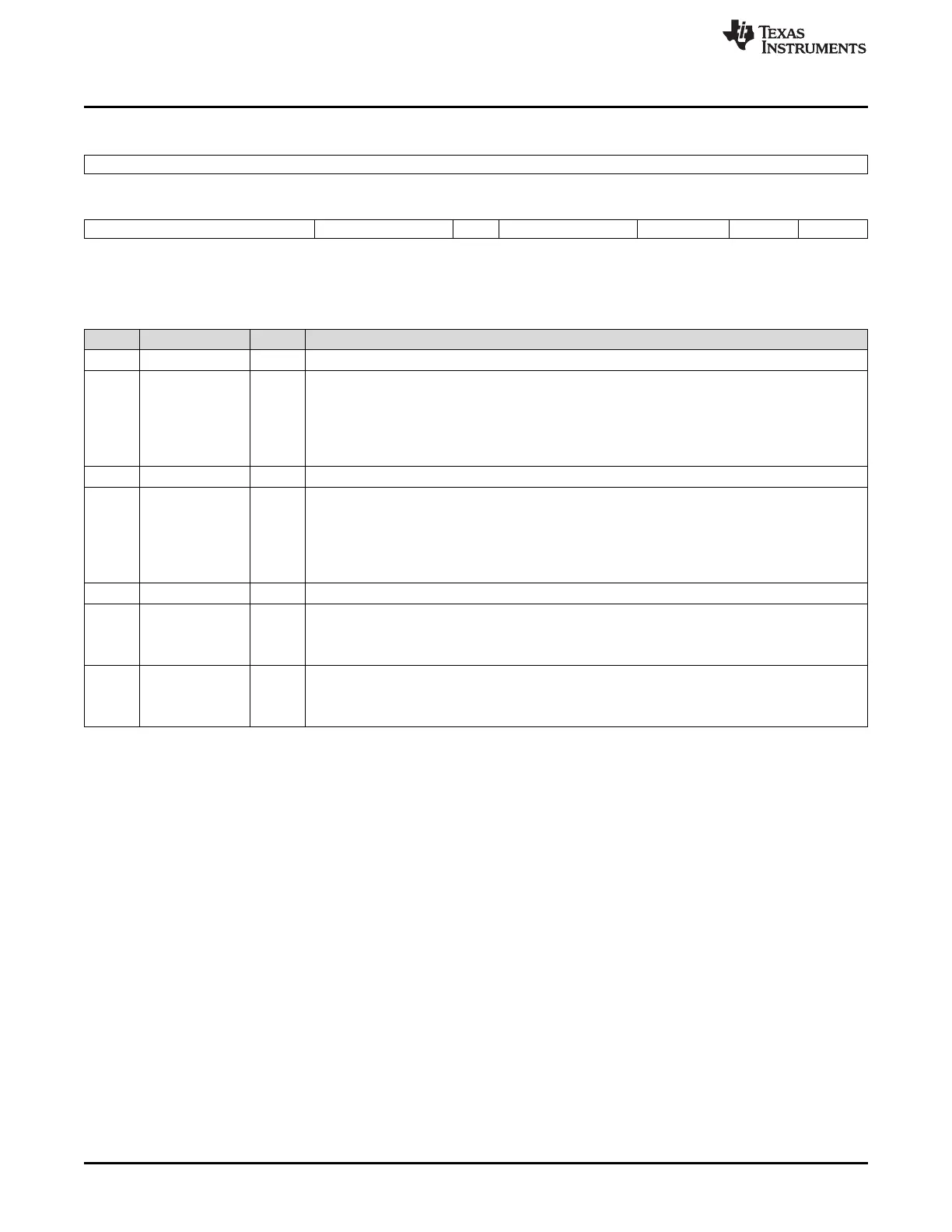

Table 26-37. Transfer Error Interrupt Enable Reset (TEIRER)

Bit Field Value Description

31-11 Reserved 0 Reads return 0. Writes have no effect.

10-8 RSTATE Read Error Interrupt Generation (interrupt generation on VBUS read transfer errors).

0 Interrupt generation on VBUS read transfer error is disabled.

7h Interrupt generation on VBUS read transfer error is enabled.

Note: Any value different from 111 does not assure the interrupt error generation of all possible

VBUS read errors.

7 Reserved 0 Reads return 0. Writes have no effect.

6-4 WSTATE Write Error Interrupt Generation (interrupt generation on VBUS write transfer errors).

0 Interrupt generation on VBUS write transfer error is disabled.

7h Interrupt generation on VBUS write transfer error is enabled.

Note: Any value different from 111 does not assure the interrupt error generation of all possible

VBUS read errors.

3-2 Reserved 0 Reads return 0. Writes have no effect.

1 TNRE Transfer Not Ready Enable.

0 TNR interrupt is disabled.

1 TNR interrupt is enabled.

0 FACE Forbidden Access Enable.

0 FAC interrupt is disabled.

1 FAC interrupt is enabled.

Loading...

Loading...