FlexRay Module Registers

www.ti.com

1314

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

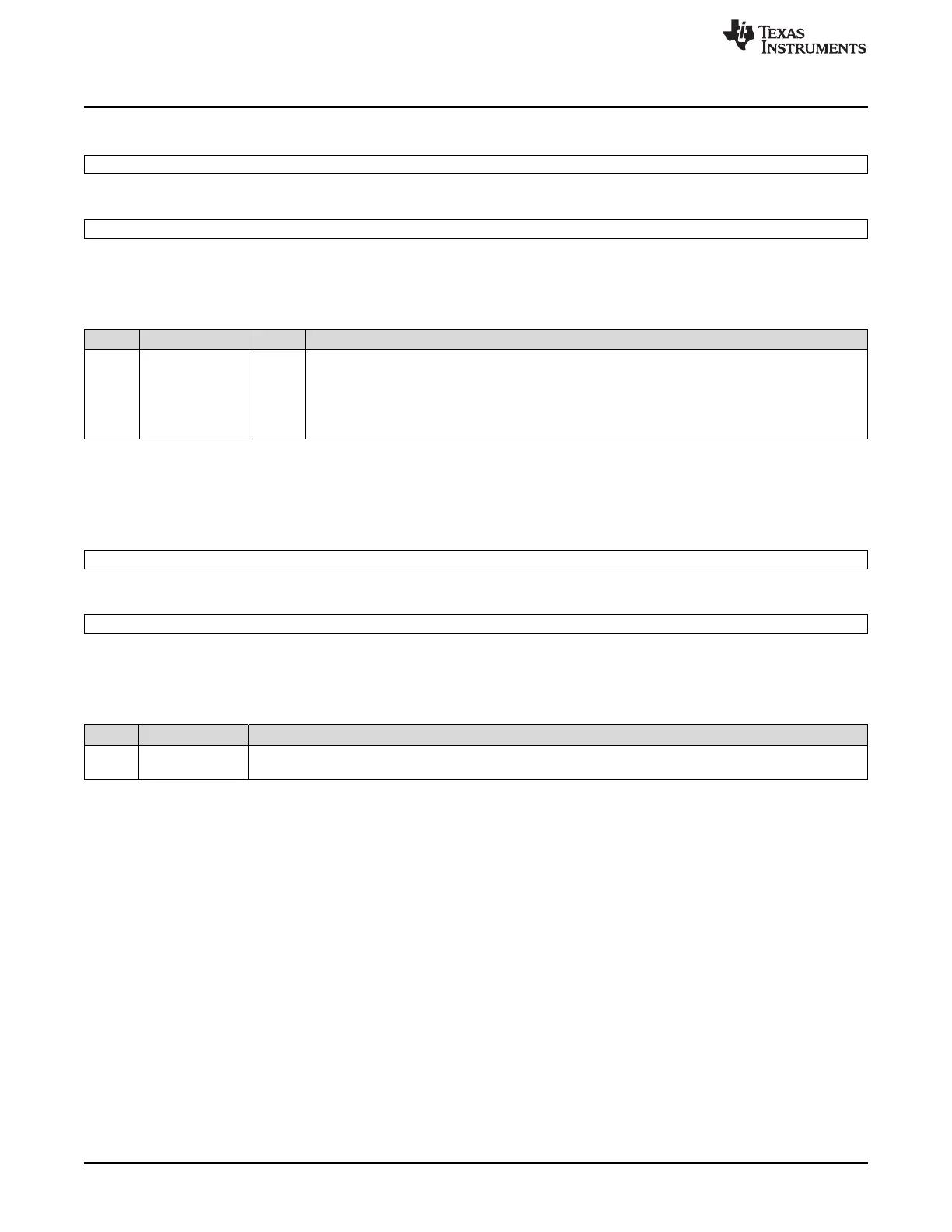

Figure 26-88. Clear on Event to System Memory Set 4 (CESMS4) [offset_TU = F8h]

31 16

CESMS4[127-112]

R/WS-0

15 0

CESMS4[111-96]

R/WS-0

LEGEND: R/W = Read/Write; R = Read only; S = Set; -n = value after reset

Table 26-68. Clear on Event to System Memory Set 4 (CESMS4) Field Descriptions

Bit Field Value Description

31-0 CESMS4[n] Clear on Event to System Memory Set 4. The register bits 0 to 31 correspond to message buffers

96 to 127. Each bit of the register enables an automatic clear of the corresponding ETESM4 bit

after a receive or transmit event:

0 No clear.

1 Activate clear.

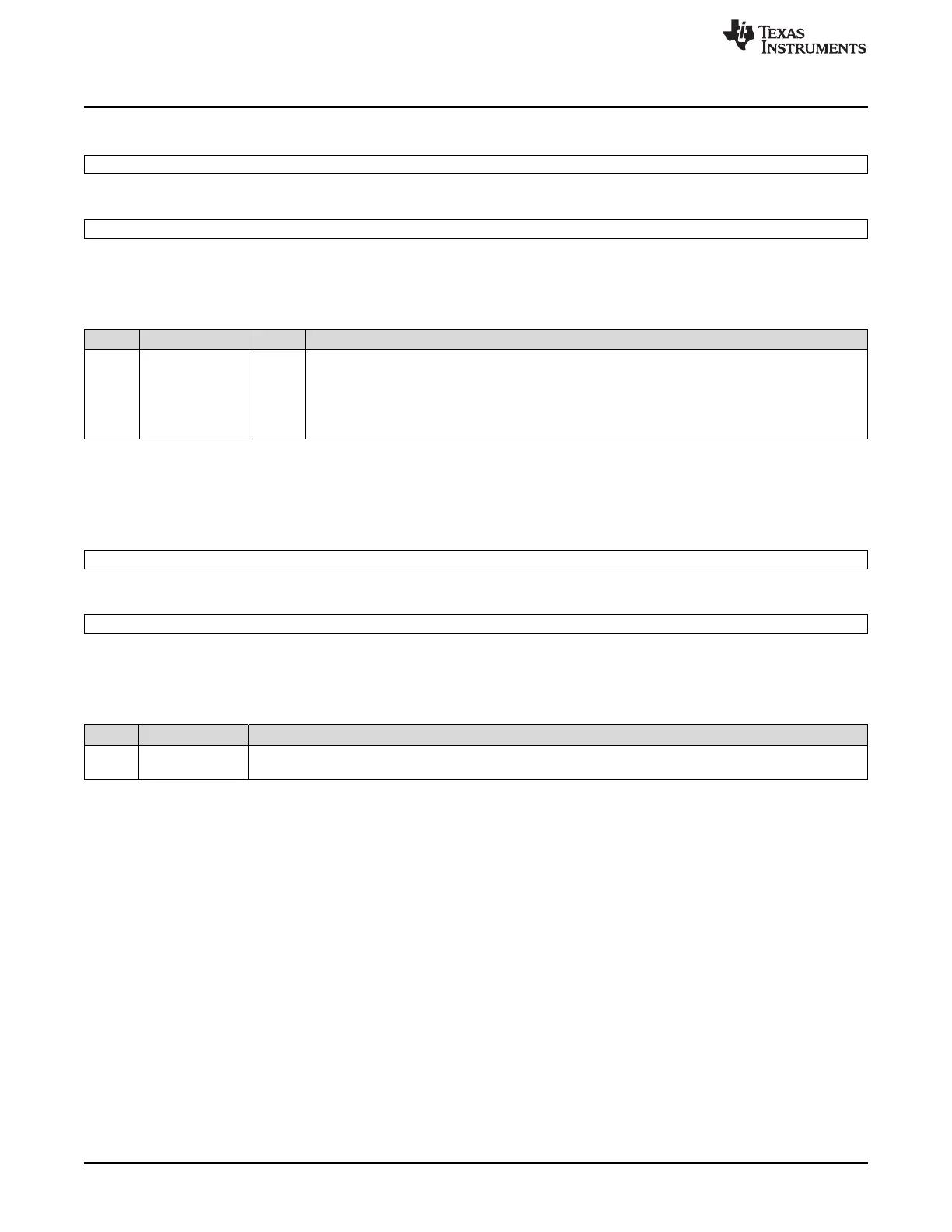

Figure 26-89. Clear on Event to System Memory Reset 4 (CESMR4) [offset_TU = FCh]

31 16

CESMR4

R/WC-0

15 0

CESMR4

R/WC-0

LEGEND: R/W = Read/Write; R = Read only; C = Clear; -n = value after reset

Table 26-69. Clear on Event to System Memory Reset 4 (CESMR4) Field Descriptions

Bit Field Description

31-0 CESMR4 Clear on Event to System Memory Reset 4. The CESMR4 register shows the identical values to CESMS4 if

read.

Loading...

Loading...