FlexRay Module Registers

www.ti.com

1328

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

26.3.2.1 Special Registers

26.3.2.1.1 ECC Control Register (ECC_CTRL)

ECC Control Register holds three 4-bit keys. SBEL to turn ECC single-bit error correction on or off,

SBE_EVT_EN to enable a single-bit error event and DIAGSEL to enable the diagnostic mode to test the

ECC single-bit error correction and double-bit error detection (SECDED) mechanism. Write access to key

DIAGSEL is only possible in privilege mode.

Figure 26-109 and Table 26-89 illustrate this register.

NOTE: Diagnostic mode should be used only for RAM test purpose in RAM test mode. Therefore,

when entering diagnostic mode, the FlexRay module should be in RAM test mode (TMC(1-0)

set to 1 in Test Register 1 (TEST1)) before performing ECC testing.

Single-bit error correction can only be active when ECC is enabled.

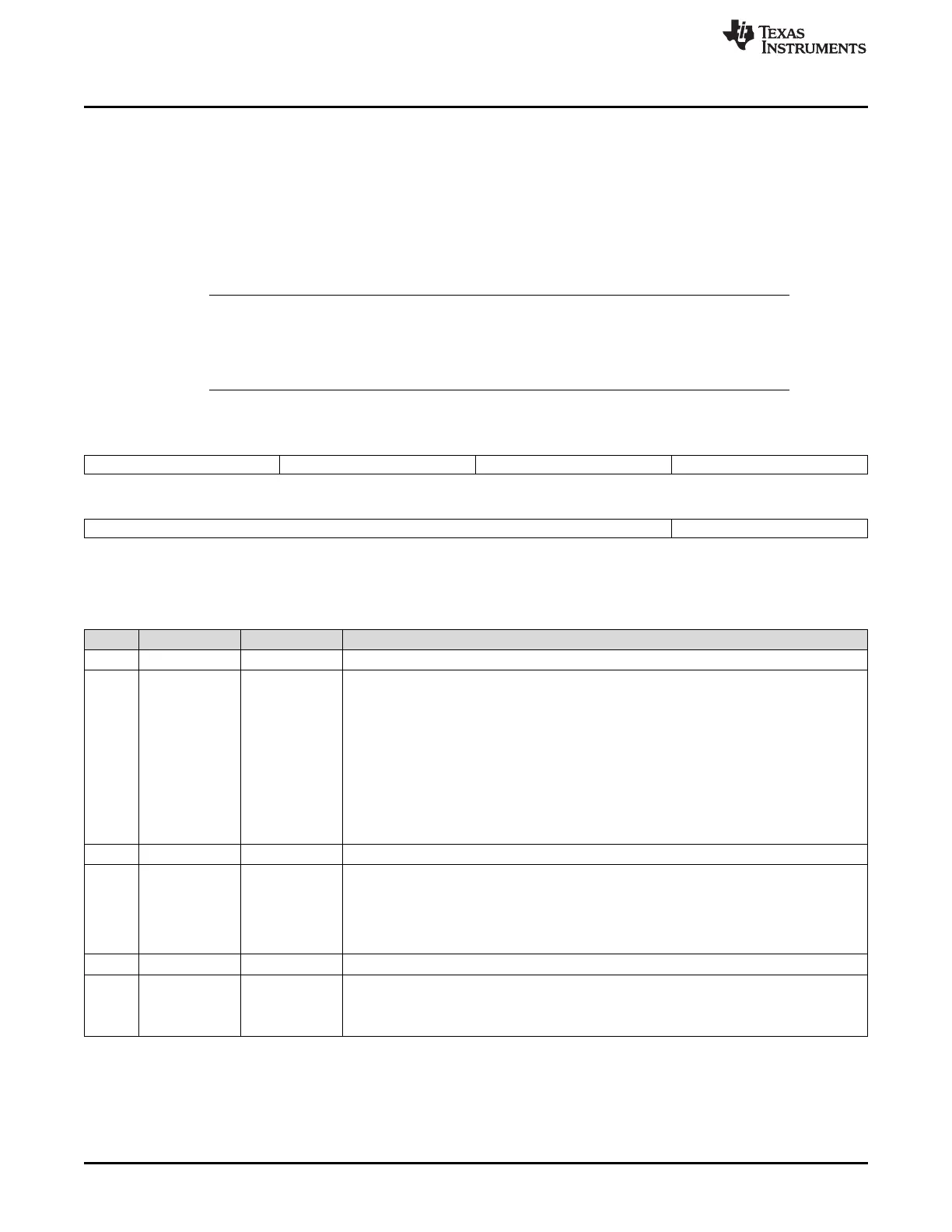

Figure 26-109. ECC Control Register (ECC_CTRL) [offset_CC = 00h]

31 28 27 24 23 20 19 16

Reserved SBE_EVT_EN Reserved SBEL

R-0 R/W-5h R-0 R/W-Ah

15 4 3 0

Reserved DIAGSEL

R-0 R/WP-Ah

LEGEND: R/W = Read/Write; R = Read only; WP = Write in Privilege Mode only; -n = value after reset

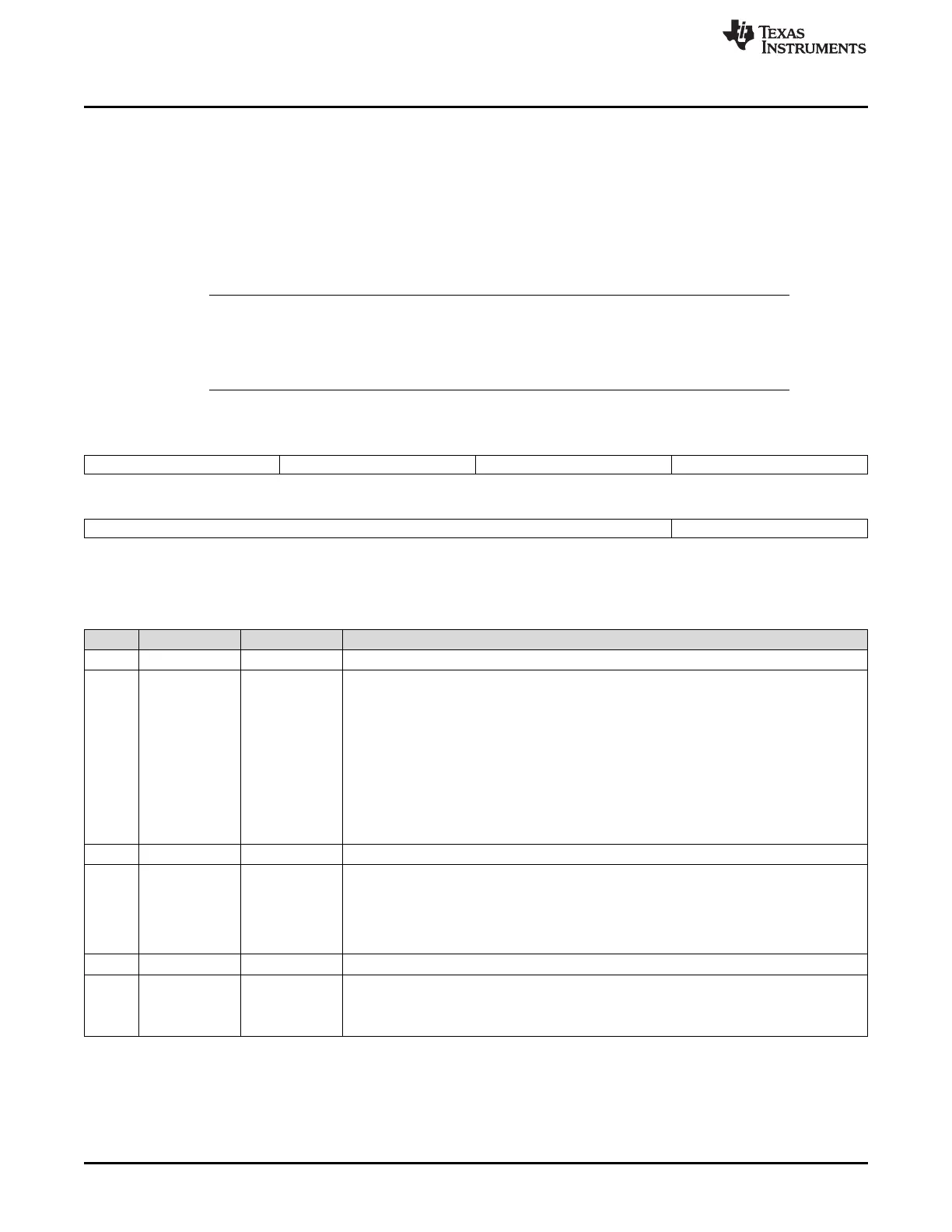

Table 26-89. ECC Control Register (ECC_CTRL) Field Descriptions

Bit Field Value Description

31-28 Reserved 0 Reads return 0. Writes have no effect.

27-24 SBE_EVT_EN ECC Single-Bit Error Indication.

5h ECC single-bit error indication is disabled. On ECC single-bit error detection when reading

from message RAM, transient buffer RAMs, input buffer RAMs and output buffer RAMs, the

single-bit error event signal of the communication controller (CC_SBE_err) is activated. On

ECC single-bit error detection when reading from TCR, the single-bit error event signal of the

transfer unit (TU_SBE_err) is activated.

All other values ECC single-bit error indication is enabled. On ECC single-bit error detection when reading

from message RAM, transient buffer RAMs, input buffer RAMs and output buffer RAMs, the

single-bit error event signal of the communication controller (CC_SBE_err) is not activated.

On ECC single-bit error detection when reading from TCR, the single-bit error event signal of

the transfer unit (TU_SBE_err) is not activated.

23-20 Reserved 0 Reads return 0. Writes have no effect.

19-16 SBEL ECC Single-Bit Error Lock.

5h ECC single-bit error correction is turned off. ECC single-bit errors in the FlexRay RAMs do

not get corrected and the ECC algorithm will detect up to 3 bits in error in a word.

All other values ECC single-bit error correction is turned on. ECC single-bit errors in the FlexRay RAMs get

corrected.

15-4 Reserved 0 Reads return 0. Writes have no effect.

3-0 DIAGSEL Diagnostic Mode select Key. The 4-bit key enables or disables the diagnostic mode.

5h Diagnostic mode is enabled. Double-bit errors will not trigger the peripheral ECC interrupt.

All other values Diagnostic mode is disabled. Double-bit errors will trigger the peripheral ECC interrupt.

Loading...

Loading...