FlexRay Module Registers

www.ti.com

1342

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

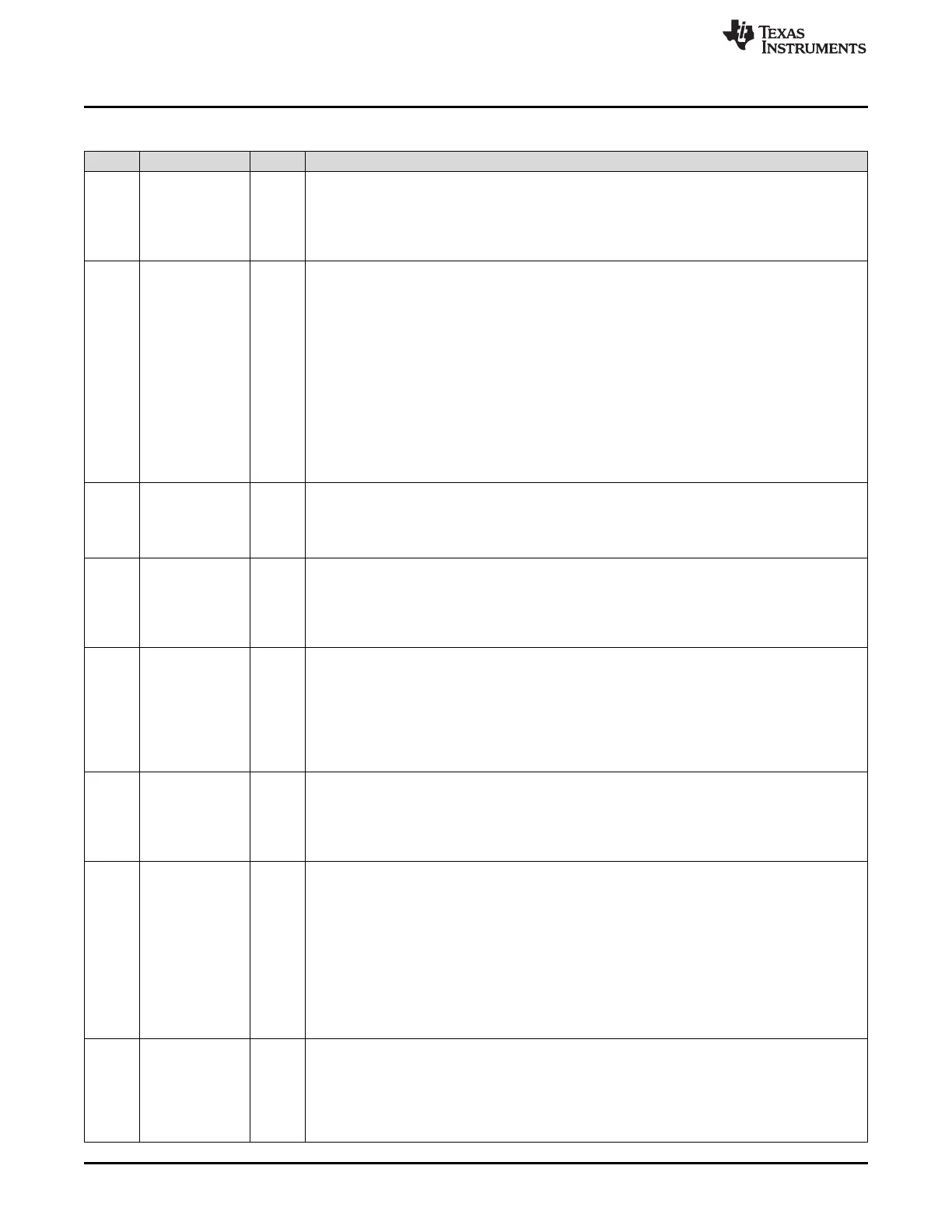

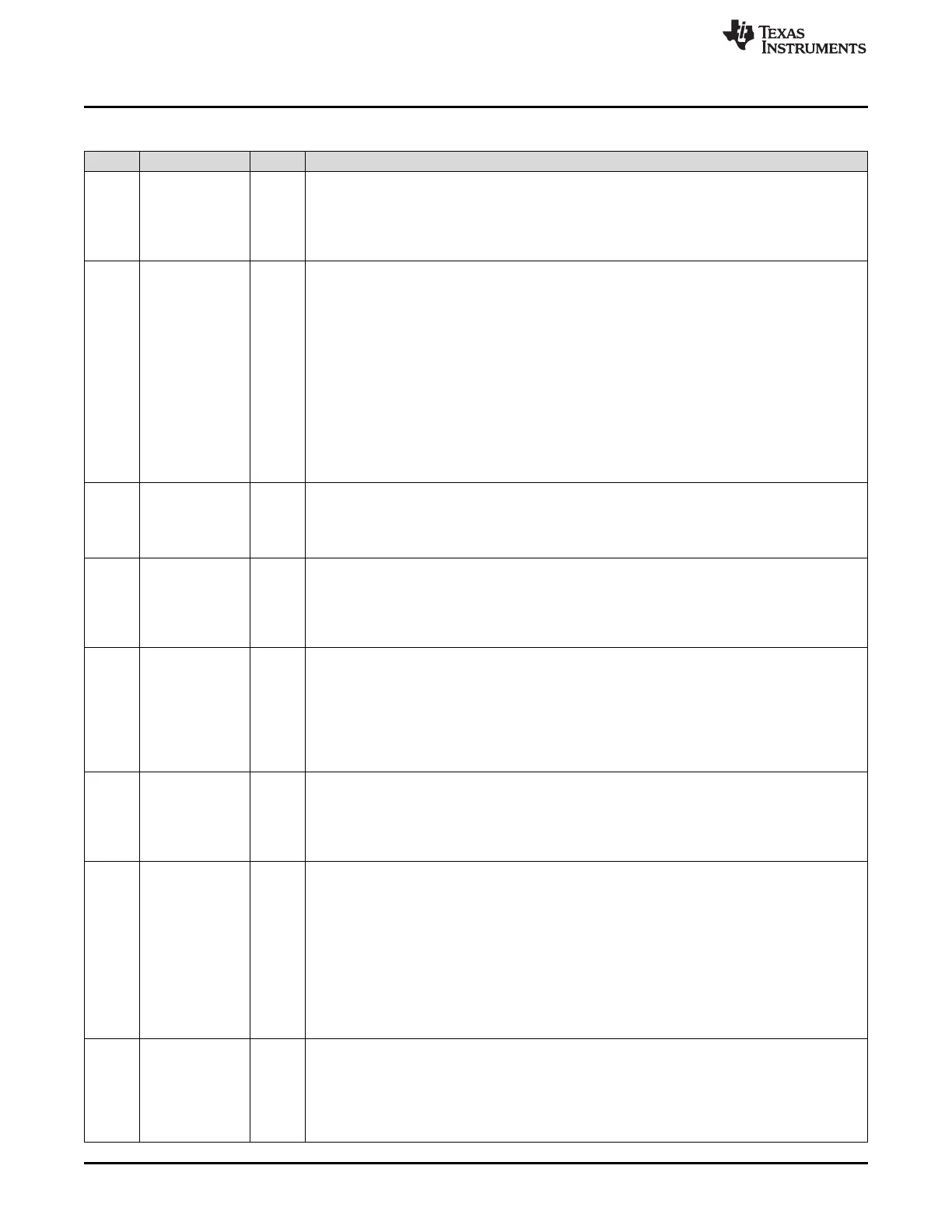

Table 26-96. Error Interrupt Register (EIR) Field Descriptions (continued)

Bit Field Value Description

10 IOBA Illegal Output buffer Access. This flag is set by the communication controller when the Host

requests the transfer of a message buffer from the Message RAM to the Output Buffer while

OBCR.OBSYS is set to 1.

0 No illegal Host access to Output Buffer occurred.

1 Illegal Host access to Output Buffer occurred.

9 IIBA Illegal Input Buffer Access. This flag is set by the communication controller when the Host wants to

modify a message buffer via Input Buffer and one of the following conditions applies:

• The communication controller is not in CONFIG or DEFAULT_CONFIG state and the Host writes

to the Input Buffer Command Request register to modify the following:

– the Header section of message buffer 0, 1 if configured for transmission in key slot

– the Header section of static message buffers with buffer number < MRC.FDB while

MRC.SEC = 01

– the Header section of any static or dynamic message buffer while MRC.SEC = 1x

– Header and / or data section of any message buffer belonging to the receive FIFO

• The Host writes to any register of the Input Buffer while IBCR.IBSYH is set to 1.

0 No illegal Host access to Input Buffer occurred.

1 Illegal Host access to Input Buffer occurred.

8 EFA Empty FIFO Access. This flag is set by the communication controller when the Host requests the

transfer of a message from the receive FIFO via Output Buffer while the receive FIFO is empty.

0 No Host access to empty FIFO occurred.

1 Host access to empty FIFO occurred.

7 RFO Receive FIFO overrun. This flag is set by the communication controller when a receive FIFO

overrun was detected. The flag is cleared by the next FIFO read access of the host. After this read

access one position in the FIFO is empty again.

0 No receive FIFO overrun is detected.

1 A receive FIFO overrun is detected.

6 PERR ECC error. The flag signals an ECC multi-bit error to the host. The flag is set by the ECC logic of

the communication controller, when it detects an ECC multi-bit error while reading from one of the

FlexRay RAM blocks.

Note: ECC single-bit errors are indicated by a separate SBE bit in the Single-Bit Error Status

Register (SBESTAT).

0 No ECC multi-bit error is detected.

1 ECC multi-bit error is detected.

5 CCL CHI Command Locked. The flag signals that the write access to the CHI command vector

SUCC1.CMD was not successful because it coincided with a POC state change triggered by

protocol functions. In this case bit CNA is also set to 1.

0 CHI command is accepted.

1 CHI command is not accepted.

4 CCF Clock correction failure. This flag is set at the end of the cycle whenever one of the following errors

occurred:

• Missing rate correction signal

• Missing offset correction signal

• Clock correction Failed counter stopped at 15

• Clock correction Limit Reached

The clock correction status is monitored in the communication controller error vector and sync

frame status register.

0 No clock correction error.

1 Clock correction failed.

3 SFO Sync frame overflow. Set when either the number of sync frames received during the last

communication cycle or the total number of different sync frame IDs received during the last double

cycle exceeds the maximum number of sync frames as defined by SNM in the GTU configuration

register 2.

0 Number of received sync frames in the configured range.

1 More sync frames received than configured by SNM.

Loading...

Loading...