www.ti.com

FlexRay Module Registers

1349

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

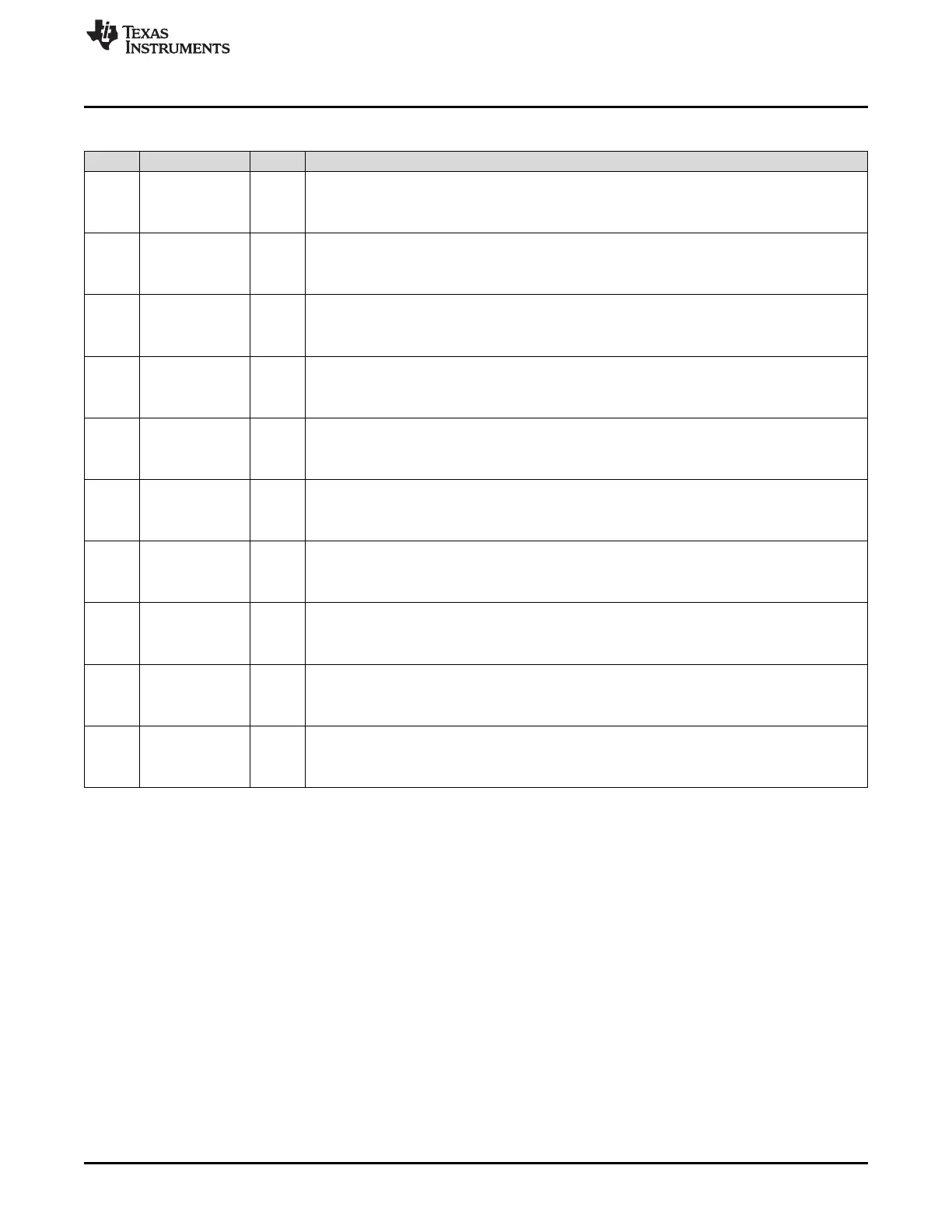

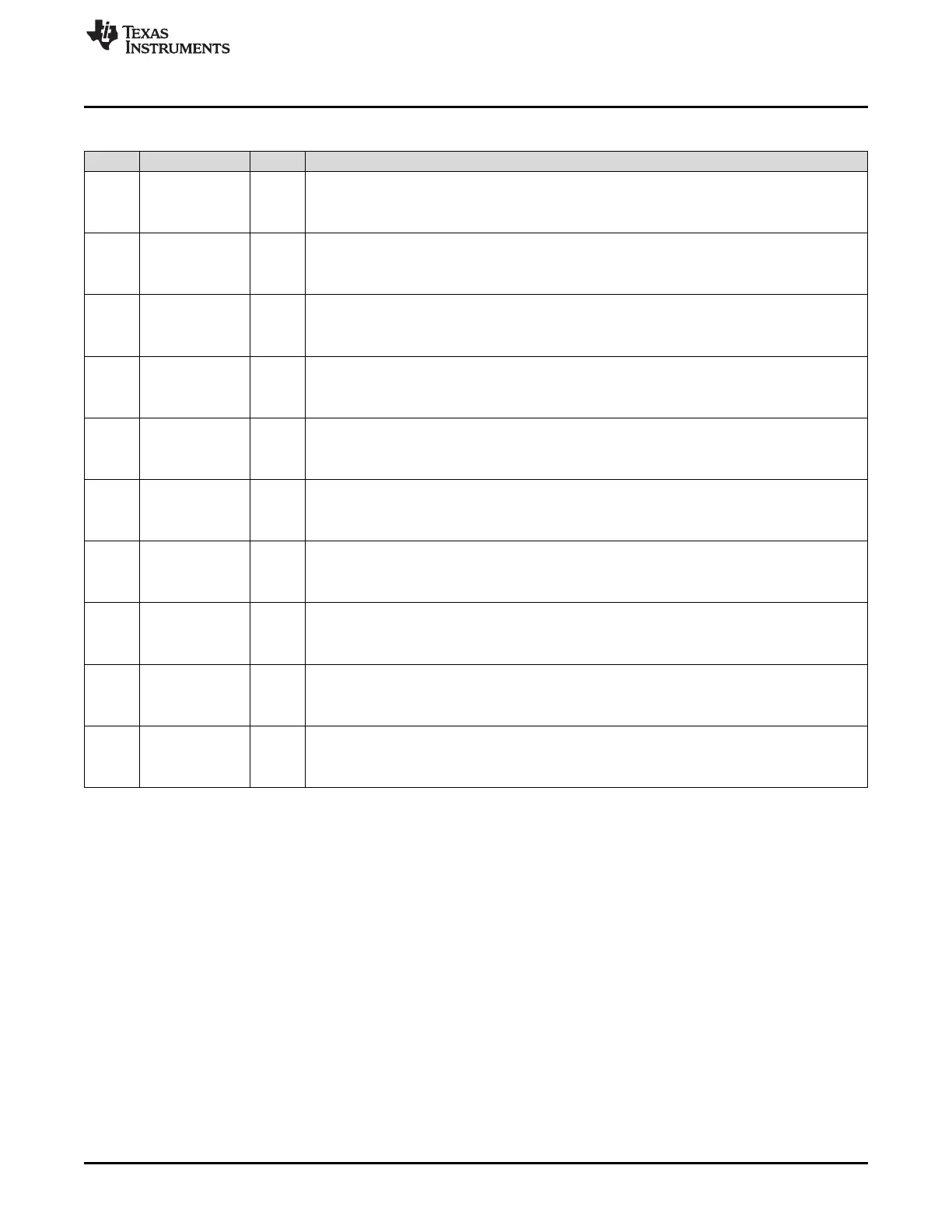

Table 26-99. Status Interrupt Line Select Register (SILS) Field Descriptions (continued)

Bit Field Value Description

9 TI1L Timer interrupt 1 line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

8 TI0L Timer interrupt 0 line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

7 NMVCL Network management vector changed interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

6 RFCLL Receive FIFO full interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

5 RFNEL Receive FIFO not empty interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

4 RXIL Receive interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

3 TXIL Transmit interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

2 CYCSL Cycle start interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

1 CASL Collision Avoidance symbol interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

0 WSTL Wakeup status interrupt line.

0 Interrupt is assigned to interrupt line CC_int0.

1 Interrupt is assigned to interrupt line CC_int1.

Loading...

Loading...