www.ti.com

FlexRay Module Registers

1351

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

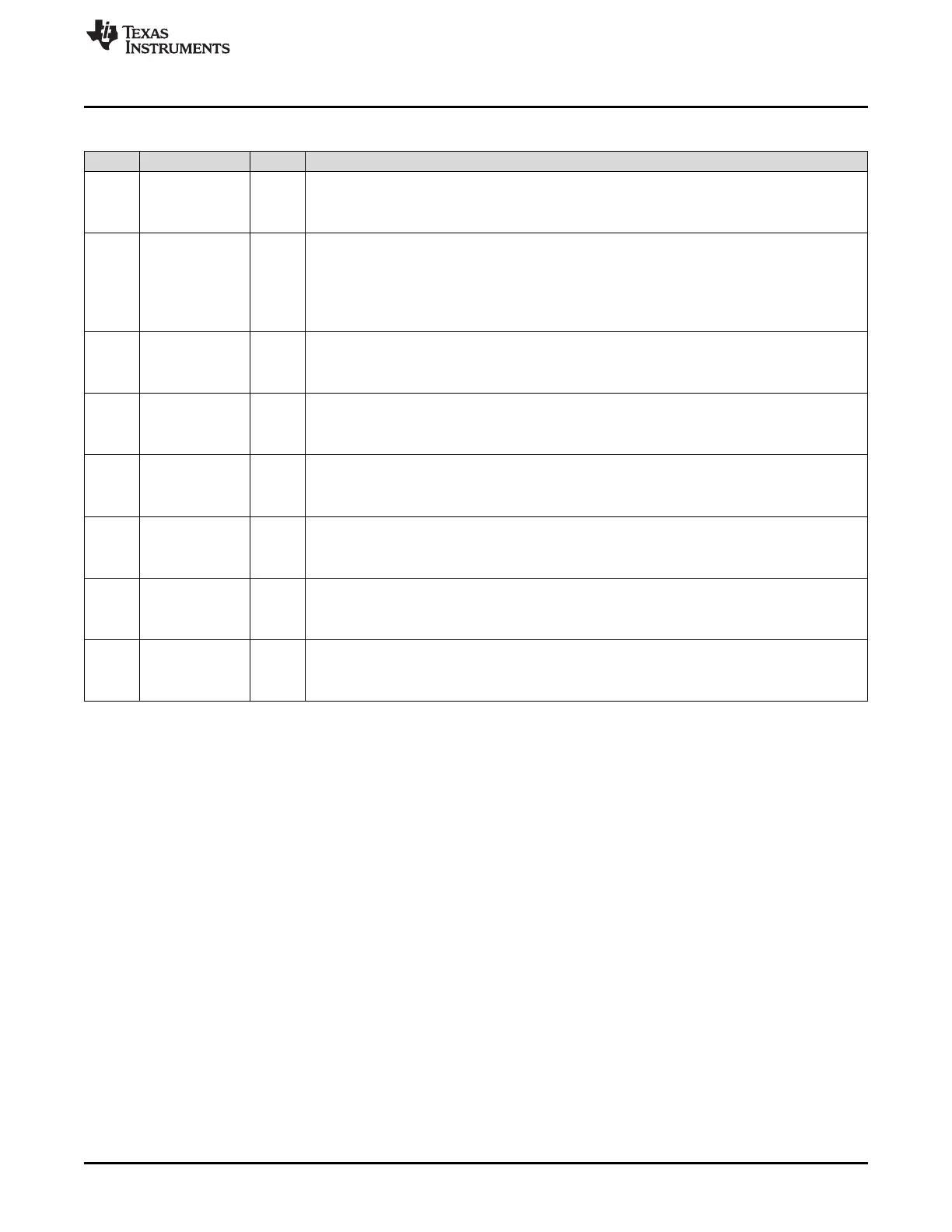

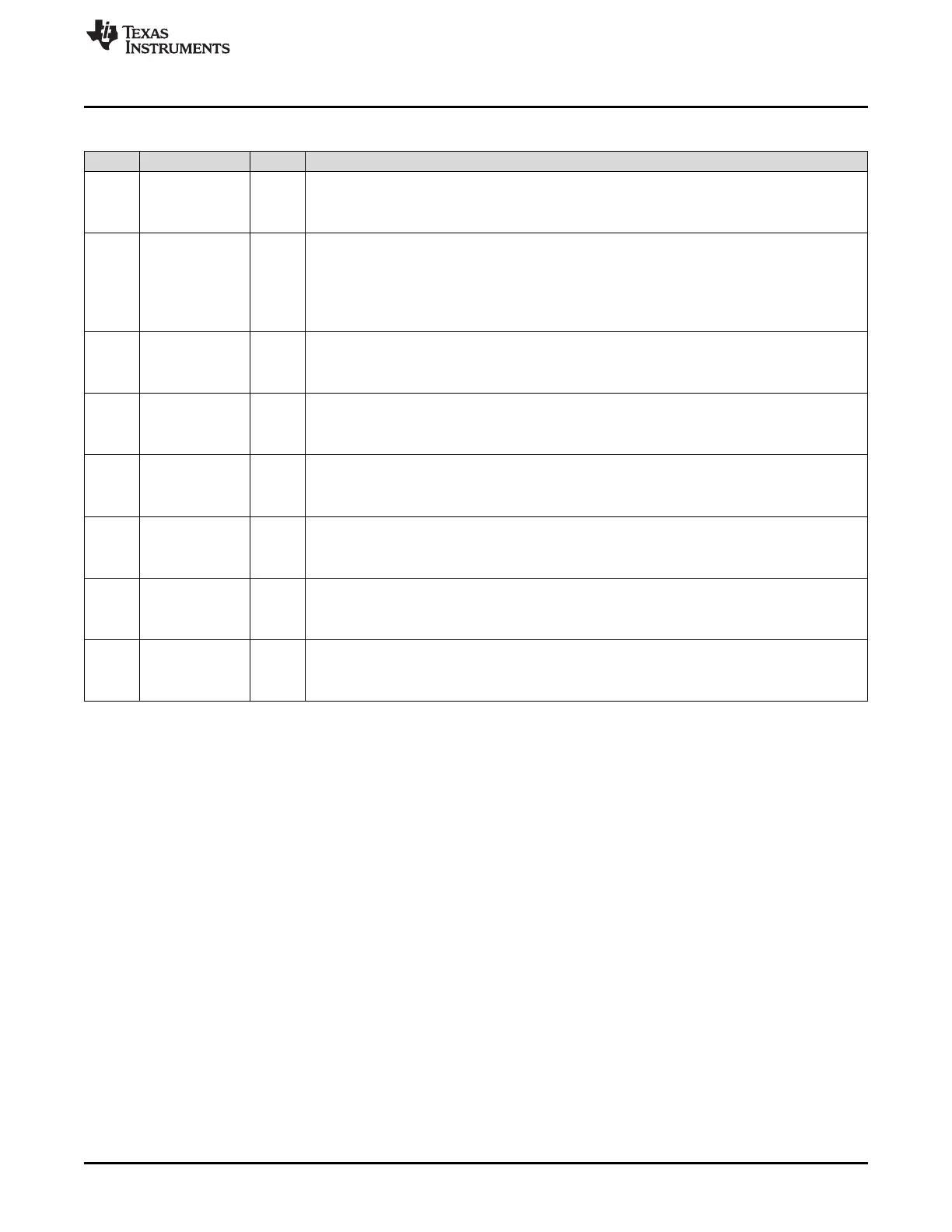

Table 26-100. Error Interrupt Set/Reset Register (EIES/EIER) Field Descriptions (continued)

Bit Field Value Description

7 RFOE Receive FIFO overrun interrupt enable.

0 Interrupt is disabled.

1 Receive FIFO overrun interrupt is enabled.

6 UCREE Uncorrectable RAM error interrupt enable. An uncorrectable RAM error can be caused by:

• an ECC single-bit error, if ECC single-bit error correction is disabled

• an ECC double-bit error

0 Interrupt is disabled.

1 Uncorrectable RAM error interrupt is enabled.

5 CCLE CHI command locked interrupt enable.

0 Interrupt is disabled.

1 CHI command locked interrupt is enabled.

4 CCFE Clock correction failure interrupt enable.

0 Interrupt is disabled.

1 Clock correction failure interrupt is enabled.

3 SFOE Sync frame overflow interrupt enable.

0 Interrupt is disabled.

1 Sync frame overflow interrupt is enabled.

2 SFBME Sync frames below minimum interrupt enable.

0 Interrupt is disabled.

1 Sync frames below minimum interrupt is enabled.

1 CNAE Command not Accepted interrupt enable.

0 Interrupt is disabled.

1 Command not valid interrupt is enabled.

0 PEMCE POC error mode changed interrupt enable.

0 Interrupt is disabled.

1 Protocol error mode changed interrupt is enabled.

Loading...

Loading...