www.ti.com

FlexRay Module Registers

1377

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

NOTE: CHI command RESET_STATUS_INDICATORS (SUCC1.CMD = Ah) resets flags FSI, HRQ,

CSNI, CSAI, the slot mode SLM, and the wakeup status WSV.

26.3.2.4.2 Communication Controller Error Vector (CCEV)

Reset by CHI command RESET_STATUS_INDICATORS or by transition from HALT to

DEFAULT_CONFIG state or when entering READY state.

Figure 26-147 and Table 26-126 illustrate this register.

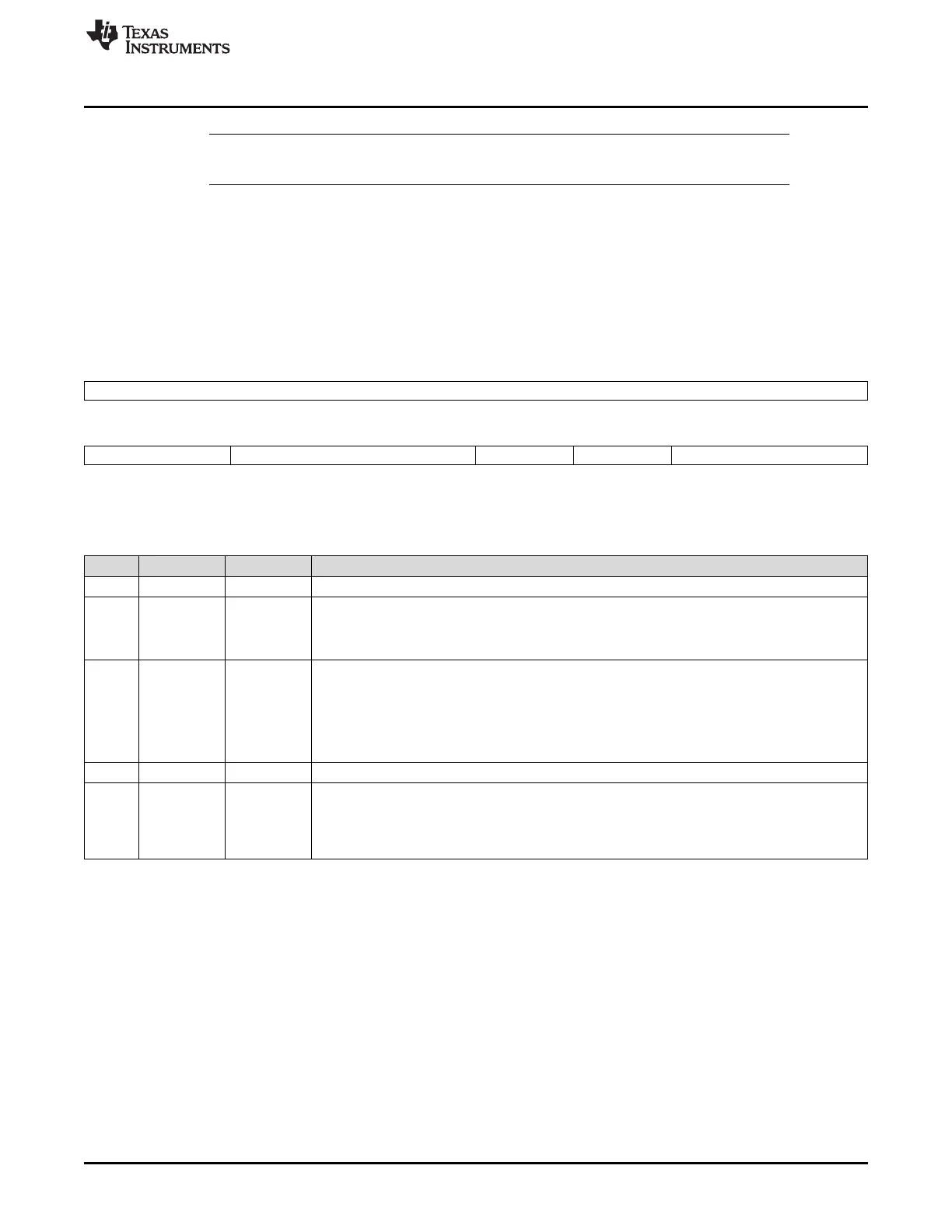

Figure 26-147. Communication Controller Error Vector Register (CCEV) [offset_CC = 104h]

31 16

Reserved

R-0

15 13 12 8 7 6 5 4 3 0

Reserved PTAC ERRM Reserved CCFC

R-0 R-0 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

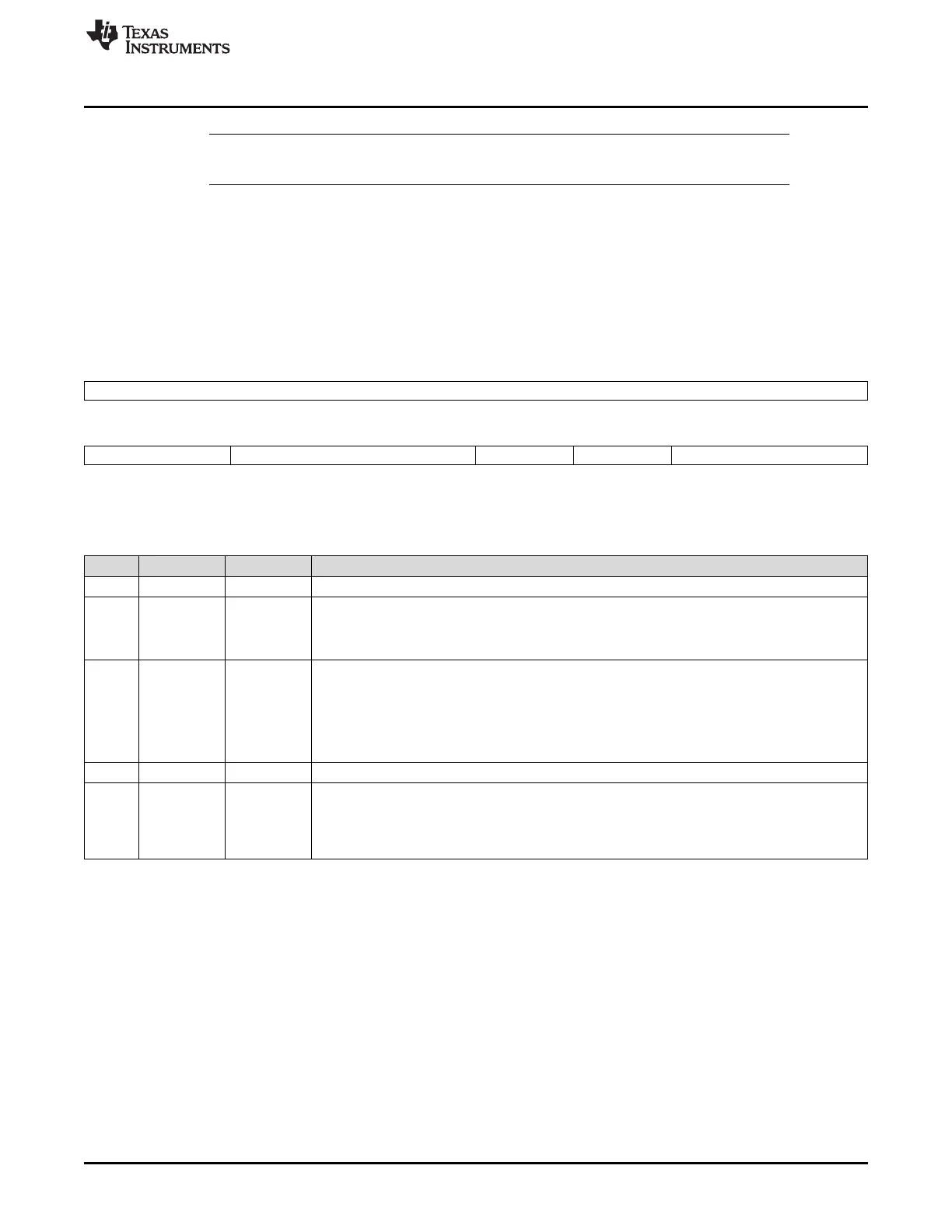

Table 26-126. Communication Controller Error Vector Register (CCEV) Field Descriptions

Bit Field Value Description

31-13 Reserved 0 Reads return 0. Writes have no effect.

12-8 PTAC 0-1Fh Passive to active count. Indicates the number of consecutive even / odd cycle pairs that have

passed with valid rate and offset correction terms, while the node is waiting to transit from

NORMAL_PASSIVE state to NORMAL_ACTIVE state. The transition takes place when PTAC

equals PTA - 1 as defined in the SUC configuration register 1.

7-6 ERRM Error mode. Indicates the actual error mode of the POC.

0 ACTIVE

1h PASSIVE

2h COMM_HALT

3h Reserved

5-4 Reserved 0 Reads return 0. Writes have no effect.

3-0 CCFC 0-Fh Clock correction failed counter. The clock correction failed counter is incremented by 1 at the end

of any odd communication cycle where either the missing offset correction error or missing rate

correction error are active. The clock correction failed counter is reset to 0 at the end of an odd

communication cycle if neither the offset correction failed nor the rate correction failed errors are

active. The clock correction failed counter stops at 15.

Loading...

Loading...