FlexRay Module Registers

www.ti.com

1390

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

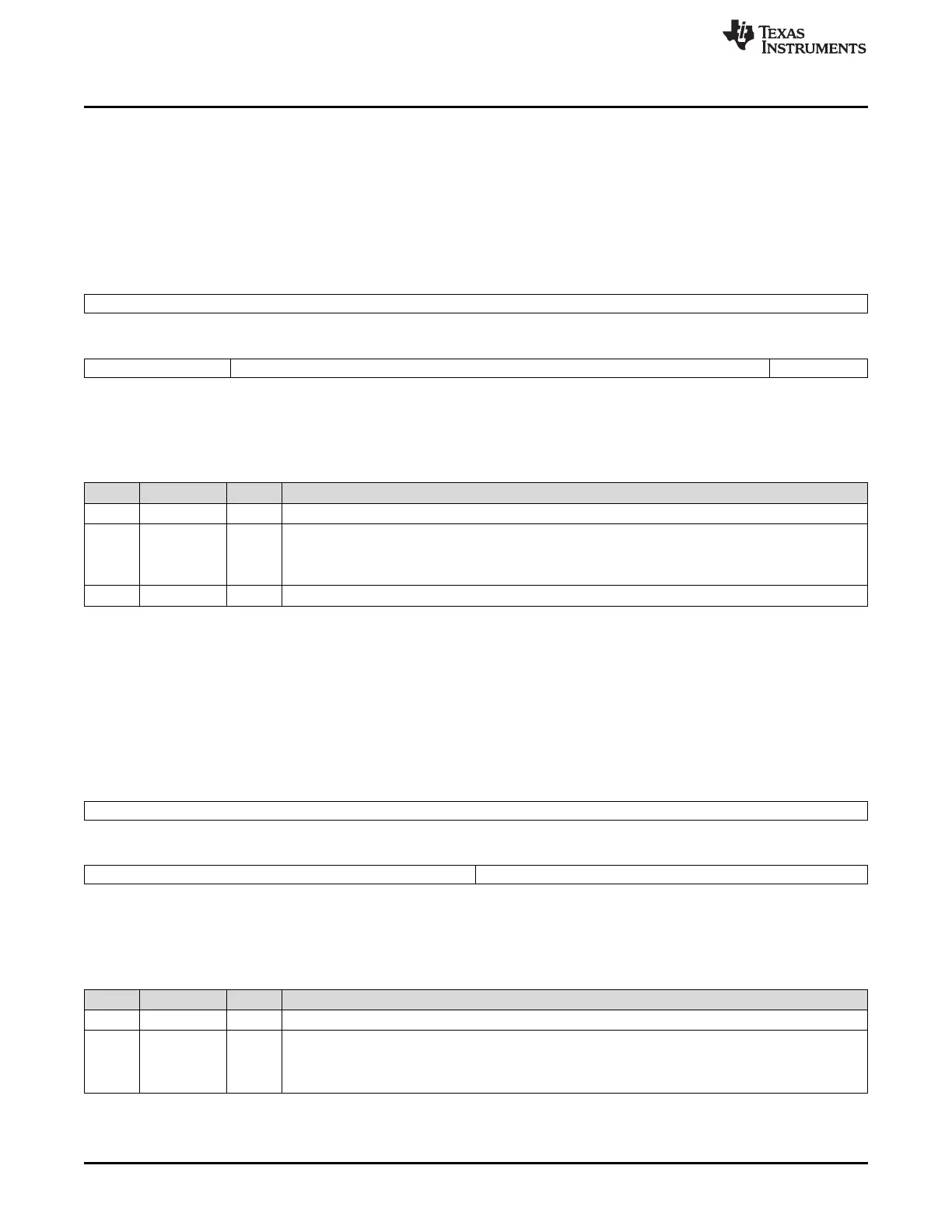

26.3.2.5.3 FIFO Rejection Filter Mask (FRFM)

The FIFO rejection filter mask specifies which of the corresponding frame ID filter bits are relevant for

rejection filtering. If a bit is set, it indicates that the state of the corresponding bit in the FRF register will

not be considered for rejection filtering. The FRFM register can be written during DEFAULT_CONFIG or

CONFIG state only.

Figure 26-160 and Table 26-140 illustrate this register.

Figure 26-160. FIFO Rejection Filter Mask Register (FRFM) [offset_CC = 308h]

31 16

Reserved

R-0

15 13 12 2 1 0

Reserved MFID* Reserved

R-0 R/W-0 R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset; *These bits can be updated in DEFAULT_CONFIG or CONFIG state

only

Table 26-140. FIFO Rejection Filter Mask Register (FRFM) Field Descriptions

Bit Field Value Description

31-13 Reserved 0 Reads return 0. Writes have no effect.

12-2 MFID Mask Frame ID Filter.

0 Corresponding frame ID filter bit is used for rejection filtering.

1 Ignore corresponding frame ID filter bit.

1-0 Reserved 0 Reads return 0. Writes have no effect.

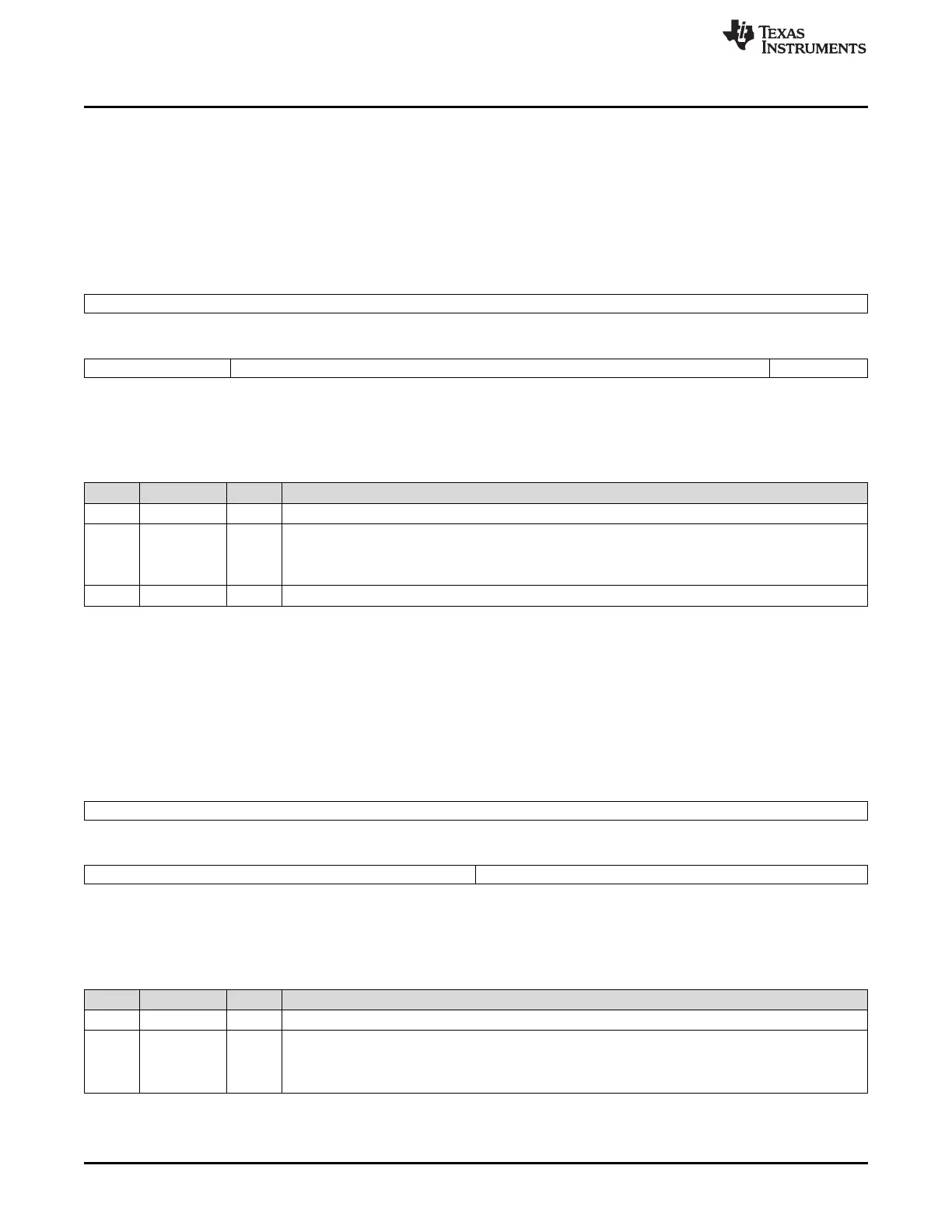

26.3.2.5.4 FIFO Critical Level (FCL)

The communication controller accepts modifications of the register in DEFAULT_CONFIG or CONFIG

state only.

Figure 26-161 and Table 26-141 illustrate this register.

Figure 26-161. FIFO Critical Level Register (FCL) [offset_CC = 30Ch]

31 16

Reserved

R-0

15 8 7 0

Reserved CL*

R-0 R/W-810h

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset; *These bits can be updated in DEFAULT_CONFIG or CONFIG state

only

Table 26-141. FIFO Critical Level Register (FCL) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reads return 0. Writes have no effect.

7-0 CL Critical Level. When the receive FIFO fill level FSR.RFFL is equal or greater than the critical level

configured by CL, the receive FIFO critical level flag FSR.RFCL is set. If CL is programmed to values >

128, bit FSR.RFCL is never set. When FSR.RFCL changes from 0 to 1 bit SIR.RFCL is set to 1, and if

enabled, an interrupt is generated.

Loading...

Loading...