www.ti.com

FlexRay Module Registers

1391

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

FlexRay Module

26.3.2.6 Message Buffer Status Registers

26.3.2.6.1 Message Handler Status (MHDS)

A flag is cleared by writing a 1 to the corresponding bit position. Writing a 0 has no effect on the flag. A

hardware reset will also clear the register.

Figure 26-162 and Table 26-142 illustrate this register.

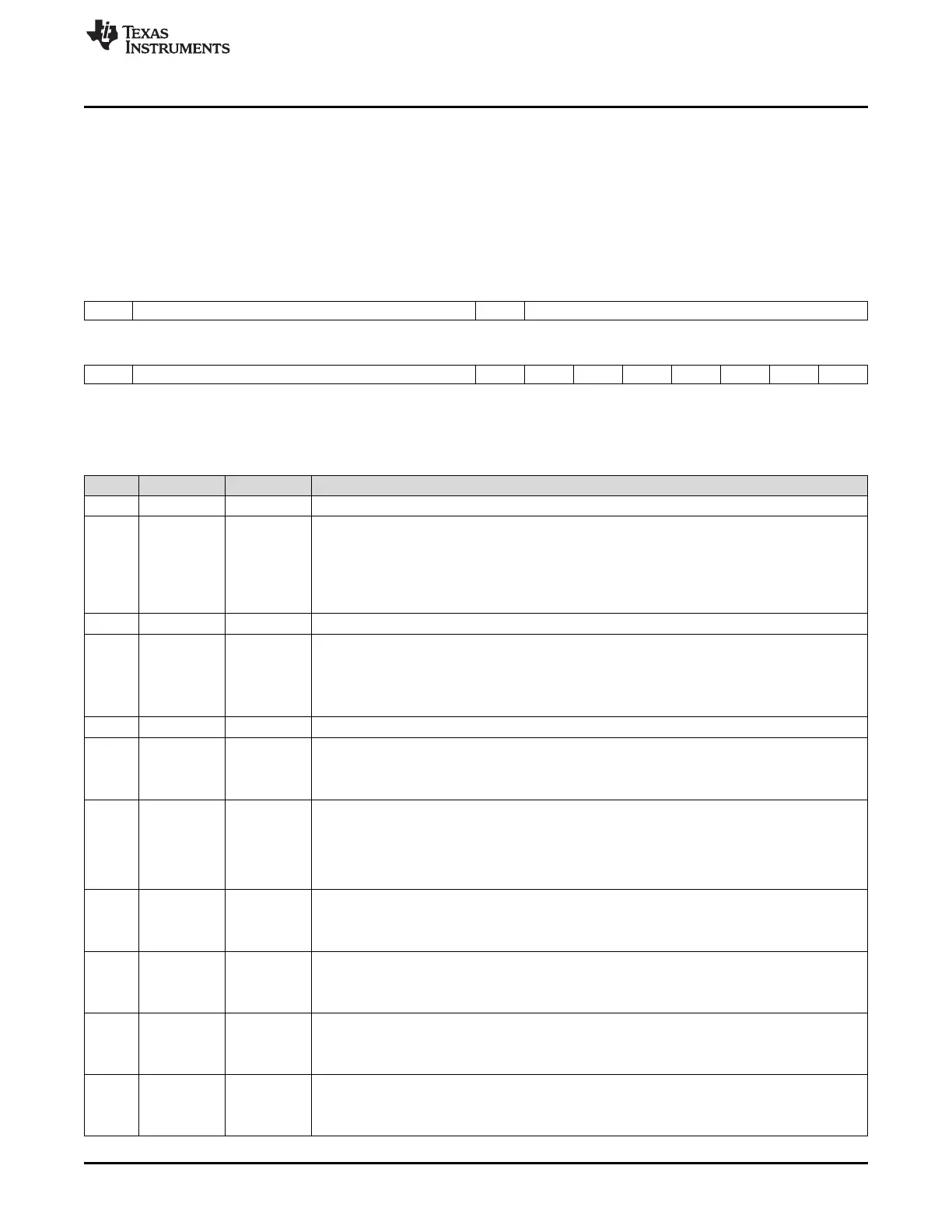

Figure 26-162. Message Handler Status (MHDS) [offset_CC = 310h]

31 30 24 23 22 16

Rsvd MBU Rsvd MBT

R-0 R-0 R-0 R-0

15 14 8 7 6 5 4 3 2 1 0

Rsvd FMB CRAM MFMB FMBD PTFB2 PTFB1 PMR POBF PIBF

R-0 R-0 R-1h R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

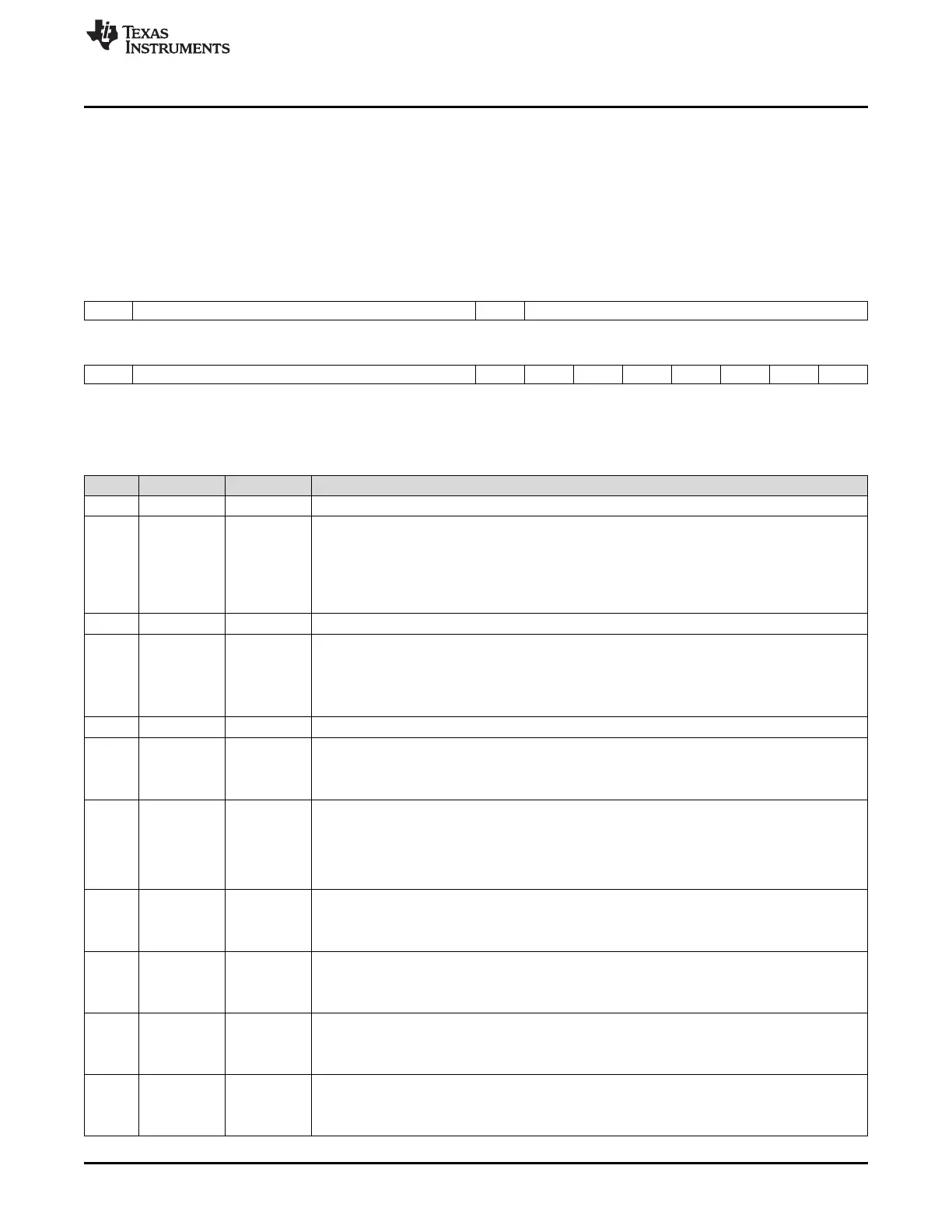

Table 26-142. Message Handler Status (MHDS) Field Descriptions

Bit Field Value Description

31 Reserved 0 Reads return 0. Writes have no effect.

30-24 MBU 0-7Fh Message buffer updated. Number of the message buffer that was updated last by the

communication controller. For this message buffer, the respective ND and/or MBC flag in the new

data 1...4 (NDAT1...4) and the message buffer status changed 1...4 (MBSC1...4) registers are also

set.

Note: MBU are reset when the communication controller leaves CONFIG state or enters

STARTUP state.

23 Reserved 0 Reads return 0. Writes have no effect.

22-16 MBT 0-7Fh Message buffer transmitted. Number of the last successfully transmitted message buffer. If the

message buffer is configured for single-shot mode, the respective TXR flag in the Transmission

request register 1...4 (TXRQ1..4) was reset.

Note: MBT are reset when the communication controller leaves CONFIG state or enters

STARTUP state.

15 Reserved 0 Reads return 0. Writes have no effect.

14-8 FMB 0-7Fh Faulty message buffer. An ECC multi-bit error occurred when reading from a message buffer or

when transferring data from Input Buffer or Transient Buffer 1,2 to the message buffer referenced

by FMB. This value is only valid when one of the flags PIBF, PMR, PTBF1, PTBF2, and flag

FMBD is set. Is not updated while flag FMBD is set.

7 CRAM Clear all internal RAMs. Signals that execution of the controller host interface command

CLEAR_RAMS is ongoing (all bits of all internal RAM blocks are written to 0). The bit is set by

hardware reset or by the controller host interface command CLEAR_RAMS.

0 No execution of the controller host interface command CLEAR_RAMS.

1 Execution of the controller host interface command CLEAR_RAMS is ongoing.

6 MFMB Multiple faulty message buffers detected.

0 No additional faulty message buffer.

1 Another faulty message buffer was detected while flag FMBD is set.

5 FMBD Faulty message buffer detected.

0 No faulty message buffer.

1 Message buffer referenced by FMB holds faulty data due to an ECC multi-bit error.

4 PTBF2 ECC error transient buffer RAM B.

0 No ECC multi-bit error.

1 ECC multi-bit error occurred when reading transient buffer RAM B.

3 PTBF1 ECC error transient buffer RAM A.

0 No ECC multi-bit error.

1 ECC multi-bit error occurred when reading transient buffer RAM A.

Loading...

Loading...