DCAN Control Registers

www.ti.com

1462

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Controller Area Network (DCAN) Module

27.17.4 Bit Timing Register (DCAN BTR)

NOTE: This register is only writable if CCE and Init bits in the CAN Control Register are set.

The CAN bit time may be programmed in the range of 8 to 25 time quanta.

The CAN time quantum may be programmed in the range of 1 to 1024 CAN_CLK periods.

With a CAN_CLK of 8 MHz and BRPE = 00, the reset value of 2301h configures the DCAN for a bit rate of

500kBit/s.

For details see Section 27.3.2.1.

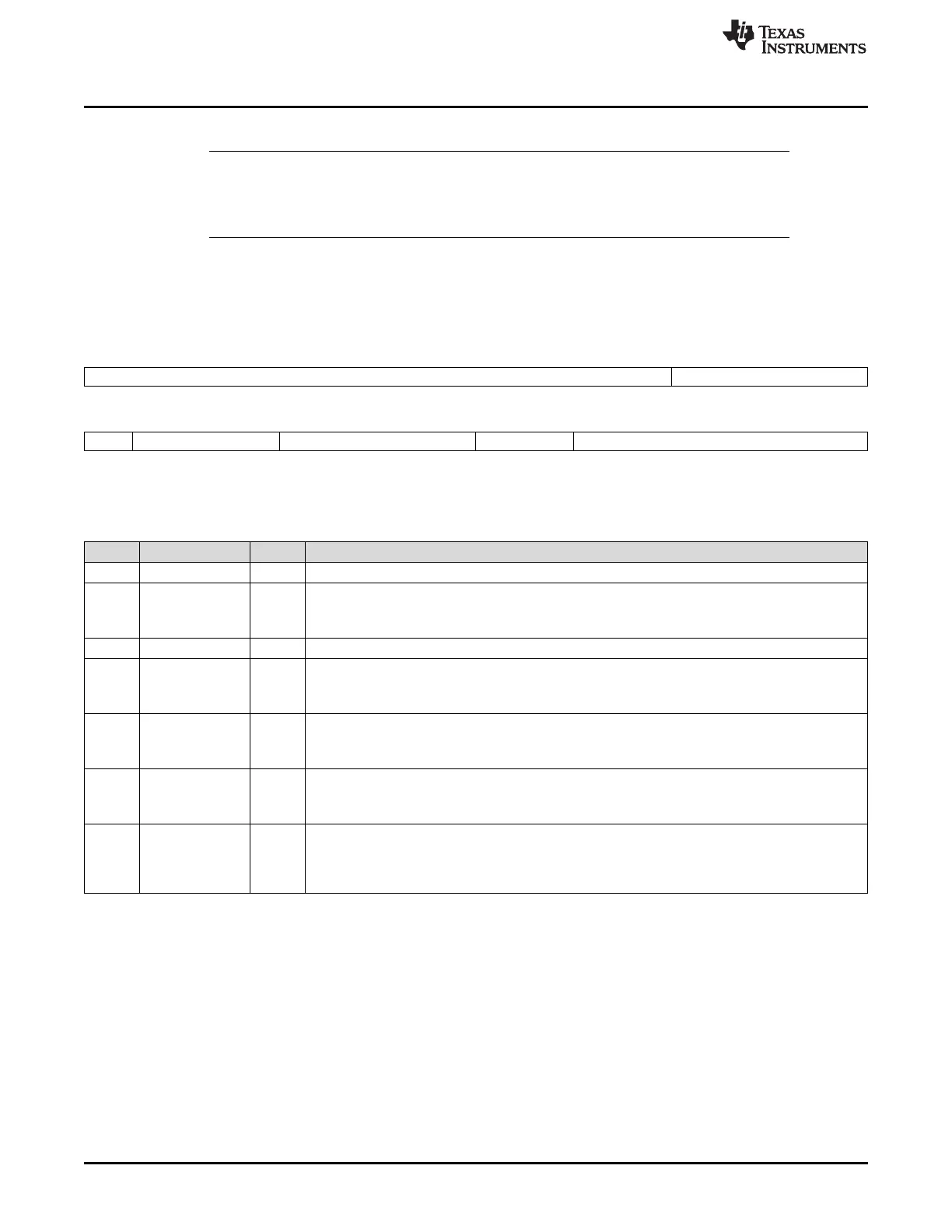

Figure 27-23. Bit Timing Register (DCAN BTR) [offset = 0Ch]

31 20 19 16

Reserved BRPE

R-0 R/WP-0

15 14 12 11 8 7 6 5 0

Rsvd TSeg2 TSeg1 SJW BRP

R-0 R/WP-2h R/WP-3h R/WP-0 R/WP-1h

LEGEND: R/W = Read/Write; R = Read only; WP = Write Protected by CCE bit; -n = value after reset

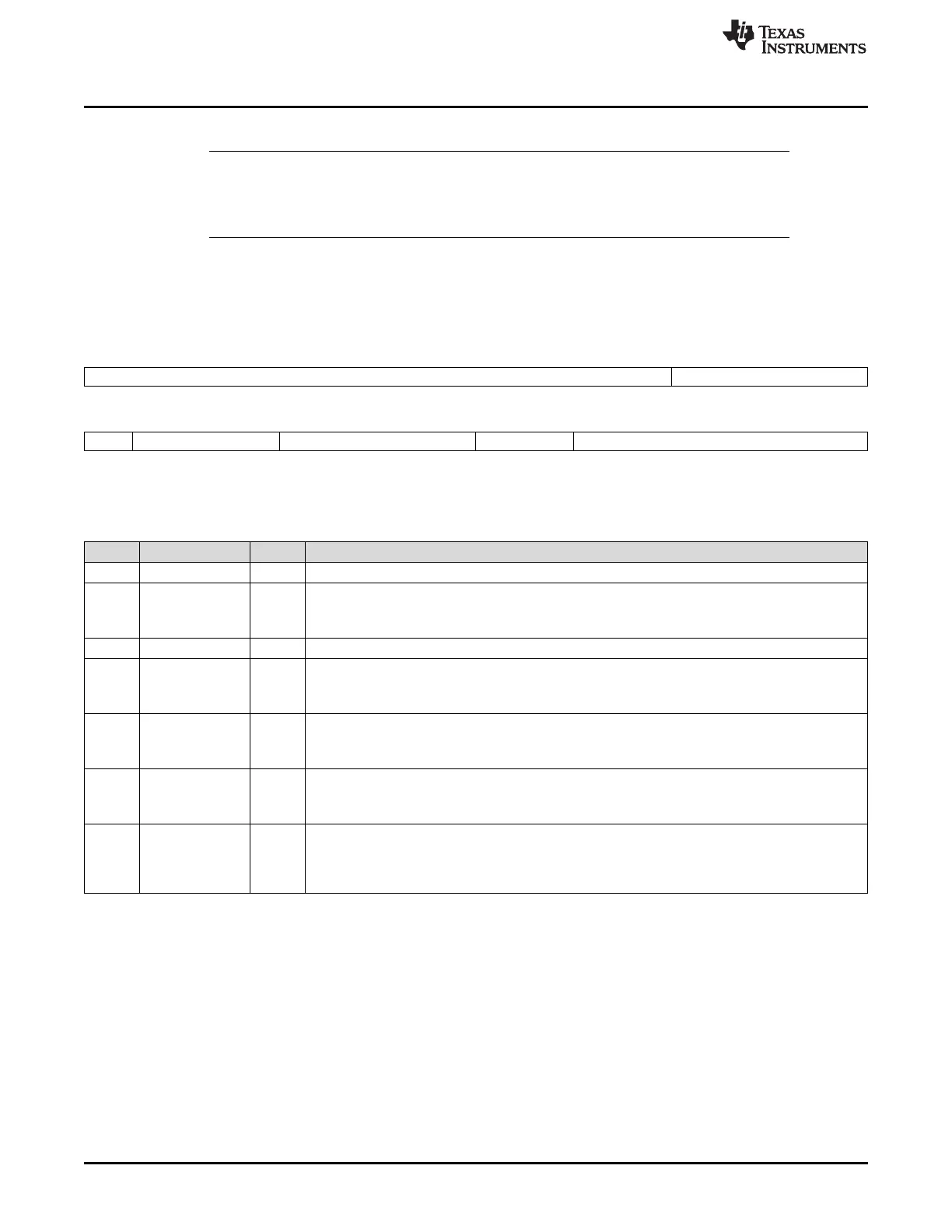

Table 27-10. Bit Timing Register (DCAN BTR) Field Descriptions

Bit Field Value Description

31-20 Reserved 0 These bits are always read as 0. Writes have no effect.

BRPE 0-Fh Baud Rate Prescaler Extension.

Valid programmed values are 0 to 15. By programming BRPE the Baud Rate Prescaler can be

extended to values up to 1024.

15 Reserved 0 This bit is always read as 0. Writes have no effect.

14-12 TSeg2 0-7h Time segment after the sample point.

Valid programmed values are 0 to 7. The actual TSeg2 value that is interpreted for the Bit Timing

will be the programmed TSeg2 value + 1.

11-8 TSeg1 1h-Fh Time segment before the sample point.

Valid programmed values are 1 to 15. The actual TSeg1 value interpreted for the Bit Timing will be

the programmed TSeg1 value + 1.

7-6 SJW 0-3h Synchronization Jump Width

Valid programmed values are 0 to 3. The actual SJW value interpreted for the Synchronization will

be the programmed SJW value + 1.

5-0 BRP 0-3Fh Baud Rate Prescaler

Value by which the CAN_CLK frequency is divided for generating the bit time quanta. The bit time

is built up from a multiple of this quanta. Valid programmed values are 0 to 63. The actual BRP

value interpreted for the Bit Timing will be the programmed BRP value + 1.

Loading...

Loading...