Control Registers

www.ti.com

1574

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Multi-Buffered Serial Peripheral Interface Module (MibSPI) with Parallel Pin

Option (MibSPIP)

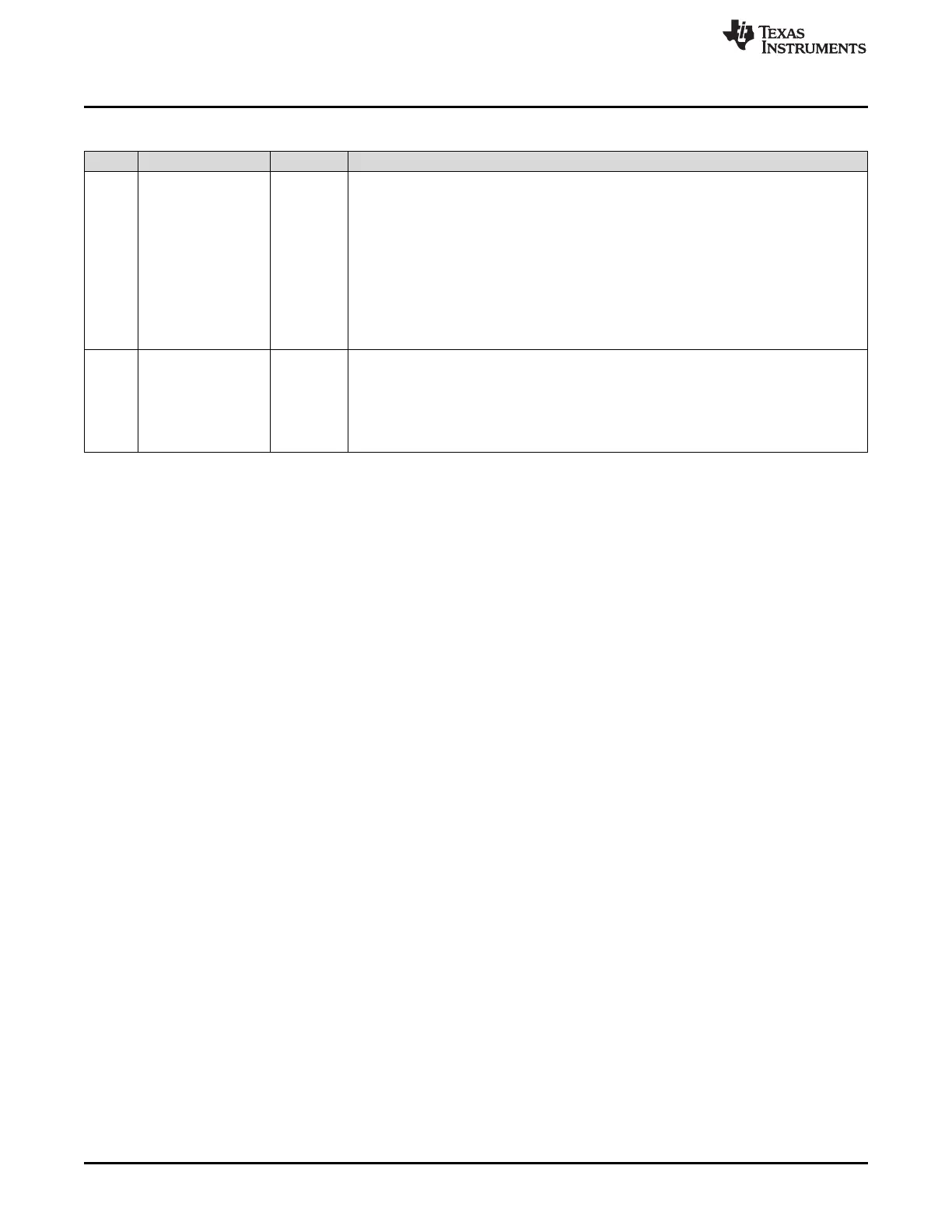

Table 28-34. SPI Parallel/Modulo Mode Control Register (SPIPMCTRL) Field Descriptions (continued)

Bit Field Value Description

4-2 MMODE0 These bits determine whether the SPI/MibSPI operates with 1, 2, 4, 5, or 6 data lines (if

modulo option is supported by the module).

0 1-data line mode (default). (PMODE0 should be set to 00).

1h 2-data line mode (PMODE0 should be set to 00).

2h 3-data line mode (PMODE0 should be set to 00).

3h 4-data line mode (PMODE0 should be set to 00).

4h 5-data line mode (PMODE0 should be set to 00).

5h 6-data line mode (PMODE0 should be set to 01).

6h-7h Reserved

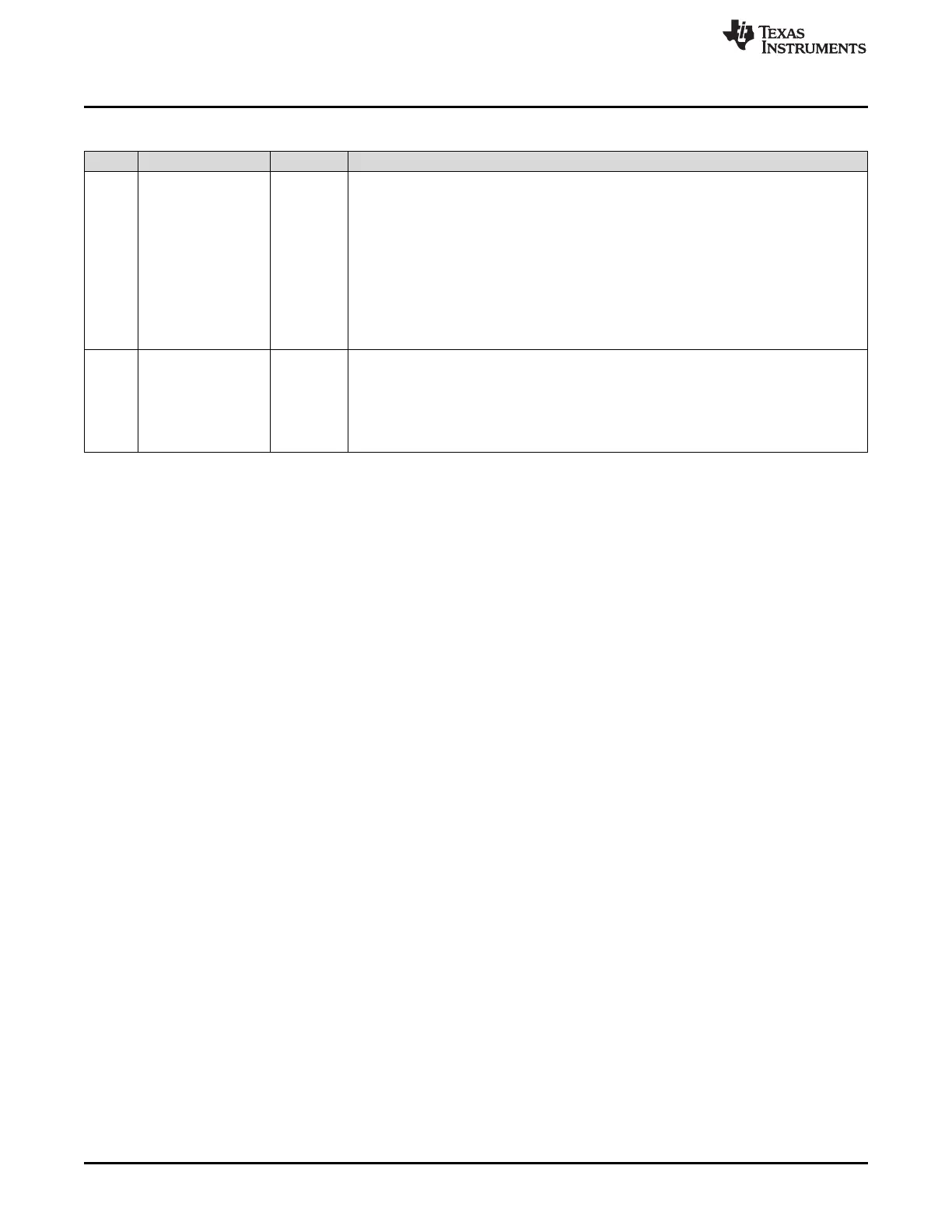

1-0 PMODE0 Parallel mode bits determine whether the SPI/MibSPI operates with 1, 2, 4, or 8 data lines.

0 Normal operation/1-data line (MMODE0 should be set to 000).

1h 2-data line mode (MMODE0 should be set to 000).

2h 4-data line mode (MMODE0 should be set to 000).

3h 8-data line mode (MMODE0 should be set to 000).

Loading...

Loading...