www.ti.com

Control Registers

1575

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Multi-Buffered Serial Peripheral Interface Module (MibSPI) with Parallel Pin

Option (MibSPIP)

NOTE: Accessibility of Registers

Registers from this offset address onwards are not accessible in SPI compatibility mode.

They are accessible only in the multi-buffer mode.

28.3.26 Multi-buffer Mode Enable Register (MIBSPIE)

NOTE: Accessibility of Multi-Buffer RAM

The multi-buffer RAM is not accessible unless the MSPIENA bit is set to 1. The only

exception to this is in test mode, where, by setting RXRAMACCESS to 1, the multi-buffer

RAM can be fully accessed for both read and write.

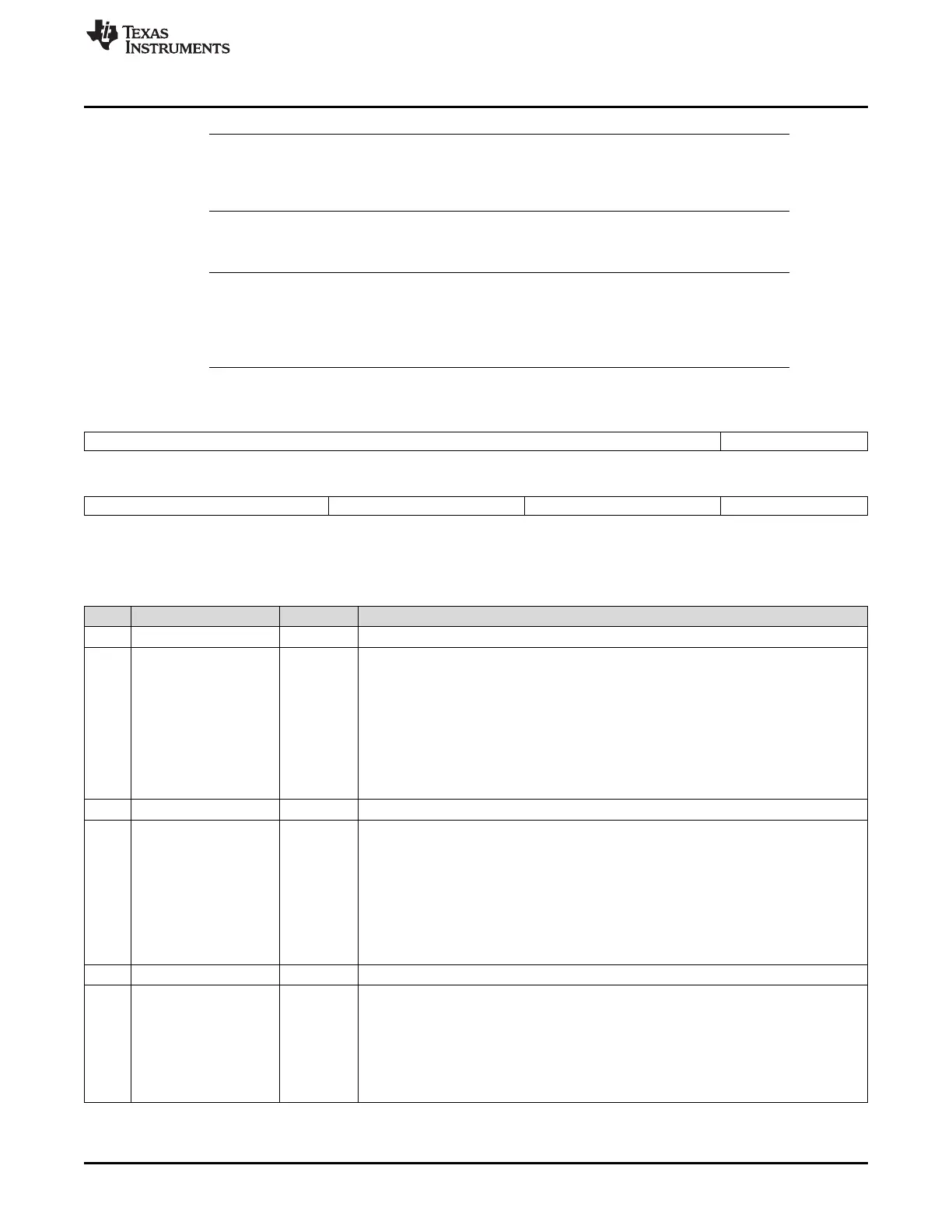

Figure 28-61. Multi-buffer Mode Enable Register (MIBSPIE) [offset = 70h]

31 17 16

Reserved RXRAM_ACCESS

R-0 R/WP-0

15 12 11 10 9 8 7 1 0

Reserved EXTENDED_BUF_ENA Reserved MSPIENA

R-0 R/WP-5h R/WP-0

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privilege mode only; -n = value after reset

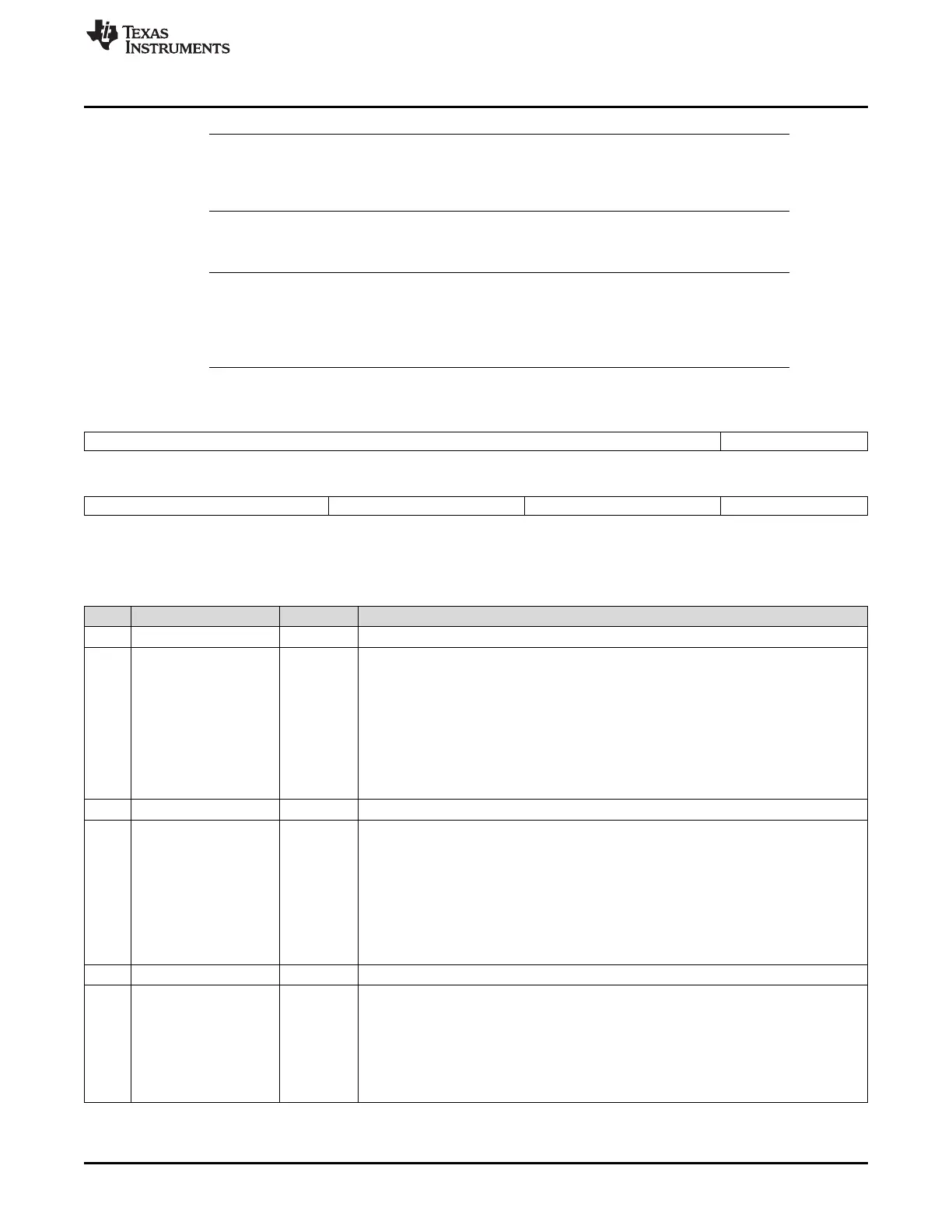

Table 28-35. Multi-buffer Mode Enable Register (MIBSPIE) Field Descriptions

Bit Field Value Description

31-17 Reserved 0 Reads return 0. Writes have no effect.

16 RXRAM_ACCESS Receive-RAM access control. During normal operating mode of SPI, the receive

data/status portion of multi-buffer RAM is read-only. To enable testing of receive RAM,

direct read/write access is enabled by setting this bit.

0 The RX portion of multi-buffer RAM is not writable by the CPU.

1 The whole of multi-buffer RAM is fully accessible for read/write by the CPU.

Note: The RX RAM ACCESS bit remains 0 after reset and it should remain set to 0

at all times, except when testing the RAM. SPI should be given a local reset by

using the nRESET (SPIGCR0[0]) bit after RAM testing is performed so that the

multi-buffer RAM gets re-initialized.

15-12 Reserved 0 Reads return 0. Writes have no effect.

11-8 EXTENDED_BUF_ENA

Enables the support for 256 buffers. By default MibSPI supports up to 128 buffers for both

TX and RX. Refer to the device specific datasheet if 256 buffer extension is implemented

for the specific MibSPI instance in the device.

5h Write: Disables the Extended Buffer mode - MibSPI supports only 128 buffers (default).

Ah Write: Enables the Extended Buffer mode - up to 256 buffers can be used.

all others All other values - writes are ignored and the values are not updated into this field. The

state of the feature remains unchanged.

Read: Returns the current value of this field.

7-1 Reserved 0 Reads return 0. Writes have no effect.

0 MSPIENA Multi-buffer mode enable. After power-up or reset, MSPIENA remains cleared, which

means that the SPI runs in compatibility mode by default. If multi-buffer mode is desired,

this register should be configured first after configuring the SPIGCR0 register. If MSPIENA

is not set to 1, the multi-buffer mode registers are not writable.

0 The SPI runs in compatibility mode, that is, in this mode the MibSPI is fully code-

compliant to the standard device SPI. No multi-buffered-mode features are supported.

1 The SPI is configured to run in multi-buffer mode.

Loading...

Loading...