Control Registers

www.ti.com

1590

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Multi-Buffered Serial Peripheral Interface Module (MibSPI) with Parallel Pin

Option (MibSPIP)

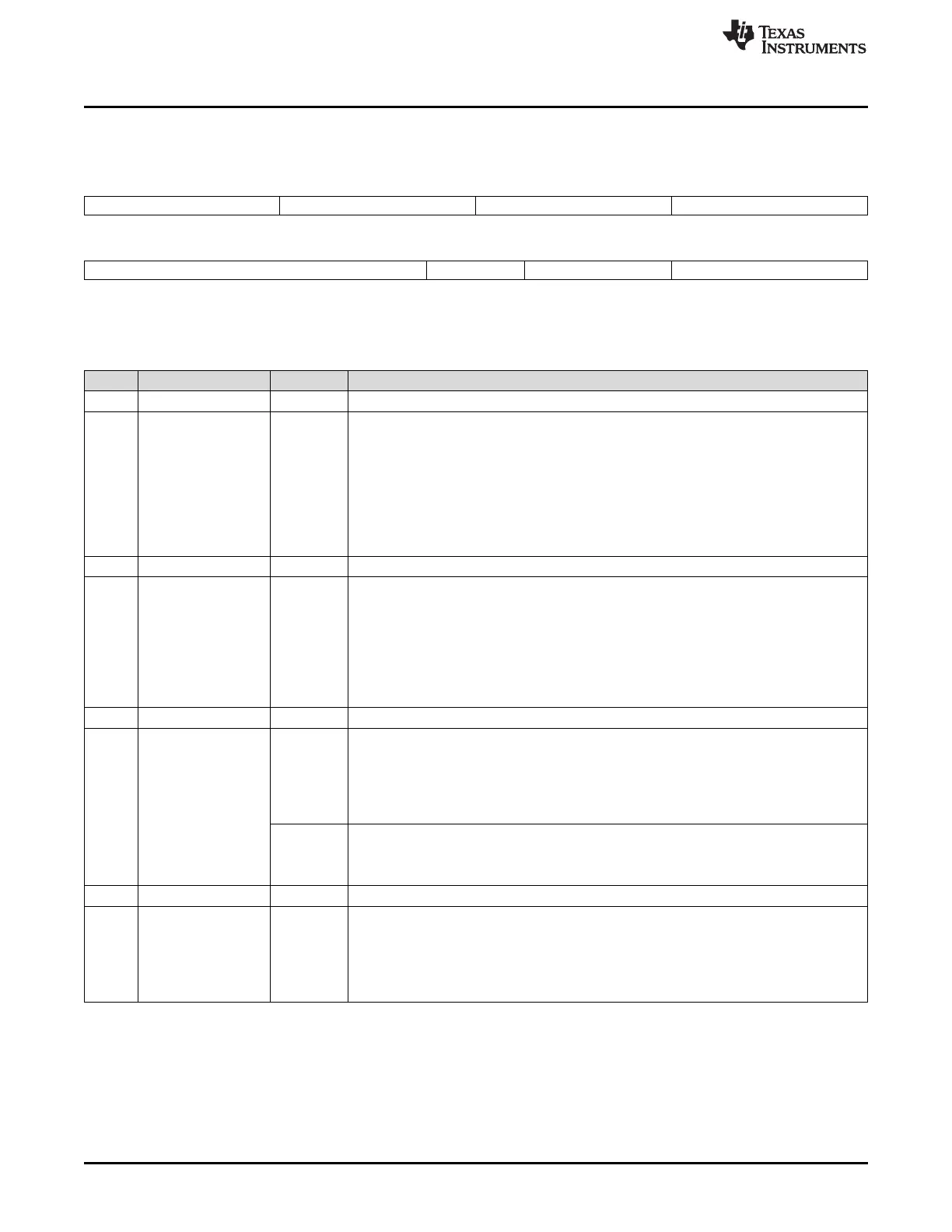

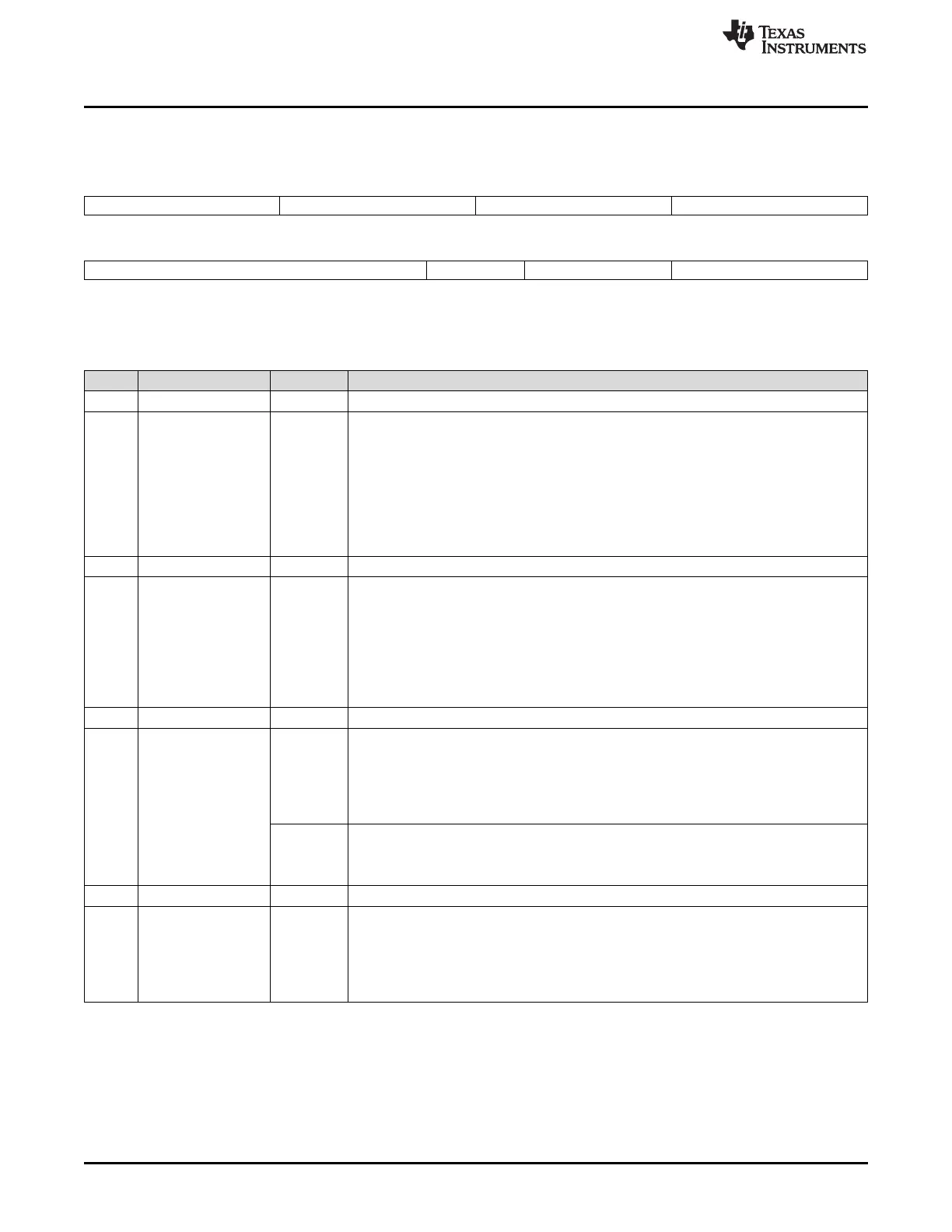

28.3.38 Parity/ECC Control Register (PAR_ECC_CTRL)

Figure 28-74. Parity/ECC Control Register (PAR_ECC_CTRL) [offset = 120]

31 28 27 24 23 20 19 16

Reserved SBE_EVT_EN Reserved EDAC_MODE

R-0 R/W-5h R-0 R/WP-Ah

15 9 8 7 4 3 0

Reserved PTESTEN Reserved EDEN

R-0 R/WP-0 R-0 R/W-5h

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privilege mode only; -n = value after reset

Table 28-47. MibSPI Parity/ECC Control Register (PAR_ECC_CTRL) Field Descriptions

Bit Field Value Description

31-28 Reserved 0 Reads return 0. Writes have no effect.

27-24 SBE_EVT_EN Single-Bit Error Event Enable This bit controls the generation of error signaling (on

MIBSPI_SBERR port) whenever a Single-Bit Error (SBE) is detected on TXRAM/RXRAM.

This signal can be used to generate interrupt if required.

5h Write: Disable Error Event indication upon detection of SBE on TXRAM/RXRAM.

Ah Write: Enable Error Event upon detection of SBE on TXRAM/RXRAM.

All other values - writes are ignored and the values are not updated into this field. The state

of the feature remains unchanged.

Read: Returns the current value of the field.

23-20 Reserved 0 Reads return 0. Writes have no effect.

19-16 EDAC_MODE These bits determine whether Single-Bit Errors (SBE) detected by the SECDED block will

be corrected or not.

5h Write: Disable correction of SBE detected by the SECDED block.

Ah Write: Enable correction of SBE detected by the SECDED block.

All other values - writes are ignored and the values are not updated into this field. The state

of the feature remains unchanged.

Read: Returns the current value of the field.

15-9 Reserved 0 Reads return 0. Writes have no effect.

8 PTESTEN Parity/ECC memory test enable. This bit, maps the parity/ECC bits corresponding to multi-

buffer RAM locations into the peripheral RAM frame to make them accessible by the CPU.

User and privilege mode (read):

0 Parity/ECC bits are not memory-mapped.

1 Parity/ECC bits are memory-mapped.

Privilege mode (write):

0 Disable memory-mapping of Parity/ECC locations.

1 Enable memory-mapping of Parity/ECC locations.

7-4 Reserved 0 Reads return 0. Writes have no effect.

3-0 EDEN Error Detection Enable These bits enable Parity/ECC error detection.

5h Write: Disable Parity/ECC error detection logic (default).

All other

values

Write: Enable Parity/ECC error detection logic.

Read: Returns the current value of this field.

Loading...

Loading...