www.ti.com

Control Registers

1601

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Multi-Buffered Serial Peripheral Interface Module (MibSPI) with Parallel Pin

Option (MibSPIP)

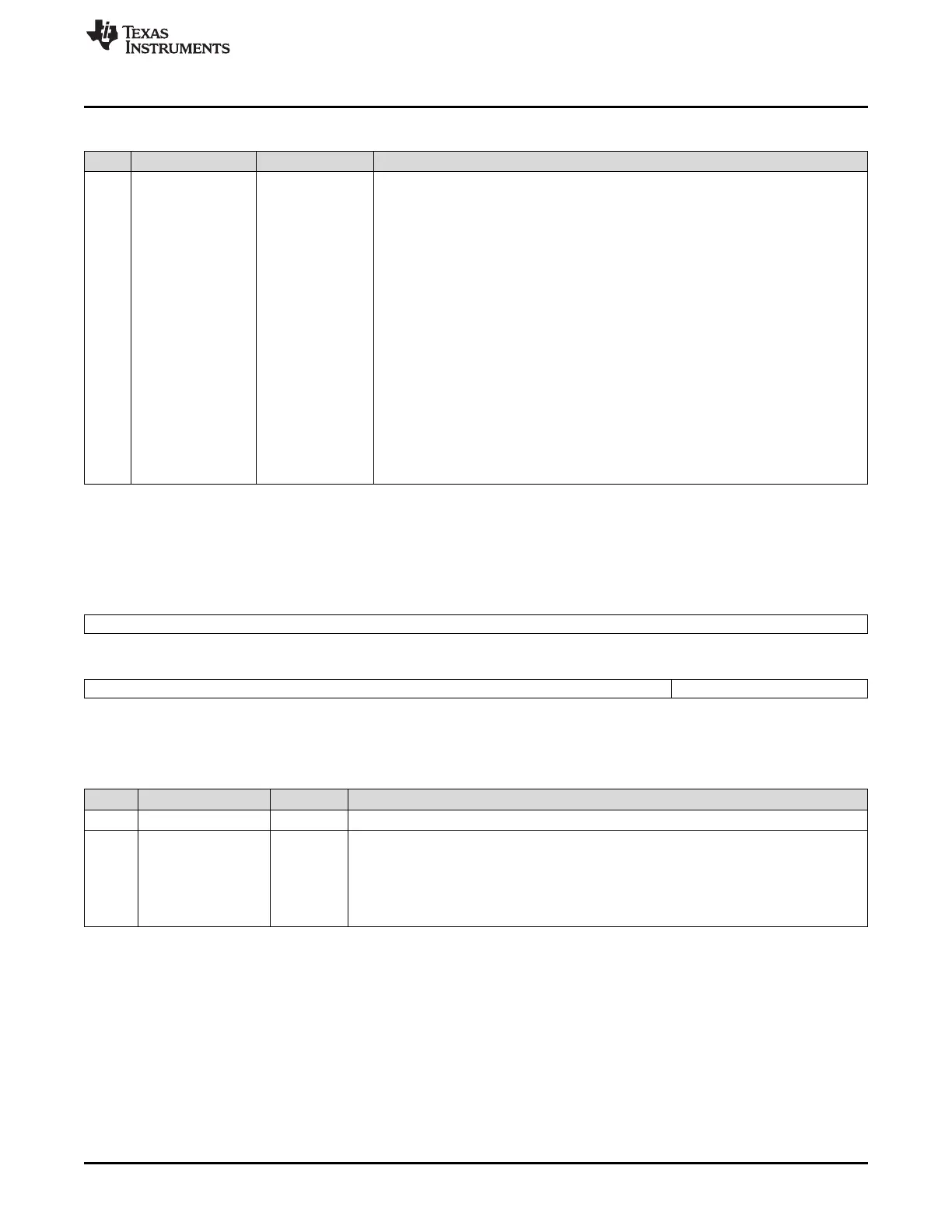

Table 28-56. SPI Extended Prescale Register 2 (EXTENDED_PRESCALE2) Field Descriptions (continued)

Bit Field Value Description

10-0 EPRESCALE_FMT2 0-7FFh EPRESCALE_FMT2. Extended Prescale value for SPIFMT2. EPRESCALE_FMT2

determines the bit transfer rate of data format 2, if the SPI/MibSPI is the network

master. EPRESCALE_FMT2 is use to derive SPICLK from VCLK. If the SPI is

configured as slave, EPRESCALE_FMT2 does not need to be configured. These

EPRESCALE_FMT2(7:0) bits and PRESCALE2 bits of SPIFMT2 register will point to

the same physically implemented register. The clock rate for data format 2 can be

calculated as:

BR

Format2

= VCLK / (EPRESCALE_FMT2 + 1)

Write: This register field should be written if a SPICLK prescaler of more VCLK/256 is

required. This field provides a prescaler of up to VCLK/2048 for SPICLK. Writing to this

register field will also get reflected in SPIFMT2(15:8).

Read: Reading this field will reflect the PRESCALE value based on the last written

register field, that is, EXTENDED_PRESCALE2(10:0) or SPIFMT2(15:8) register.

Note: If Extended Prescaler is required, it should be ensured that

EXTENDED_PRESCALE2 register is programmed after SPIFMT2 register is

programmed. This is to ensure that the final SPICLK prescale value is controlled

by EXTENDED_PRESCALE2 register when a prescale of more 256 is intended on

SPICLK. Writing to PRESCALE2 field of SPIFMT2 will automatically clear

EPRESCALE_FMT2(10:8) bits to 000 so that the integrity of PRESCALE value is

maintained.

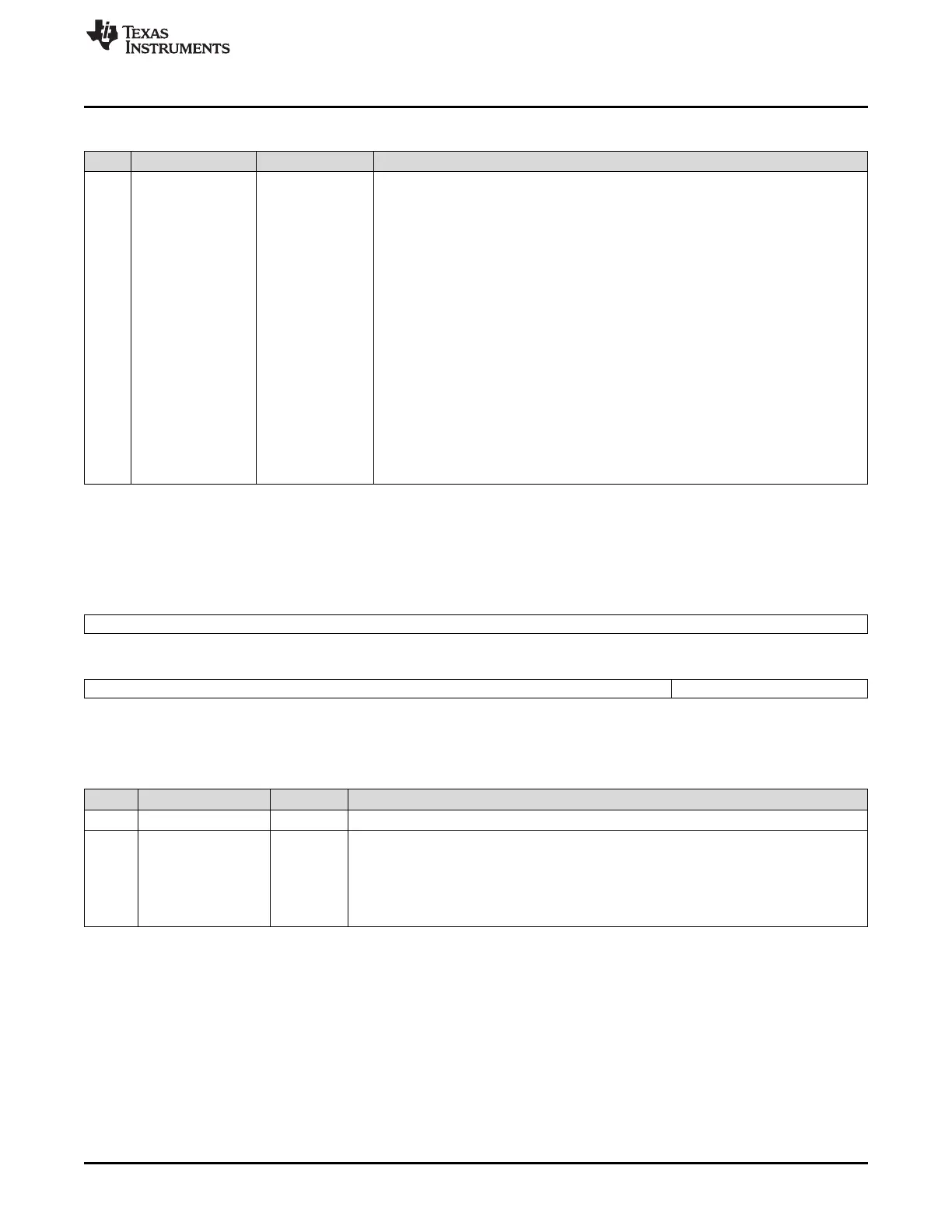

28.3.46 ECC Diagnostic Control Register (ECCDIAG_CTRL)

Figure 28-82. ECC Diagnostic Control Register (ECCDIAG_CTRL) [offset = 140h]

31 16

Reserved

R-0

15 4 3 0

Reserved ECCDIAG_EN

R-0 R/WP-Ah

LEGEND: R/W = Read/Write; R = Read only; WP = Write in privilege mode only; -n = value after reset

Table 28-57. ECC Diagnostic Control Register (ECCDIAG_CTRL) Field Descriptions

Bit Field Value Description

31-4 Reserved Reads return 0. Writes have no effect.

3-0 ECCDIAG_EN ECC Diagnostic mode Enable Key bits.

5h Write: Diagnostic mode is enabled. Writes and reads from ECC bits allowed from the ECC

address space.

All other

values

Write: Diagnostic mode is disabled. No writes to ECC bits are ignored.

Read: Returns 0.

Loading...

Loading...