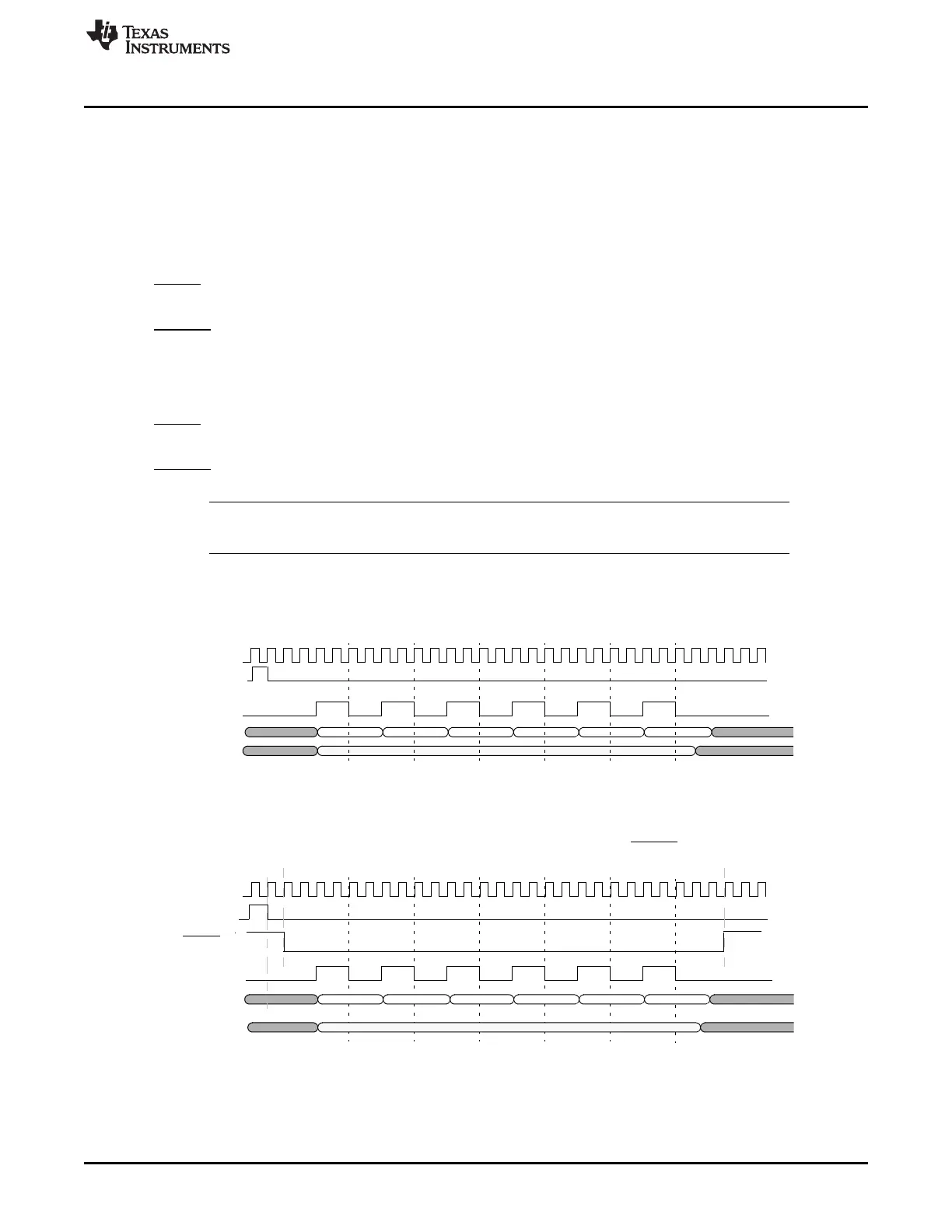

VCLK

SPICS

SPICLK

SPISIMO

SPISOMI

* Dotted vertical lines indicate the receive edges

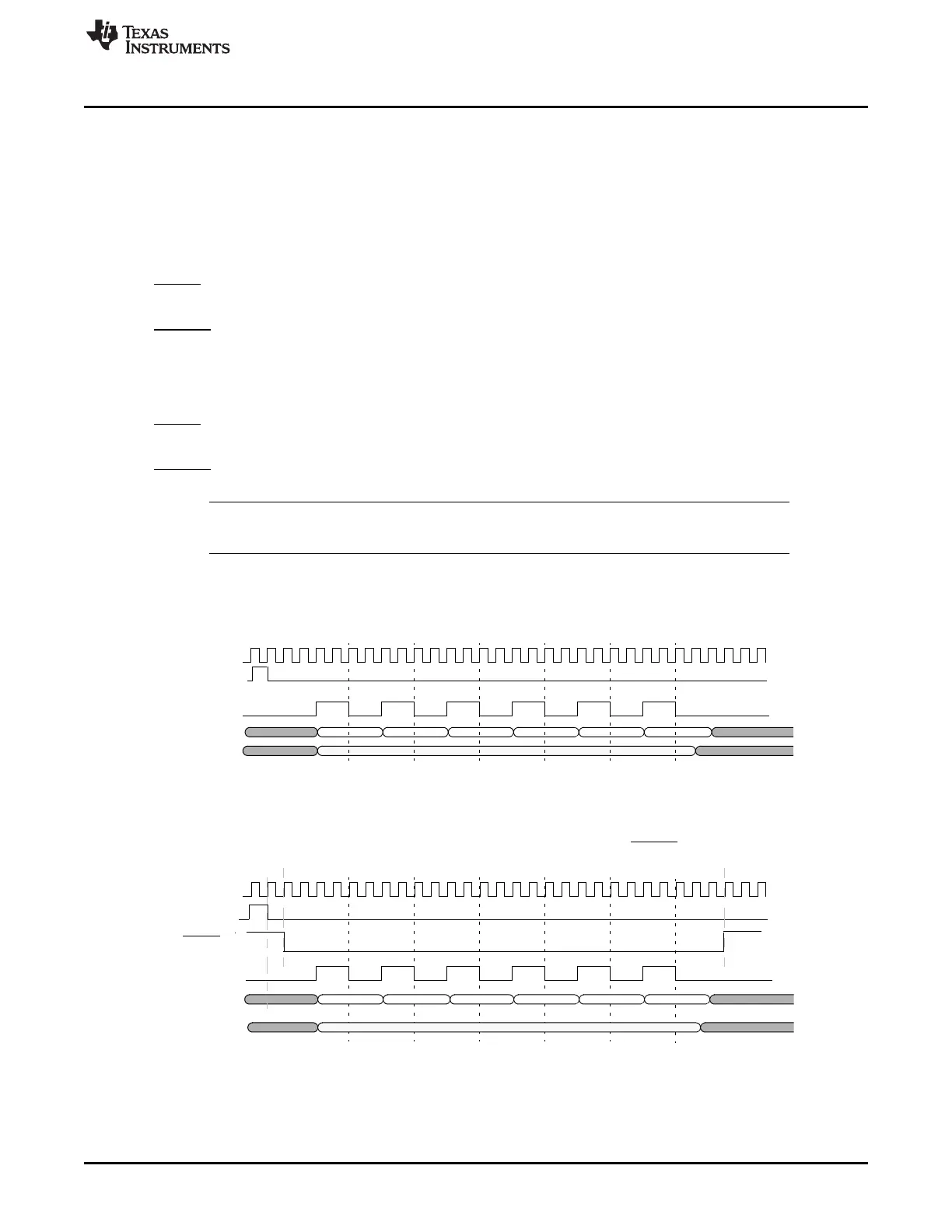

Write to SPIDAT

VCLK

Write to SPIDAT

SPICLK

SPISIMO

SPISOMI

* Dotted vertical lines indicate the receive edges

www.ti.com

MibSPI Pin Timing Parameters

1617

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Multi-Buffered Serial Peripheral Interface Module (MibSPI) with Parallel Pin

Option (MibSPIP)

28.6 MibSPI Pin Timing Parameters

The pin timings of SPI can be classified based on its mode of operation. In each mode, different

configurations like Phase & Polarity affect the pin timings.

The pin directions are based on the mode of operation.

Master mode SPI:

• SPICLK (SPI Clock) - Output

• SPISIMO (SPI Slave In Master Out) - Output

• SPICS (SPI Slave Chip Selects) - Output

• SPISOMI (SPI Slave Out Master In) - Input

• SPIENA (SPI slave ready Enable) - Input

Slave mode SPI:

• SPICLK - Input

• SPISIMO - Input

• SPICS - Input

• SPISOMI - Output

• SPIENA - Output

NOTE: All the following timing diagrams are with Phase = 0 and Polarity = 0, unless explicitly stated

otherwise.

28.6.1 Master Mode Timings for SPI/MibSPI

Figure 28-94. SPI/MibSPI Pins During Master Mode 3-Pin Configuration

Figure 28-95. SPI/MibSPI Pins During Master Mode 4-Pin with SPICS Configuation

Loading...

Loading...