SCI/LIN Control Registers

www.ti.com

1682

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Serial Communication Interface (SCI)/ Local Interconnect Network (LIN)

Module

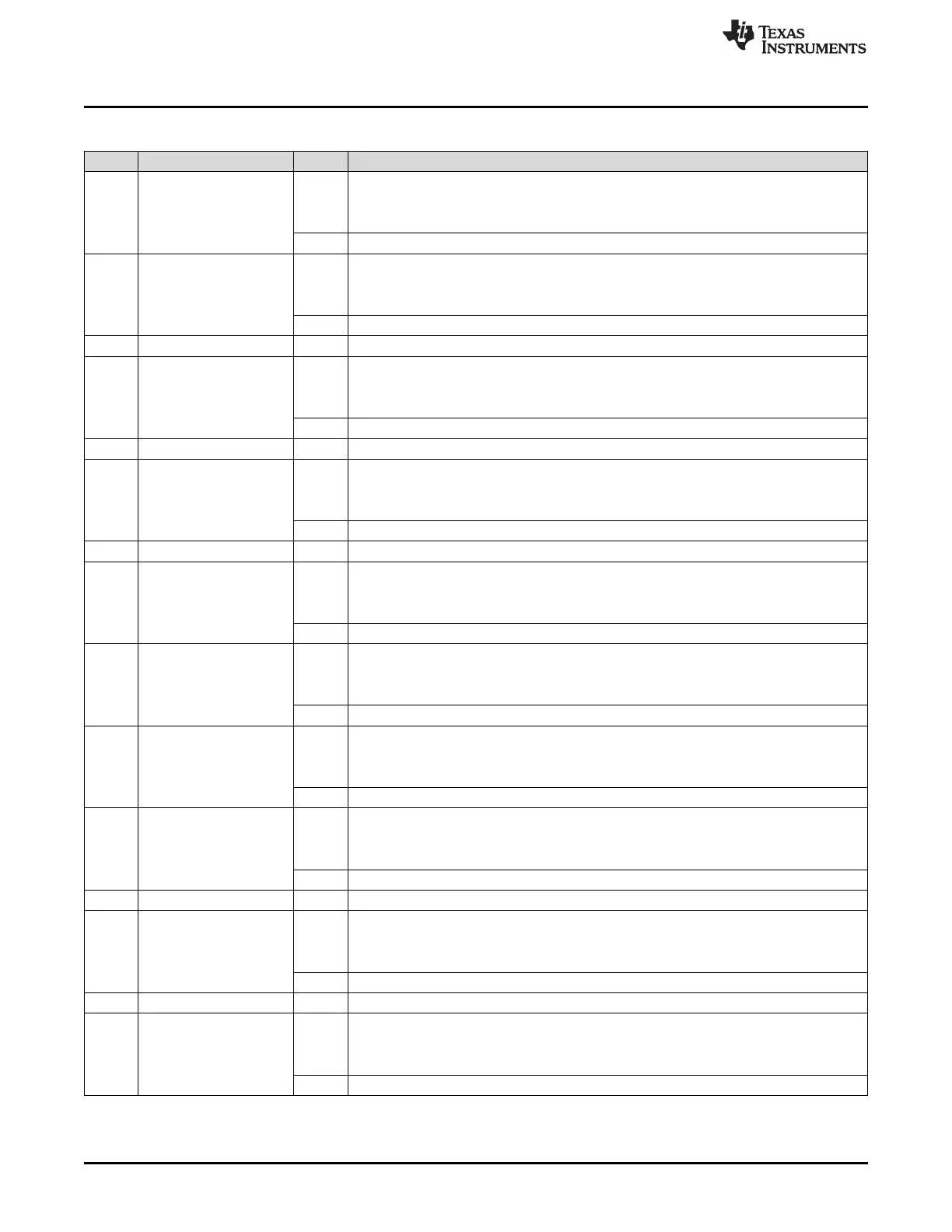

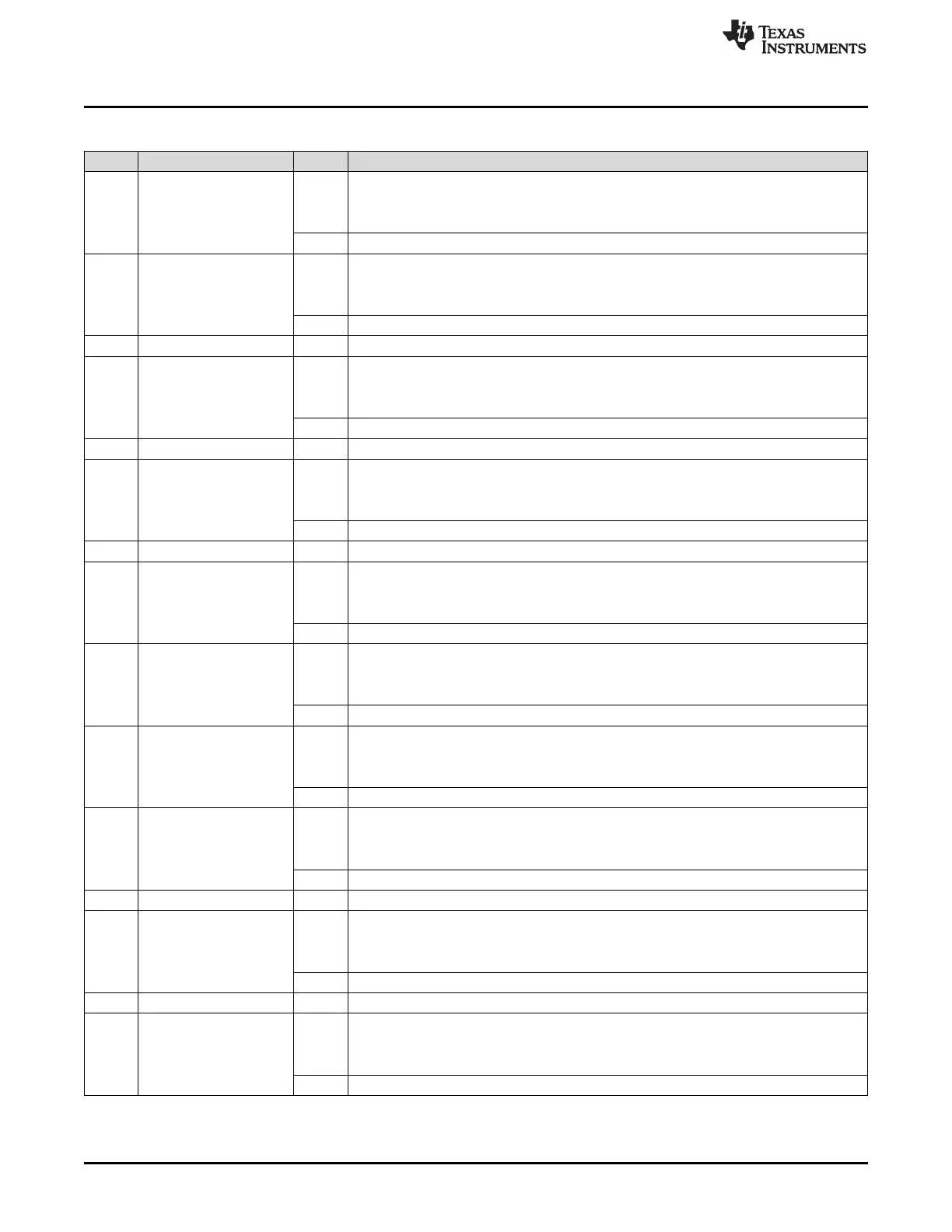

Table 29-18. SCI Set Interrupt Level Register (SCISETINTLVL) Field Descriptions (continued)

Bit Field Value Description

25 SET OE INT LVL Set overrun-error interrupt level. This bit is effective in LIN or SCI-compatible mode.

0 Read: The interrupt level is mapped to the INT0 line.

Write: No effect.

1 Read or write: The interrupt level is mapped to the INT1 line.

24 SET PE INT LVL Set parity error interrupt level. This bit is effective in LIN or SCI-compatible mode.

0 Read: The interrupt level is mapped to the INT0 line.

Write: No effect.

1 Read or write: The interrupt level is mapped to the INT1 line.

23-19 Reserved 0 Reads return 0. Writes have no effect.

18 SET RX DMA ALL LVL Set receive DMA all interrupt levels. This bit is effective in SCI mode only.

0 Read:The receive interrupt request for address frames is mapped to the INT0 line.

Write: No effect.

1 Read or write: The receive interrupt request for address frames is mapped to the INT1 line.

17-14 Reserved 0 Reads return 0. Writes have no effect.

13 SET ID INT LVL Set ID interrupt level. This bit is effective in LIN mode only.

0 Read: The interrupt level is mapped to the INT0 line.

Write: No effect.

1 Read or write: The interrupt level is mapped to the INT1 line.

12-10 Reserved 0 Reads return 0. Writes have no effect.

9 SET RX INT LVL Set receiver interrupt level. This bit is effective in LIN or SCI-compatible mode.

0 Read: The interrupt level is mapped to the INT0 line.

Write: No effect.

1 Read or write: The interrupt level is mapped to the INT1 line.

8 SET TX INT LVL Set transmitter interrupt level. This bit is effective in LIN or SCI-compatible mode.

0 Read: The interrupt level is mapped to the INT0 line.

Write: No effect.

1 Read or write: The interrupt level is mapped to the INT1 line.

7 SET TOA3WUS INT LVL Set timeout after three wakeup signals interrupt level. This bit is effective in LIN mode only.

0 Read: The interrupt level is mapped to the INT0 line.

Write: No effect.

1 Read or write: The interrupt level is mapped to the INT1 line.

6 SET TOAWUS INT LVL Set timeout after wakeup signal interrupt level. This bit is effective in LIN mode only.

0 Read: The interrupt level is mapped to the INT0 line.

Write: No effect.

1 Read or write: The interrupt level is mapped to the INT1 line.

5 Reserved 0 Reads return 0. Writes have no effect.

4 SET TIMEOUT INT LVL Set timeout interrupt level. This bit is effective in LIN mode only.

0 Read: The interrupt level is mapped to the INT0 line.

Write: No effect.

1 Read or write: The interrupt level is mapped to the INT1 line.

3-2 Reserved 0 Reads return 0. Writes have no effect.

1 SET WAKEUP INT LVL Set wake-up interrupt level. This bit is effective in LIN or SCI-compatible mode.

0 Read: The interrupt level is mapped to the INT0 line.

Write: No effect.

1 Read or write: The interrupt level is mapped to the INT1 line.

Loading...

Loading...