SCI/LIN Control Registers

www.ti.com

1716

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Serial Communication Interface (SCI)/ Local Interconnect Network (LIN)

Module

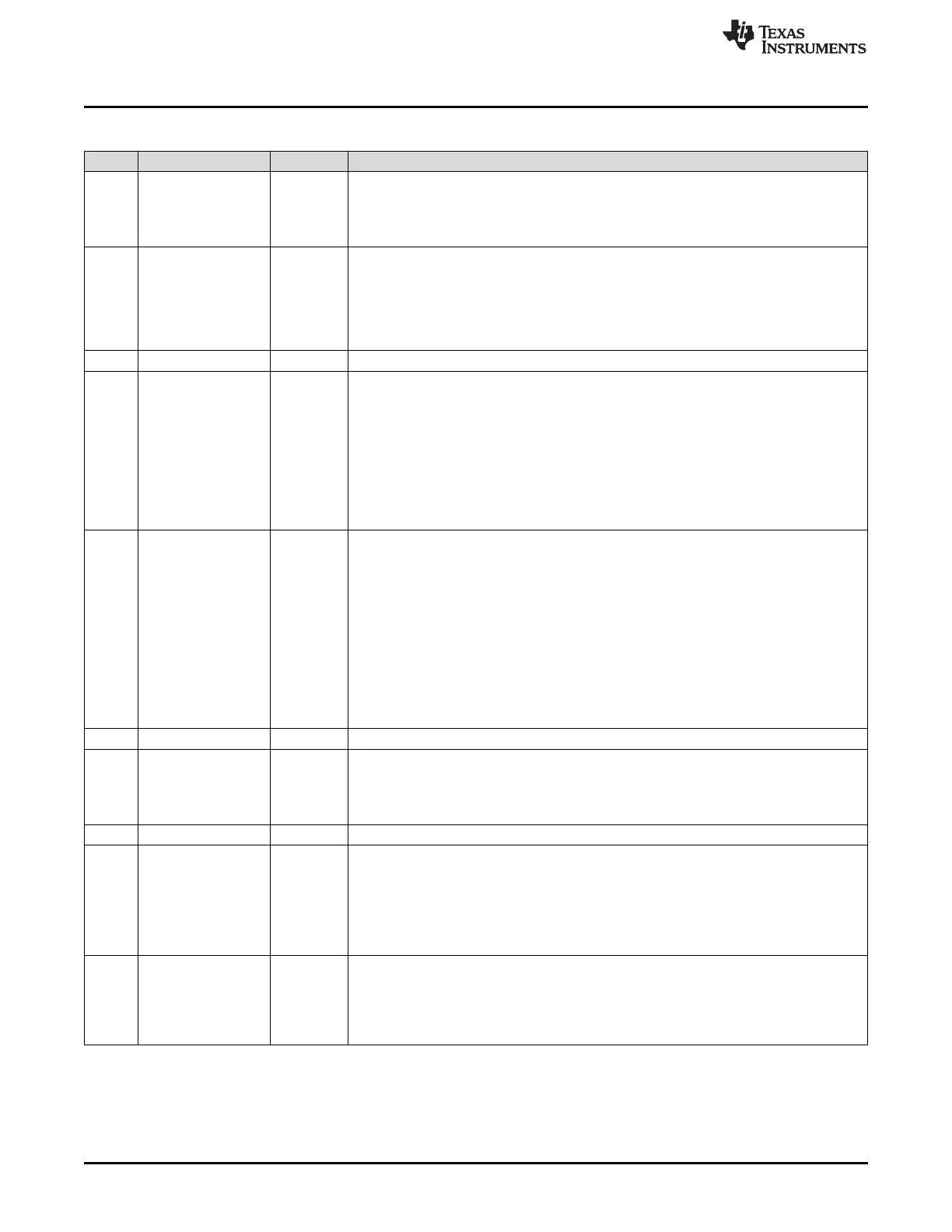

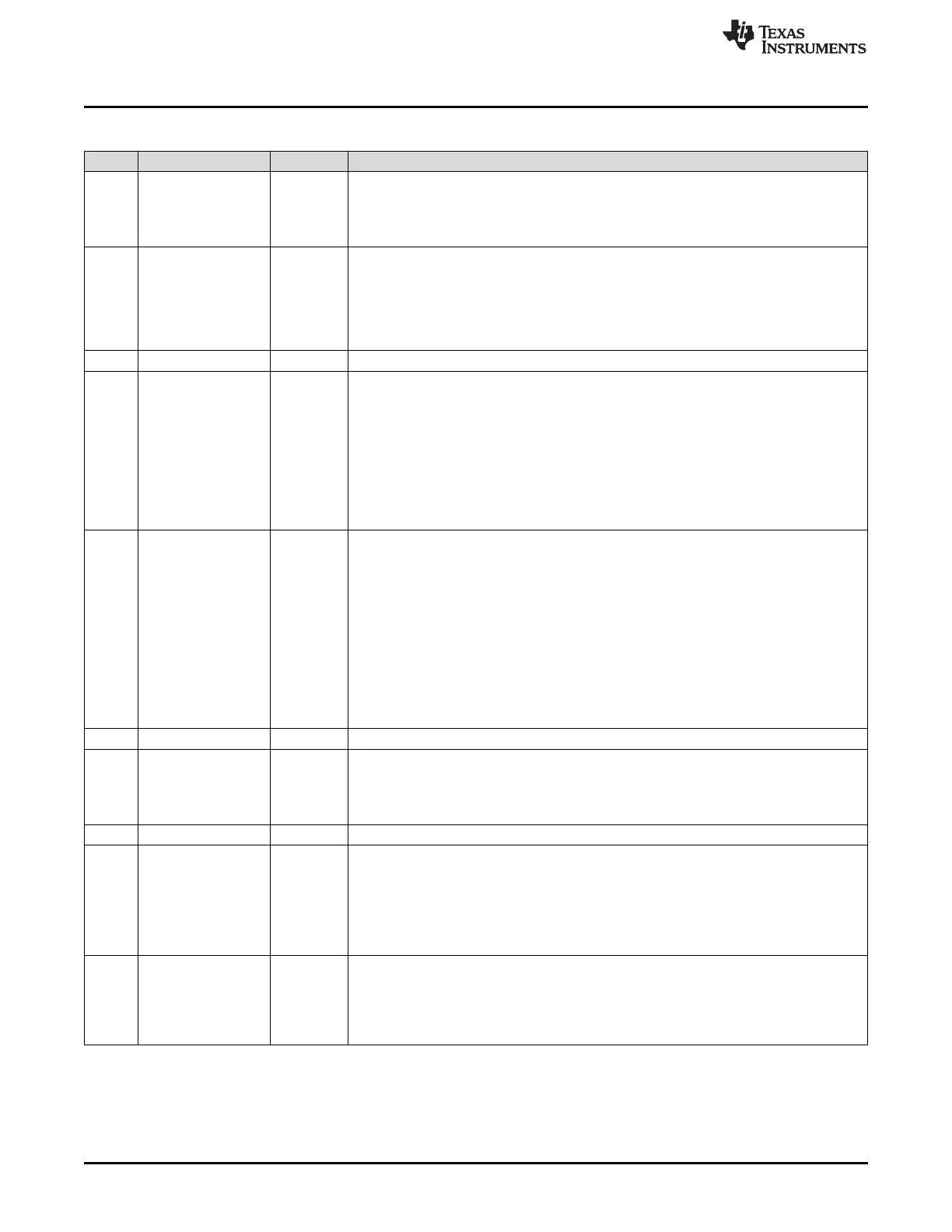

Table 29-48. Input/Output Error Enable Register (IODFTCTRL) Field Descriptions (continued)

Bit Field Value Description

25 PEN Parity error enable. This bit is effective in SCI-compatible mode only. This bit is used to

create a parity error.

0 No parity error occurs.

1 The parity bit received is toggled so that a parity error occurs.

24 BRKDT ENA Break detect error enable. This bit is effective in SCI-compatible mode only. This bit is used

to create a BRKDT error.

0 No error is created.

1 The stop bit of the frame is ANDed with 0 and passed to the RSM so that a frame error

occurs. Then the RX pin is forced to continuous low for 10 T

bit

so that a BRKDT error

occurs.

32-21 Reserved 0 Reads return 0. Writes have no effect.

20-19 PIN SAMPLE MASK Pin sample mask. These bits define the sample number at which the TX pin value that is

being transmitted will be inverted to verify the receive pin samples majority detection

circuitry.

Note: In IODFT mode testing for pin_sample mask must be done with prescalar P

programmed greater than 2 (P > 2).

0 No mask is used.

1h Invert the TX Pin value at TBIT_CENTER.

2h Invert the TX Pin value at TBIT_CENTER + SCLK.

3h Invert the TX Pin value at TBIT_CENTER + 2 SCLK.

18-16 TX SHIFT Transmit shift. These bits define the amount by which the value on TX pin is delayed so that

the value on the RX pin is asynchronous. This feature is not applicable to the start bit.

0 No delay occurs.

1h The value is delayed by 1 SCLK.

2h The value is delayed by 2 SCLK.

3h The value is delayed by 3 SCLK.

4h The value is delayed by 4 SCLK.

5h The value is delayed by 5 SCLK.

6h The value is delayed by 6 SCLK.

7h The value is delayed by 7 SCLK.

15-12 Reserved 0 Reads return 0. Writes have no effect.

11-8 IODFTENA IODFT enable key. Write access permitted in Privilege mode only.

Ah IODFT is enabled.

All other

values

IODFT is disabled.

7-2 Reserved 0 Reads return 0. Writes have no effect.

1 LPB ENA Module loopback enable. Write access permitted in Privilege mode only.

Note: In analog loopback mode the complete communication path through the I/Os

can be tested, whereas in digital loopback mode the I/O buffers are excluded from

this path.

0 Digital loopback is enabled.

1 Analog loopback is enabled in module I/O DFT mode when IODFTENA = 1010.

0 RXP ENA Module analog loopback through receive pin enable. Write access permitted in Privilege

mode only. This bit defines whether the I/O buffers for the transmit or the receive pin are

included in the communication path (in analog loopback mode).

0 Analog loopback through the transmit pin is enabled.

1 Analog loopback through the receive pin is enabled.

Loading...

Loading...