SCI Control Registers

www.ti.com

1736

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Serial Communication Interface (SCI) Module

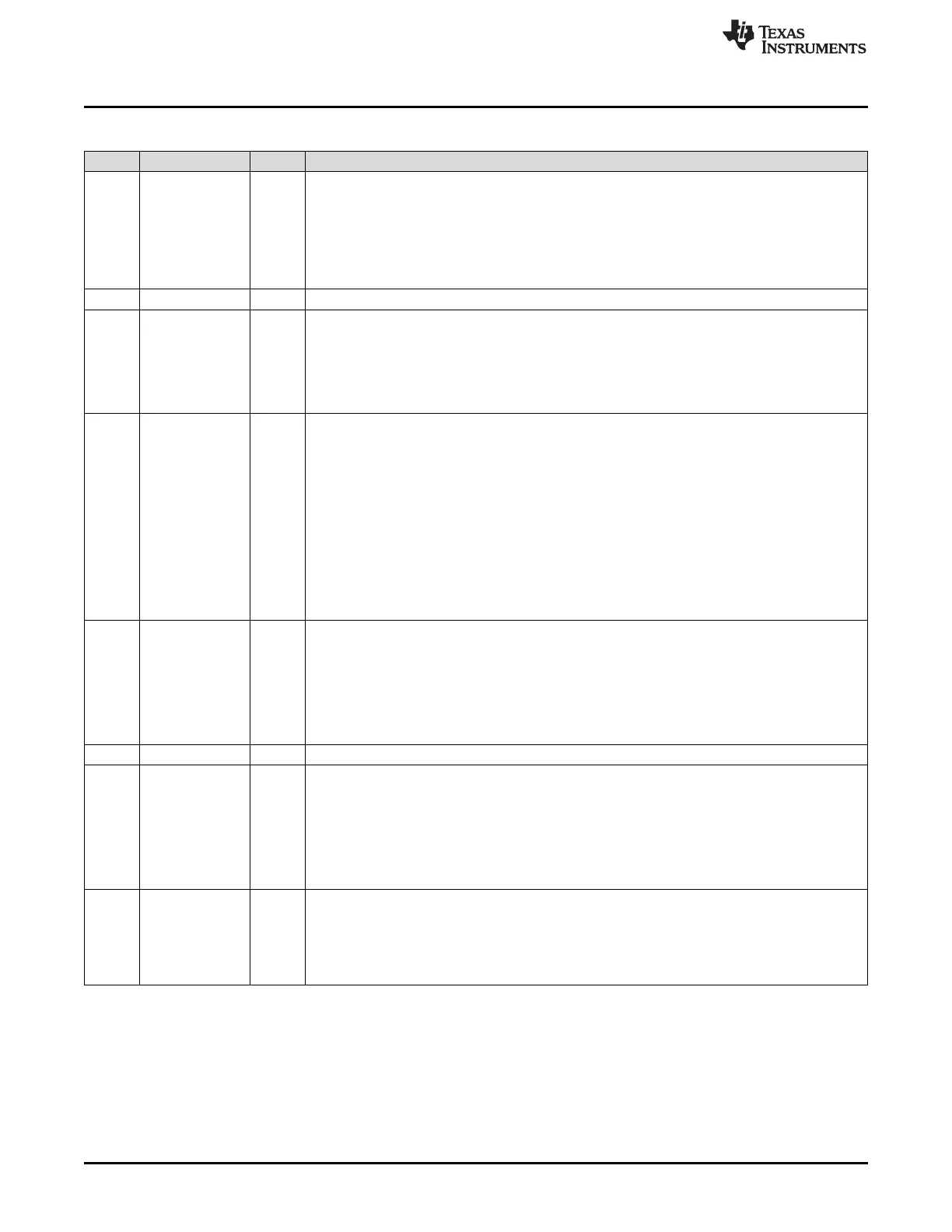

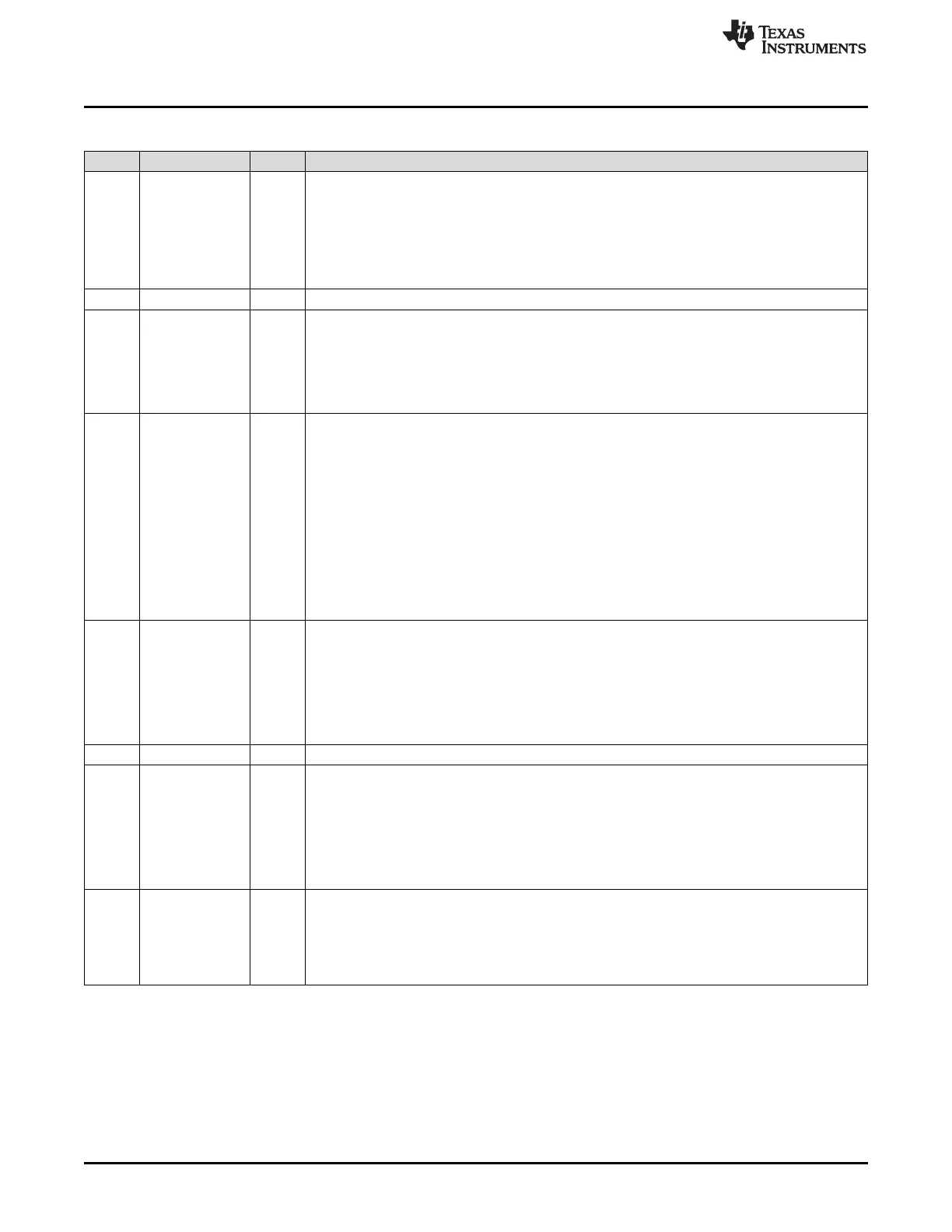

Table 30-5. SCI Global Control Register 1 (SCIGCR1) Field Descriptions (continued)

Bit Field Value Description

16 LOOP BACK Loopback bit. The self-checking option for the SCI can be selected with this bit. If the SCITX and

SCIRX pins are configured with SCI functionality, then the SCITX pin is internally connected to the

SCIRX pin. Externally, during loop back operation, the SCITX pin outputs a high value and the

SCIRX pin is in a high-impedance state. If this bit value is changed while the SCI is transmitting or

receiving data, errors may result.

0 Loop back mode is disabled.

1 Loop back mode is enabled.

15-10 Reserved 0 Reads return 0. Writes have no effect.

9 POWERDOWN Power down. When the POWERDOWN bit is set, the SCI attempts to enter local low-power mode.

If the POWERDOWN bit is set while the receiver is actively receiving data and the wake-up

interrupt is enabled, then the SCI immediately asserts an error interrupt to prevent low-power mode

from being entered. Only Privilege mode writes allowed.

0 Normal operation.

1 Low-power mode is enabled.

8 SLEEP SCI sleep. In a multiprocessor configuration, this bit controls the receive sleep function. Clearing

this bit brings the SCI out of sleep mode.

0 Sleep mode is disabled.

1 Sleep mode is enabled.

Note: The receiver still operates when the SLEEP bit is set; however, RXRDY is updated and

SCIRD is loaded with new data only when an address frame is detected. The remaining

receiver status flags are updated and an error interrupt is requested if the corresponding

interrupt enable bit is set, regardless of the value of the SLEEP bit. In this way, if an error is

detected on the receive data line while the SCI is asleep, software can promptly deal with the

error condition.

Note: The SLEEP bit is not automatically cleared when an address byte is detected.

See Section 30.6.1 for more information on using the SLEEP bit for multiprocessor communication.

7 SWnRST Software reset (active low). This bit is effective in LIN and SCI modes.

0 The SCI is in its reset state; no data will be transmitted or received. Writing a 0 to this bit initializes

the SCI state machines and operating flags as defined in Table 30-11 and Table 30-12. All affected

logic is held in the reset state until a 1 is written to this bit.

1 The SCI is in its ready state; transmission and reception can be done. After this bit is set to 1, the

configuration of the module should not change.

Note: The SCI should only be configured while SWnRST = 0.

6 Reserved 0 Reads return 0. Writes have no effect.

5 CLOCK SCI internal clock enable. The CLOCK bit determines the source of the module clock on the

SCICLK pin.

0 The external SCICLK is the clock source.

1 The internal SCICLK is the clock source.

Note: If an external clock is selected, then the internal baud rate generator and baud rate

registers are bypassed. The maximum frequency allowed for an externally sourced SCI clock

is VCLK/16.

4 STOP SCI number of stop bits per frame.

0 One stop bit is used.

1 Two stop bits are used.

Note: The receiver checks for only one stop bit. However in idle-line mode, the receiver

waits until the end of the second stop bit (if STOP = 1) to begin checking for an idle period.

Loading...

Loading...