System and Peripheral Control Registers

www.ti.com

184

SPNU563A–March 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

Architecture

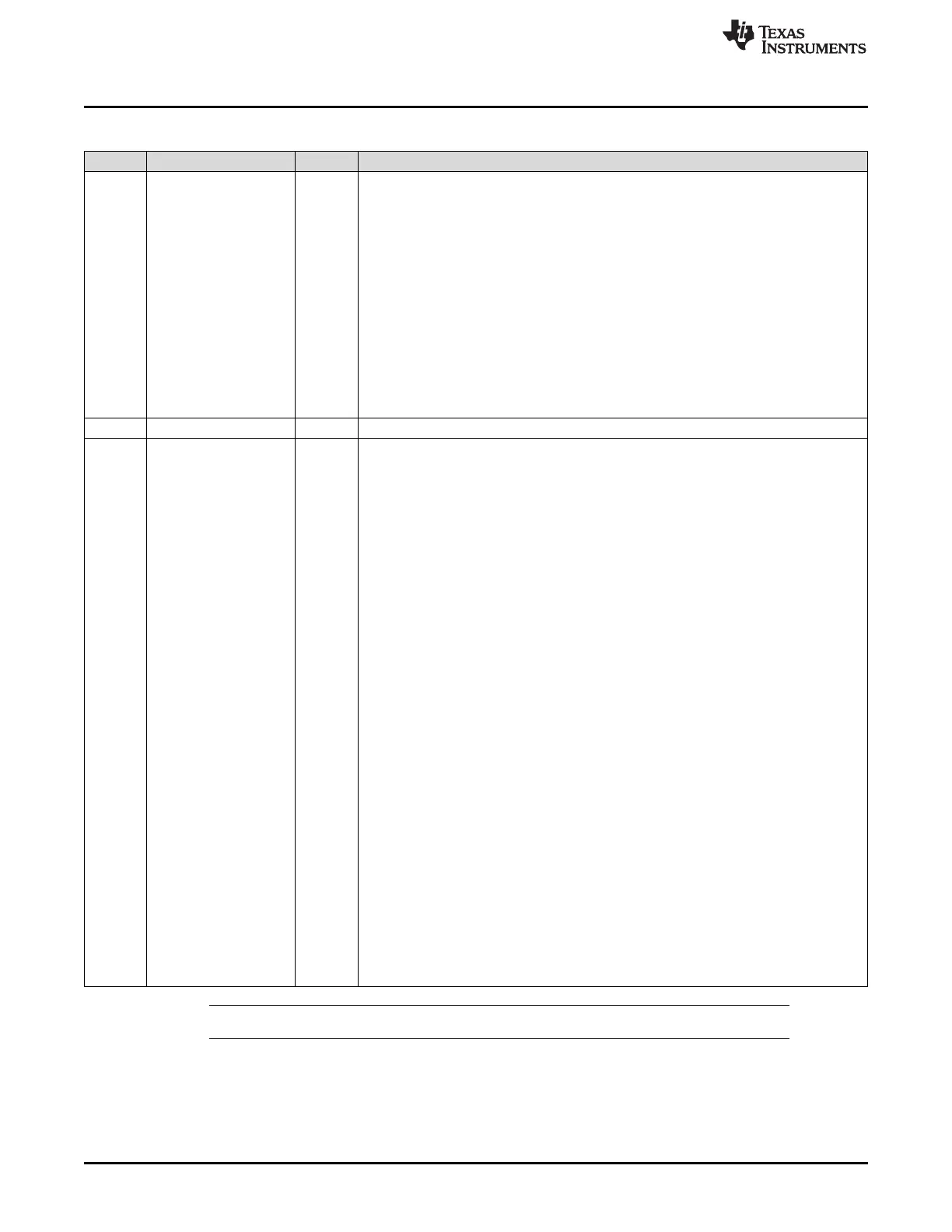

Table 2-50. Clock Test Register (CLKTEST) Field Descriptions (continued)

Bit Field Value Description

11-8 SEL_GIO_PIN GIOB[0] pin clock source valid, clock source select

0 Oscillator valid status

1h PLL1 valid status

2h-4h Reserved

5h High-frequency LPO (Low-Power Oscillator) clock output valid status [CLK10M]

6h PLL2 valid status

7h Reserved

8h Low-frequency LPO (Low-Power Oscillator) clock output valid status [CLK80K]

9h-Ch Oscillator valid status

Dh Reserved

Eh VCLKA4

Fh Oscillator valid status

7-5 Reserved 0 Reads return 0. Writes have no effect.

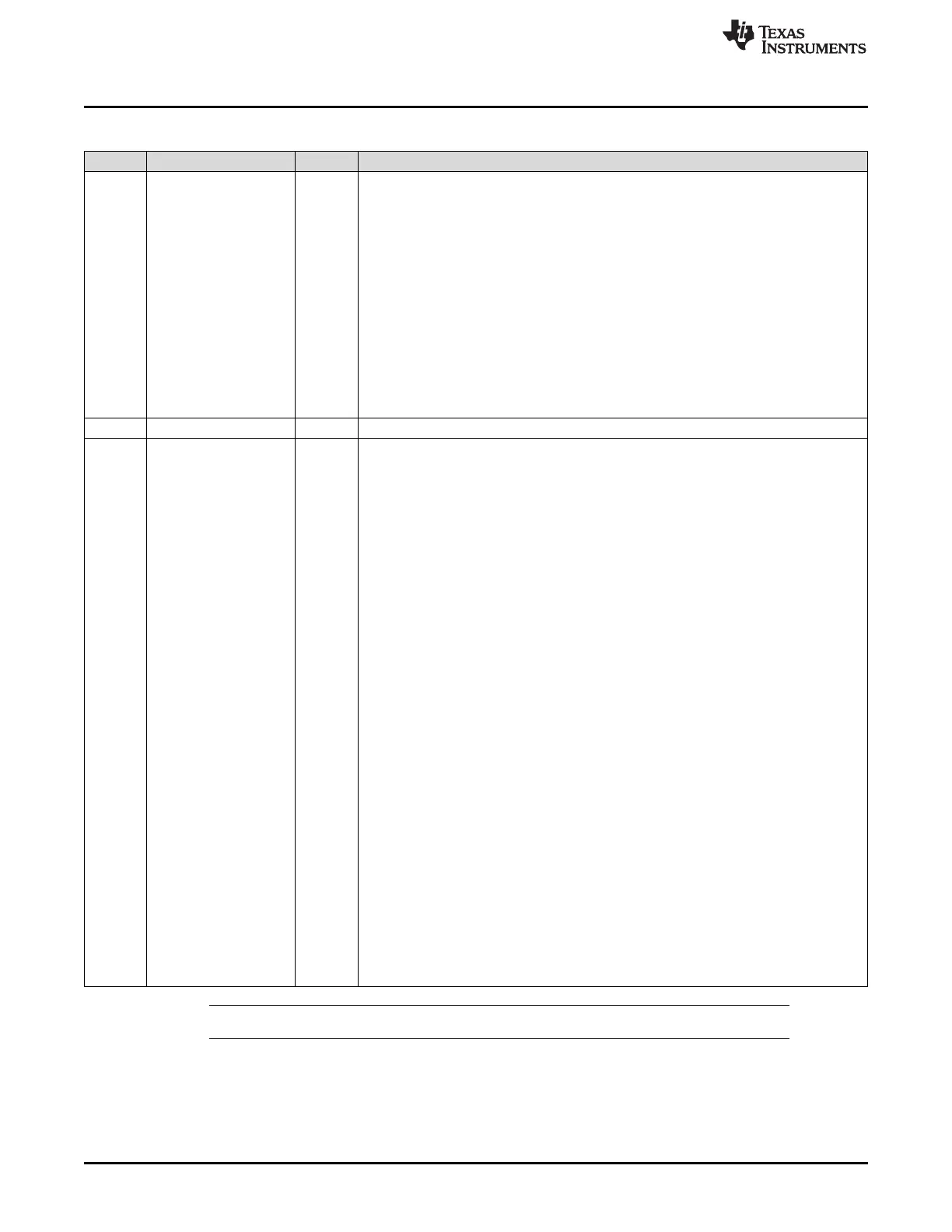

4-0 SEL_ECP_PIN ECLK pin clock source select

Note: Only valid clock sources can be selected for the ECLK pin. Valid clock

sources are displayed by the CSVSTAT register.

0 Oscillator clock

1h PLL1 clock output

2h Reserved

3h EXTCLKIN1

4h Low-frequency LPO (Low-Power Oscillator) clock [CLK80K]

5h High-frequency LPO (Low-Power Oscillator) clock [CLK10M]

6h PLL2 clock output

7h EXTCLKIN2

8h GCLK1

9h RTI1 Base

Ah Reserved

Bh VCLKA1

Ch VCLKA2

Dh Reserved

Eh VCLKA4_DIVR

Fh Flash HD Pump Oscillator

10h Reserved

11h HCLK

12h VCLK

13h VCLK2

14h VCLK3

15h-16h Reserved

17h EMAC clock output

18h-1Fh Reserved

NOTE: Non-implemented clock sources should not be enabled or used.

Loading...

Loading...